## Upgrade of the HADES RICH photon detector with H12700 MAPMTs

C. Pauly, M. Faul, J. Friese, C. Höhne, K.-H. Kampert, T. Kunz, S. Lebedev, J. Michel, W. Niebur, V. Patel, P. Skott, M. Traxler, A. Weber, and the TRB collaboration

### contact: pauly@physik.uni-wuppertal.de

# Overview

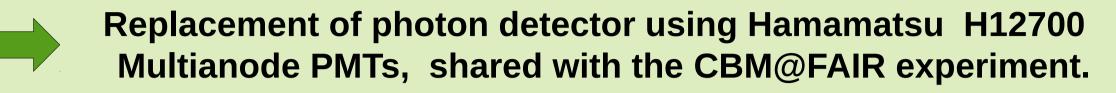

- The HADES RICH [1] is a hadron blind RICH detector with  $C_4F_{10}$  radiator, thin carbon mirror, and CsI+MWPC photon detector

- Sensitive in VUV range, 145nm 220 nm.

- Designed for  $e^{\pm}$  identification 15 MeV/c < p < 1.5 GeV/c.

- Successfully operated since 1999 at SIS18, GSI, Germany. Operation will continue first at SIS18, later (2020+) at SIS100@FAIR.

- CsI photon detector is showing first signs of aging. Insufficient for reliable future operation in high multiplicity Au+Au collisions at FAIR.

• 428 MAPMTs, 64ch each,  $\sim$ 27k readout pixels in total, each  $\sim$ 6x6 mm<sup>2</sup>. 1.2 m<sup>2</sup> active area, optical range: 200nm – 600nm.

- High efficiency (>30% q.e.), high rate, radiation hard. Time resolution ~300ps (TTS), low dark rate (<5 kHz per PMT).

- PMTs are being delivered and tested right now ( $\rightarrow$  see Poster B4).

- Common HADES/CBM development of readout electronics and reconstruction software.

- Significant gain in detector performance expected, in particular  $e^{\pm}$  pair reconstruction efficiency at small opening angles.

- Start of operation is planed for 2018.

Sketch of the new HADES RICH detector, with the MAPMT plane and readout modules replacing the old CsI+MWPC photon detector. The inner part of the detection plane is shifted by 10cm to accommodate for the curved focal plane. The original CaF<sub>2</sub> window is kept to separate the radiator ( $C_4F_{10}$ ) from the photodetector volume ( $N_2$ ).

# Simulations

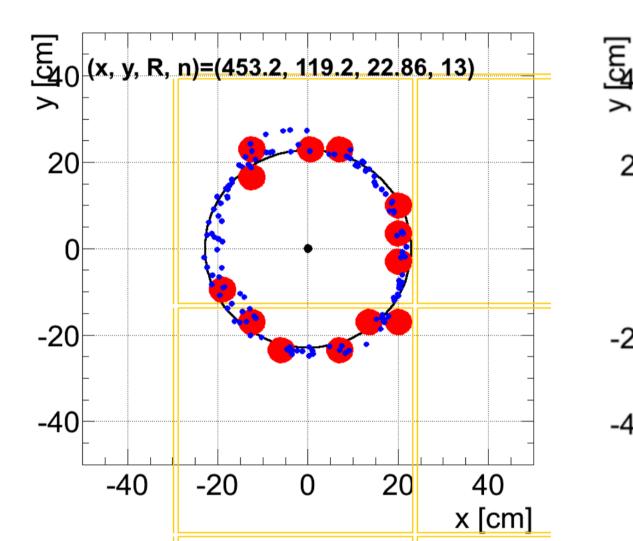

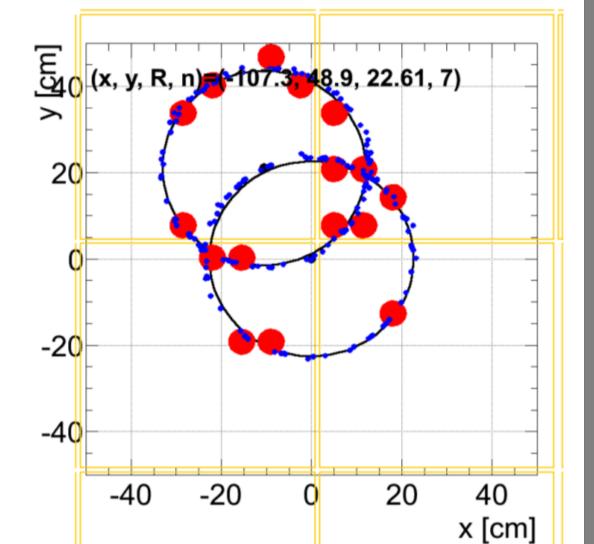

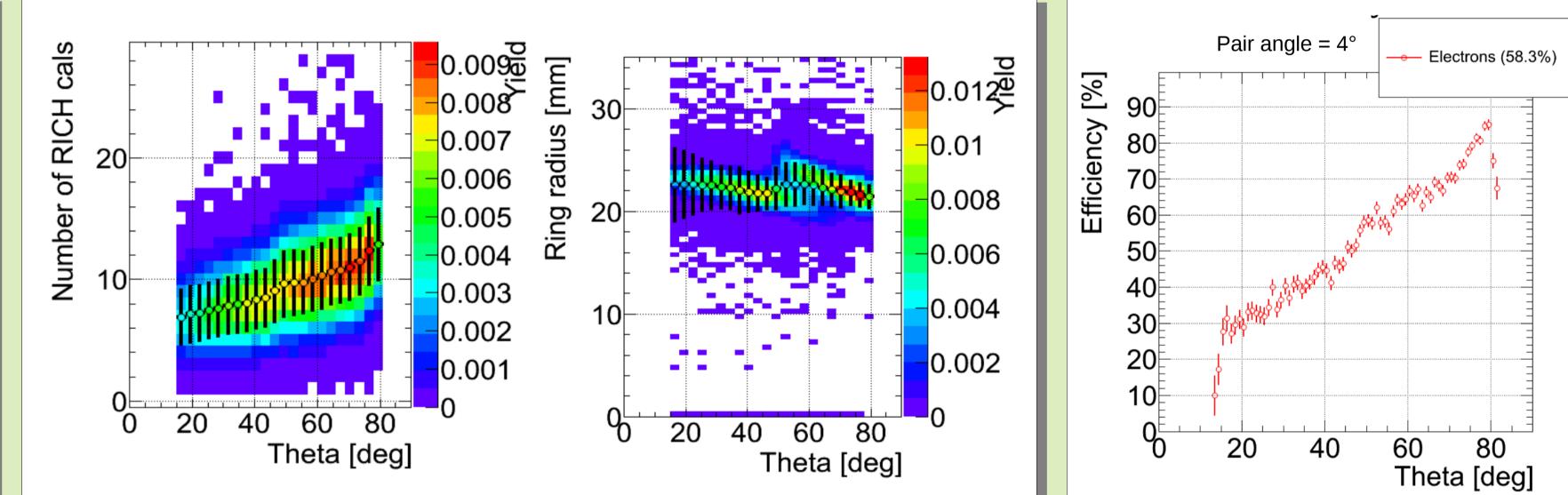

Realistic Monte Carlo simulations of the upgraded HADES RICH detector within the HYDRA simulation framework have been carried out to optimize the design and estimate the expected performance. Shown here are typical electron and e<sup>+</sup>/e<sup>-</sup>-pair ring images, taking into account measured spectral quantum efficiency courves, and a moderate collection efficiency of 70%. Blue dots: photons hitting the PM. Red points: registered photons. Circles show fully reconstructed rings, PMT boundaries indicated in yellow.

Between 7 and 15 detected photons per Cherenkov ring in average are expected, depending on  $e^{\pm}$  polar emission angle. The photon yield increases towards the outside due to the longer optical path length in the radiator.

The Cherenkov rings with a radius of about 22mm cover roughly the size of a single 8x8 pixel MAPMT. The change in radius at  $\theta \sim 50^{\circ}$  is caused by the displaced inner part of the detection plane, and can well coped for by the ring finding- and reconstruction routines.

The reconstruction efficiency for close e<sup>+</sup>e<sup>-</sup> pairs, shown here for an e<sup>+</sup>e<sup>-</sup> opening angle of 4°, will drastically be improved by the upgrade. This will significantly boost the overall reconstruction efficiency for collision events with e+/e- pair content, a key feature for the future HADES physics program.

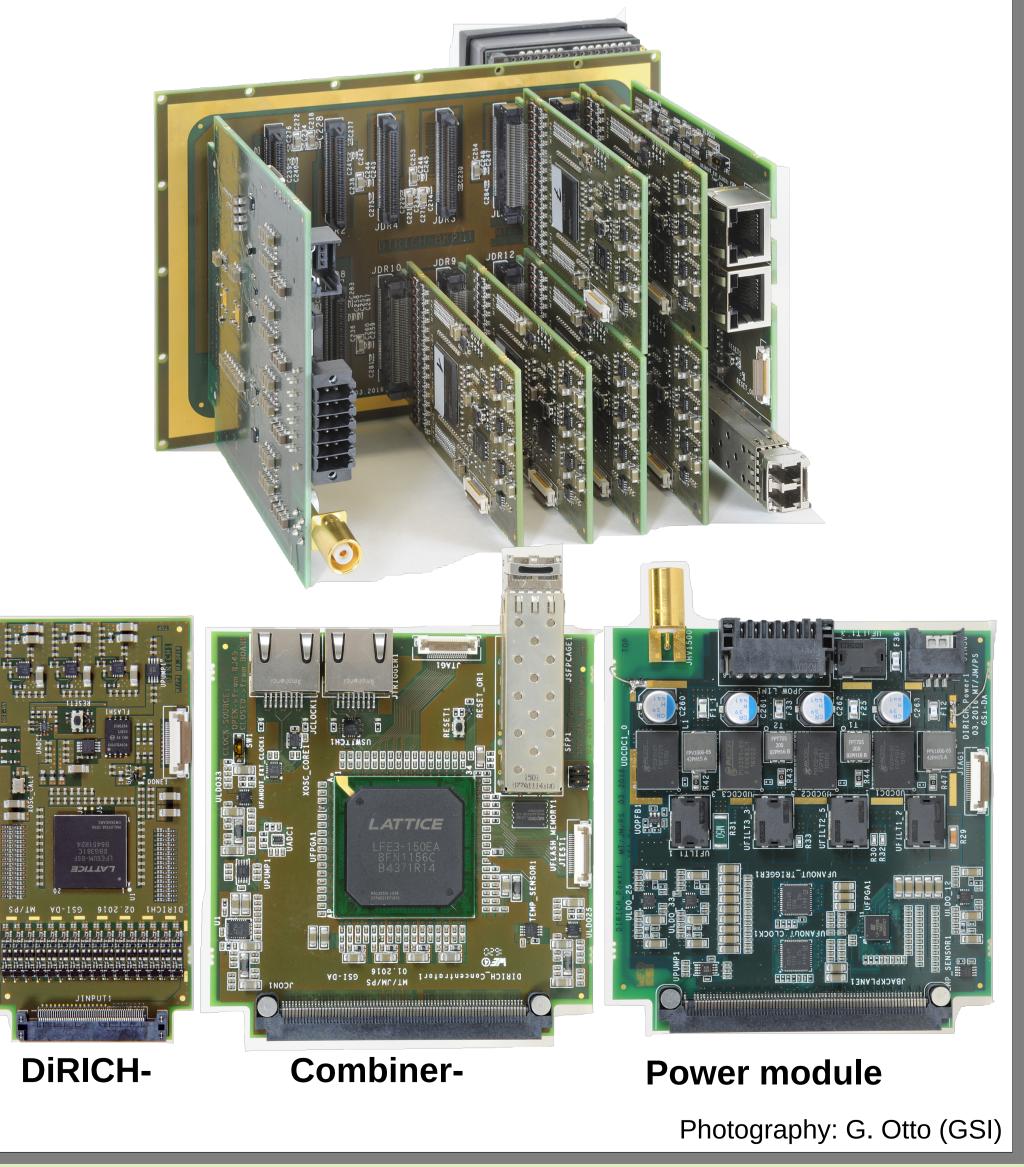

## **FPGA-TDC** readout chain

- Highly integrated FPGA-based readout chain for both HADES- and CBM RICH.

- Based on TRB / PADIWA FPGA-TDC development [2].

- Individual 3x2 MAPMT readout modules, mounted to aluminum carrier frame structure

- All interconnections between PMTs and readout modules via module backplane, serving also as light- and gas-tight seal.

- Modular design, low power, air cooling (approx. 2 kW in total).

### **DiRICH frontend module:**

- 32ch amplification, discrimination, digitization (FPGA-TDC)

- Low-power analog shaping amplifier (1.1V, 12mW / channel)

- All analog inputs galvanically decoupled.

- Discrimination using LVDS input comparators on the FPGA (Lattice ECP5).

- High sensitivity, <1mV minimum input threshold.

- Individual channel thresholds (Delta-Sigma DACs on FPGA)

- FPGA-TDC high precision time measurement, ( $\Delta T < 20$ ps RMS).

- Leading + trailing edge measurement, amplitude via ToT.

- High rate capability: >200 kHz per each channel.

- for CBM: Self-triggered, free-streaming operation.

### **Combiner module:**

- Combine data of up to 12 DiRICH to single 2 GBit/s output link.

- Inputs for ext. clock and reference time, distributed via backplane.

#### **Power module:**

- Centralized power supply for complete 3x2 readout module.

- High-Voltage connection, shared by all 6 PMTs.

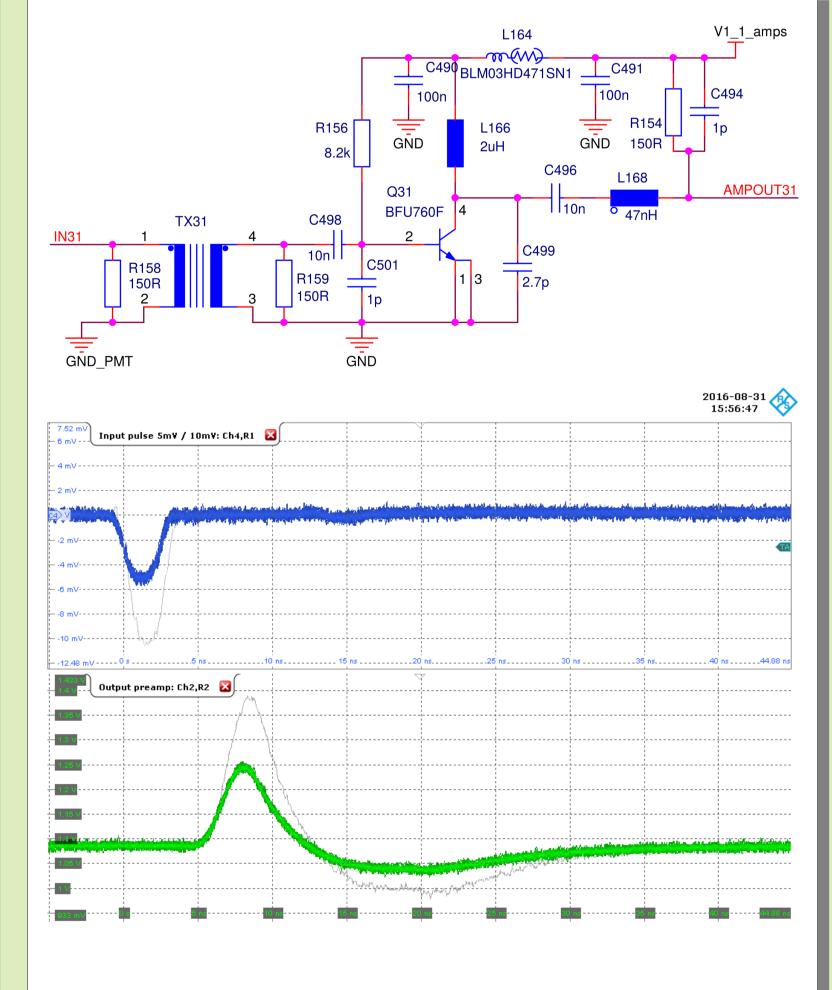

Typical signal response (green) of the DiRICH analog input amplifier for PMT-like input signals (blue) of 5 / 10 mV, 2.5ns width. The amplitude gain is  $\sim$ 32.

### [1] G. Agakichiev et al., EPJ A41, 243-277 (2009) [2] M. Traxler et al., JINST 6 12004 (2011) supported by BMBF grant 05P15PXFCA, and GSI