# Readout of straws for PANDA

#### **Dr Grzegorz Korcyl**

Department of Information Technologies

Jagiellonian University, Cracow

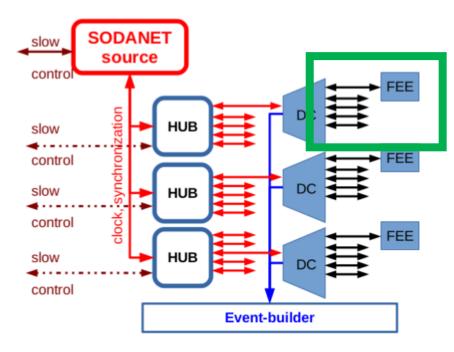

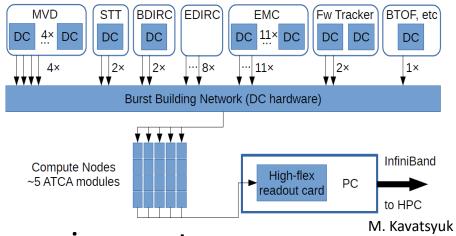

#### PANDA readout concept

- Subsystems (7) have specific FEE

- All FEEs from a subsystem are connected to unified Data Concentrators

- DCs are gateways for:

- Slow control

- Readout data to storage

- Time synchronisation

M. Kavatsyuk

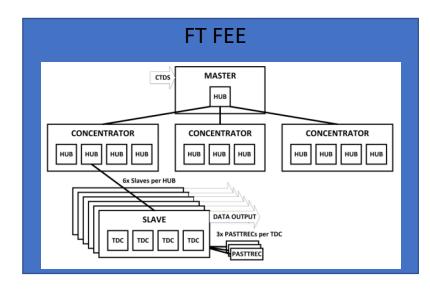

#### Forward Tracker subsystem

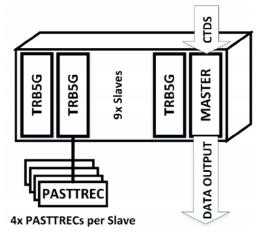

- Complete system based on PASTTRECs and TRBv3

- Tested and verified under multiple experiments

- Recent deployment for HADES

- System suitable for PANDA Phase One (1/10 luminosity)

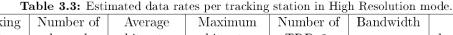

| Tracking | Number of | Average               | Maximum                | Number of | Bandwidth          | Total                |

|----------|-----------|-----------------------|------------------------|-----------|--------------------|----------------------|

| station  | channels  | hit rate              | hit rate               | TRBv3s    |                    | bandwidth            |

| FT 1,2   | 2304      | $35~\mathrm{kHits/s}$ | $140~\mathrm{kHits/s}$ | 12        | $81~\mathrm{MB/s}$ | $972~\mathrm{MB/s}$  |

| FT 3,4   | 3328      | $31~\mathrm{kHits/s}$ | $90~\mathrm{kHits/s}$  | 18        | $69~\mathrm{MB/s}$ | $1242~\mathrm{MB/s}$ |

| FT 5,6   | 6592      | $9~\mathrm{kHits/s}$  | $39~\mathrm{kHits/s}$  | 35        | $20~\mathrm{MB/s}$ | $700~\mathrm{MB/s}$  |

Traxler, M.; Korcyl, G.; Bayer, E.; Maier, L.; Michel, J.; Palka, M. "A compact system for high precision time measurements (<14 ps RMS) and integrated acquisition for a large number of channels", JINST 10.1088/1748-0221/6/12/C12004

#### Forward Tracker subsystem

- TRBv3 10 years old

- TDC implementation 5 years old

PANDA is supposed to be operational in 2025

• => refreshment would be welcome

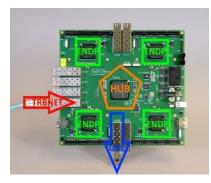

## TRB platform upgrade

- Upgraded hardware

- New form factor

- Custom crate system

- Lattice ECP5

- Addon connector

Trb.gsi.de

| Table 3.4: Estimated data rates per tracking station in High Luminosity mode | Table 3.4: | Estimated | data | rates | per | tracking | station | in | High | Luminosity | mode. |

|------------------------------------------------------------------------------|------------|-----------|------|-------|-----|----------|---------|----|------|------------|-------|

|------------------------------------------------------------------------------|------------|-----------|------|-------|-----|----------|---------|----|------|------------|-------|

| Tracking | Number of | Average                   | Maximum                    | Number of | Bandwidth          | Total                |

|----------|-----------|---------------------------|----------------------------|-----------|--------------------|----------------------|

| station  | channels  | hit rate                  | hit rate                   | TRB5Gs    |                    | bandwidth            |

| FT 1,2   | 2304      | $350~\mathrm{kHits/s}$    | $1400 \; \mathrm{kHits/s}$ | 36        | $90~\mathrm{MB/s}$ | $3240~\mathrm{MB/s}$ |

| FT 3,4   | 3328      | $310 \; \mathrm{kHits/s}$ | 900  kHits/s               | 52        | $79~\mathrm{MB/s}$ | $4108~\mathrm{MB/s}$ |

| FT 5,6   | 6592      | 90 kHits/s                | 390  kHits/s               | 103       | $23~\mathrm{MB/s}$ | $2369~\mathrm{MB/s}$ |

### TRB firmware development

- New FPGA -> possibility for a new TDC

- Lower resolution

- No delay chain oversampling with phase-shiftted clocks

- Higher channel count 4x PASTTREC boards per FPGA

- New data format with lower overhead

- Time sorted hits

- Work in progress cooperation with PK M. Michałek

- Communication features

- Most TrbNet components to be migrated

- Gigabit Ethernet requires fixes

- SodaNet to be migrated

- Connection to Data Concentrator to be developed

### Hardware development

- TRB5 PASTTREC Addon

- Fix pseudo-SPI interface

- Crate controller

- Local data concentrator via backplane

- SodaNet receiver and hub

- Data Concentrator output

- Xilinx FPGA

Trb.gsi.de

#### PANDA complete readout

- Minimum requirement

- Deliver raw data to the Data Concentrators

- Additional module for preprocessing and online tracking

- Between TRB crates and Data Concentrator

#### Intermediate module

- Performs:

- Data aggregation

- Hit sorting

- Clustering

- Filtering

- Tracking

- Prototype developed on ZCU102 platform

- 2x inputs, GbE data streams from TRBv3

- 2x output, GbE and to the Compute Node

- Tested during 2019 Juelich beamtime

- Filtering only, data to be analyzed

- Firmware to be developed

- Possibility to develop the hardware as well

### Work Packages

- TRB5 readout board

- Firmware:

- New TDC implementation

- PASTTREC controller

- Communication infrastructure

- Hardware:

- PASTTREC Addon

- 2. Crate controller

- Firmware:

- Data aggregation

- Hit sorting

- SodaNet

- Data Concentrator link

- Hardware:

- Entire board

- 3. Intermediate board

- Firmware:

- Full online tracking pipeline

- Hardware:

- Design or commercial

- 4. Support and maintenance