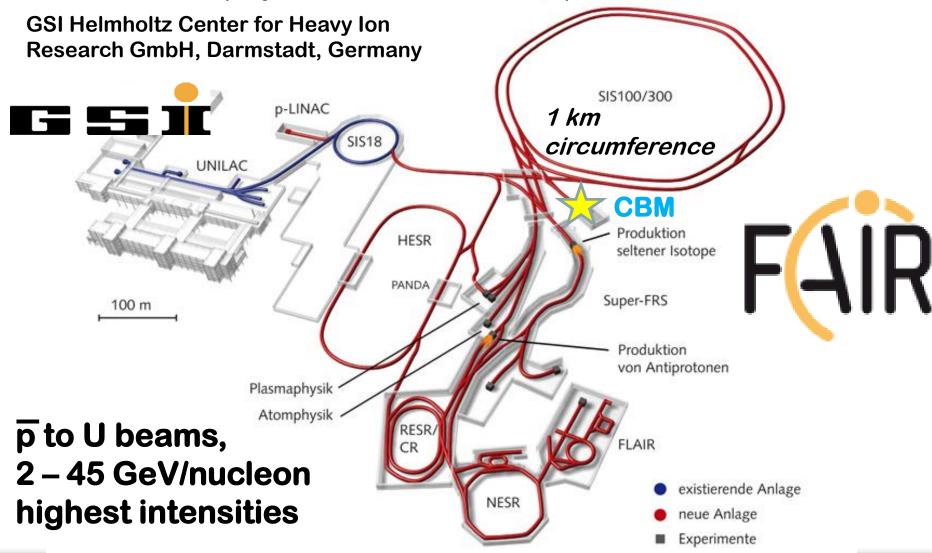

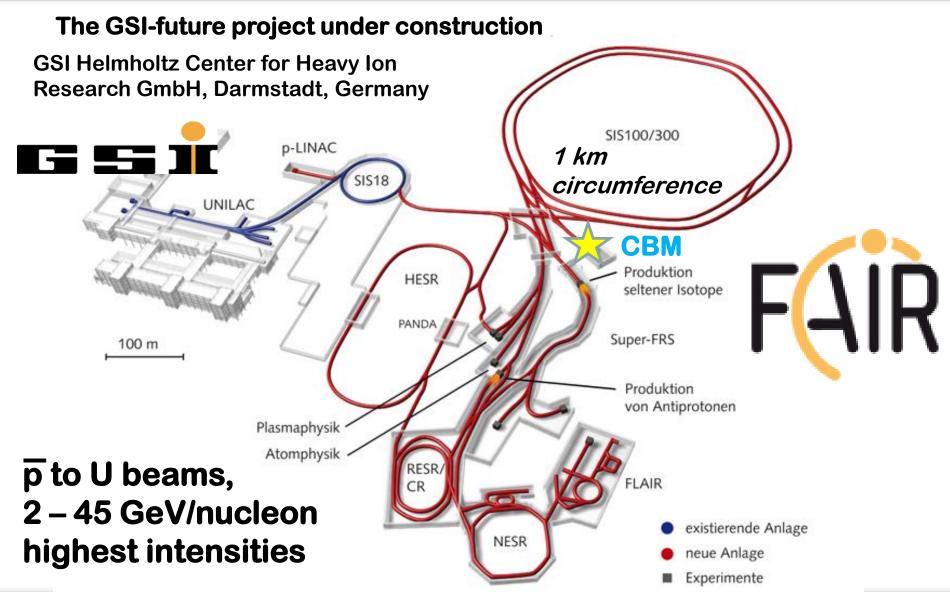

## FAIR Facility for Antiproton and Ion Research

# Particle Tracking Challenges: The CBM Silicon Tracking Station at FAIR

Christian J. Schmidt,

GSI Darmstadt

at Gauhati University, Assam, India

#### FAIR - Facility for Anti-Proton and Ion Research, Darmstadt

The GSI-future project under construction, operative in 2024

#### FAIR - Facility for Anti-Proton and Ion Research, Darmstadt

#### FAIR - Facility for Anti-Proton and Ion Research, Darmstadt

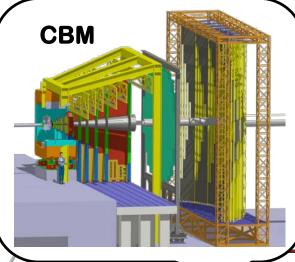

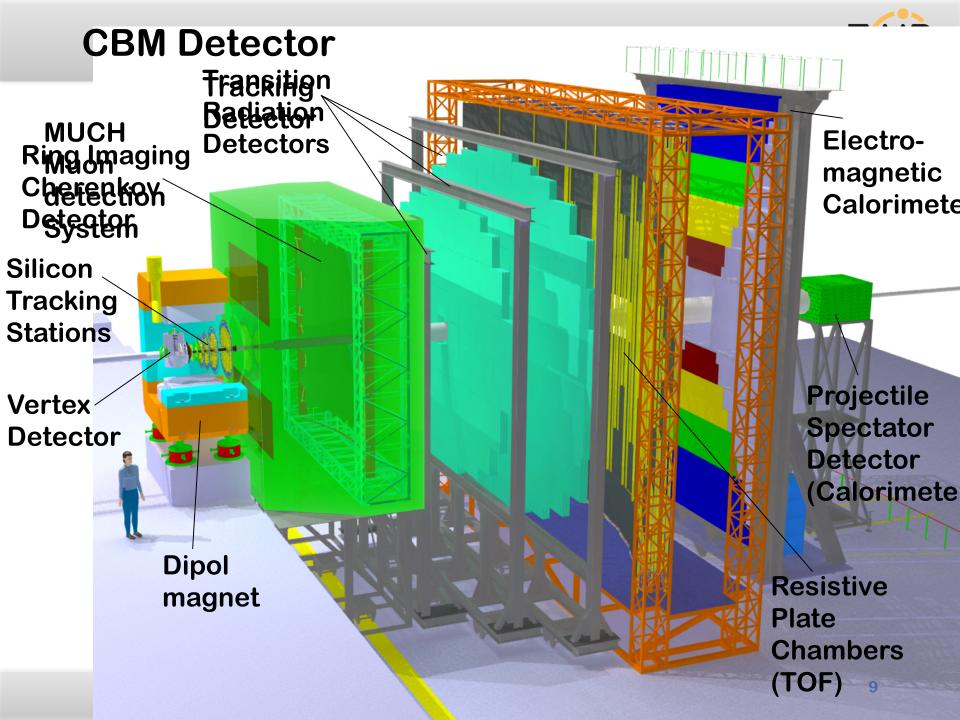

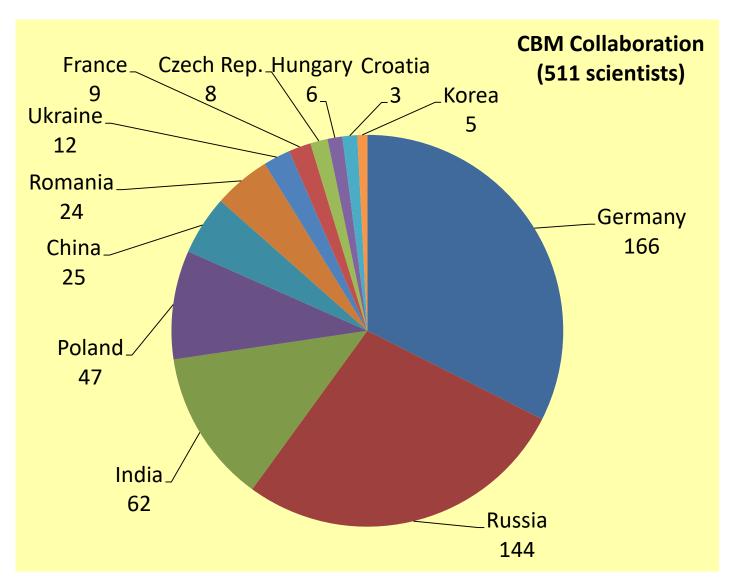

#### **CBM**

About 500 members

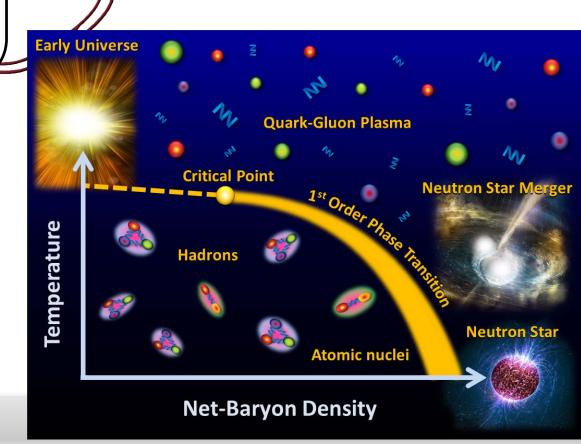

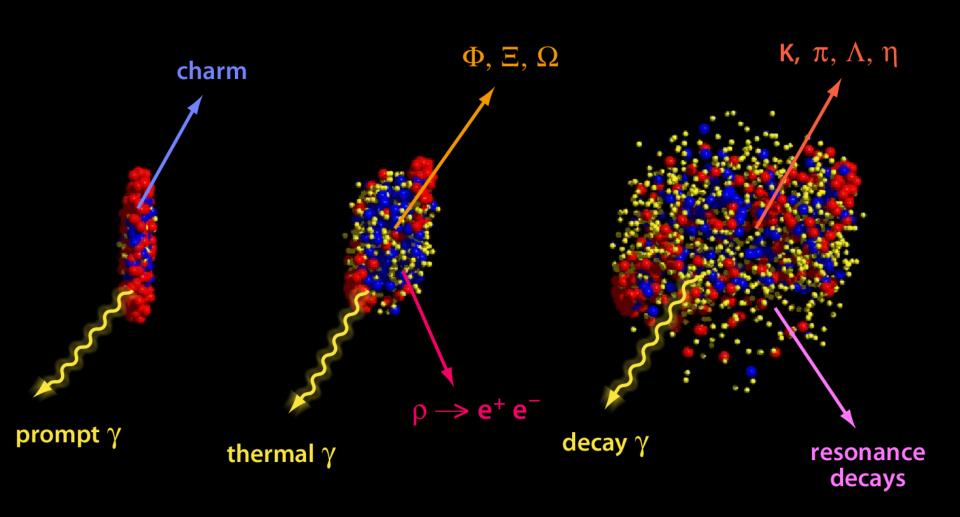

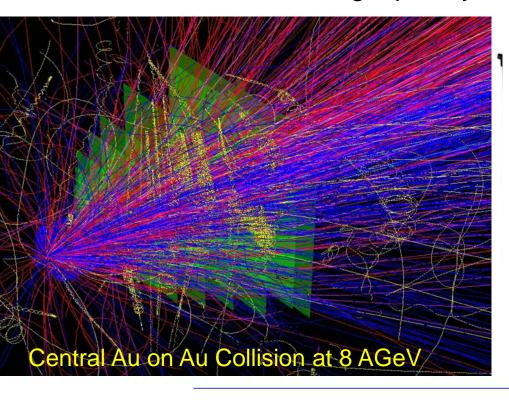

Collide Au heavy ions onto Au nuclei in a fixed target configuration at ~ 10 GeV/nucleus

## Diagnostic probes

## CBM technological challenges

# fixed target configuration makes 10MHz Au+Au interaction rate feasible at FAIR

- > 10 MHz → 6 billion tracks per second

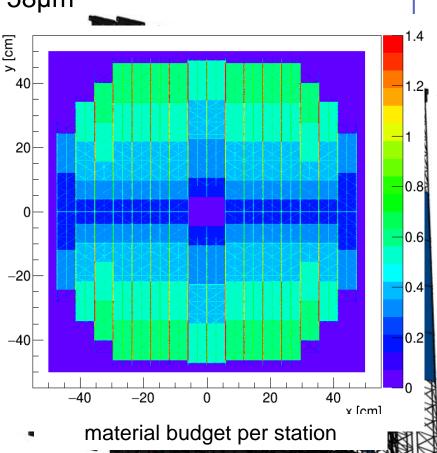

- $\triangleright$  determination of (displaced) vertices ( $\sigma \approx 50 \mu m$ )

- > identification of leptons and hadrons

- fast and radiation hard detectors

- free-streaming readout electronics

- high speed data acquisition and high performance computer farm for online event selection

- 4-D event reconstruction

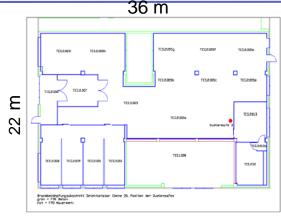

#### Detector Laboratory at GSI: 600 m<sup>2</sup> Clean-Room

#### **Competences:**

- Micro Patterned Gaseous Detector Technology

- Silicon Strip Detector Integration

- ASIC Handling and Integration

- Diamond Detectors

PSL APD-characterization lab

#### **Machinery:**

- Laser Lithography

- PVD

- Bonding Automates

- Probestation and Chip Handling

- Automated Wire Winding

- Digital Microscope

- Thin Foils Handling and Processing

- Gaseous Detector Ageing Teststands

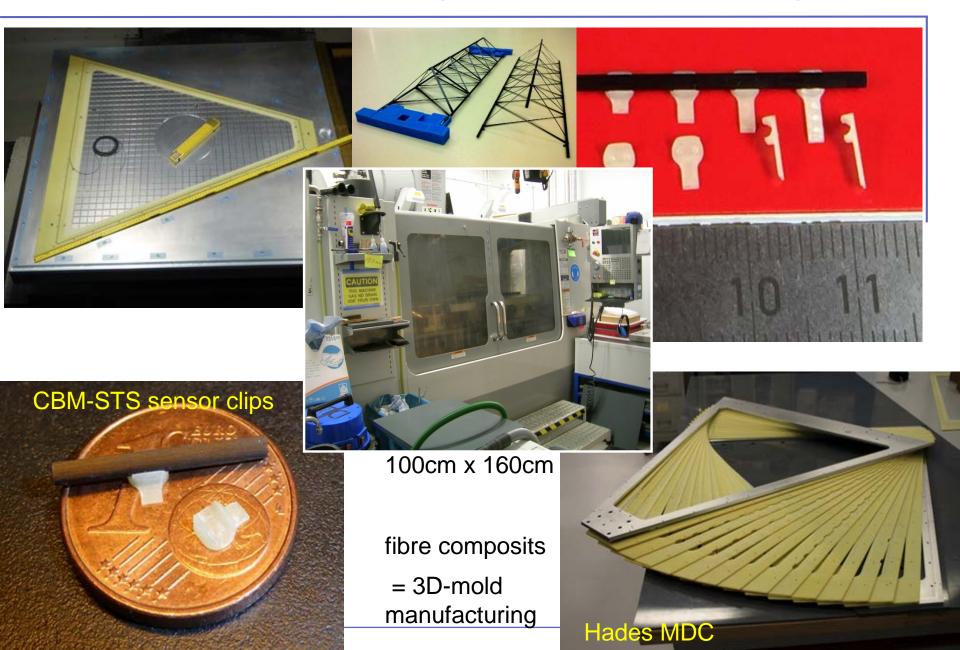

- Large Prototyping CNC Milling Machine

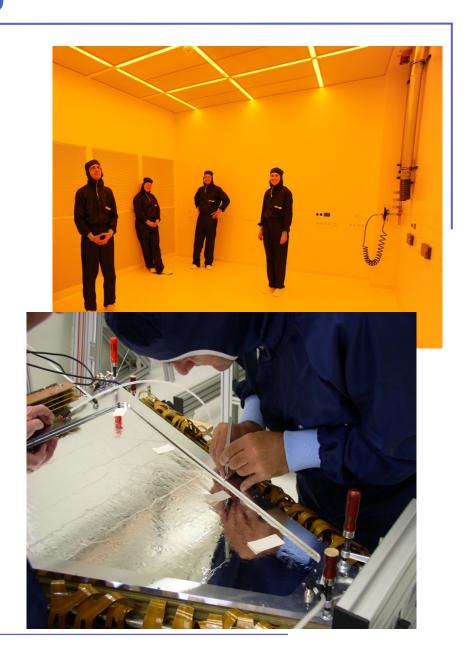

### ISO 3 Clean Room for Laser Lithography 1µ

5 x 5 mm<sup>2</sup> SCDiamond

### **Work at GSI Detectorlab**

#### Precision fibre composite milling from very small to very large

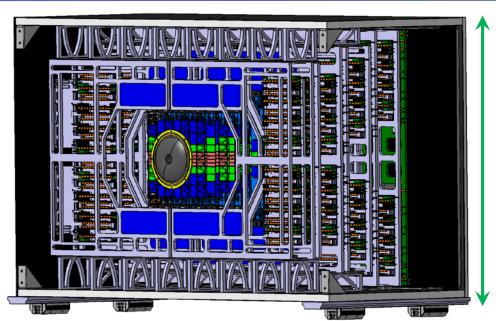

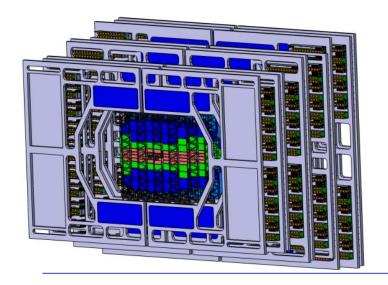

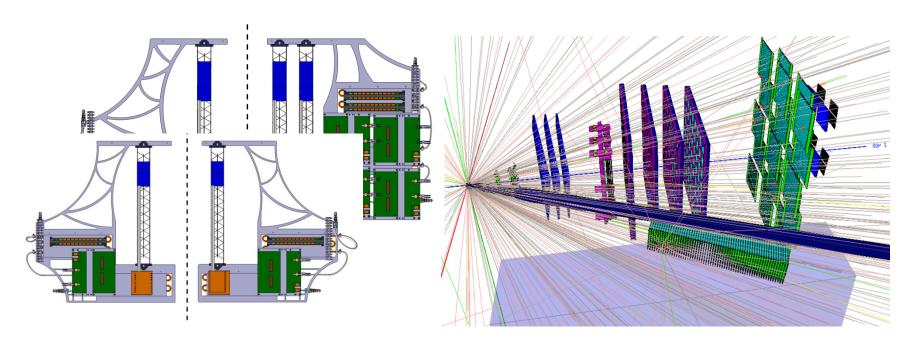

## **CBM Silicon Tracking System STS**

- Fixed Target Tracker, Acceptance 2,5°< θ < 25° to be fit into magnet yoke (1,4m)

- Double Sided Silicon Strips in 8 Layers, 58µm

- 2 Mio. readout channels, ~ 3 m²

- Event rate 10 MHz, freely streaming r/c

- less than 1% radiation length per layer

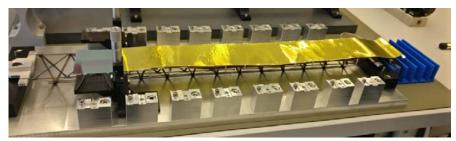

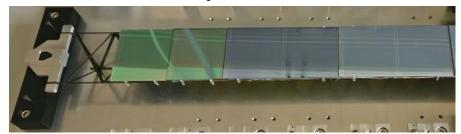

#### **Mechanical Integration in Fixed Target Configuration**

**Thermal enclosure**, operation at -5°C Minimize mat. budget in acceptance Electronics outside acceptance, 40kW

140cm

Ladder of 10 modules

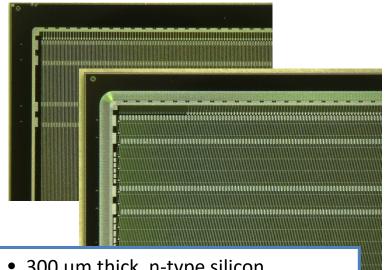

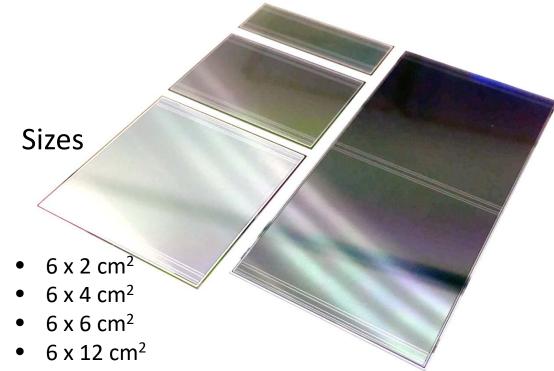

## Silicon-Doublesided-Microstrip-Sensors

- 300 µm thick, n-type silicon

- double-sided segmentation

- 2<sup>nd</sup> metal routing lines

- 1024 strips of 58 µm pitch

- rad. tol. up to  $10^{14}$   $n_{eq}$ /cm<sup>2</sup>

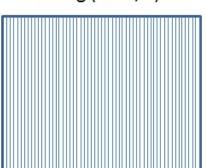

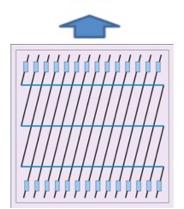

#### strip orientation at 58 µm pitch

7.5 deg (front/p)

0 deg (back/n)

connectivity, r/o direction

2<sup>nd</sup> metal interconnect required

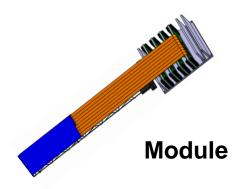

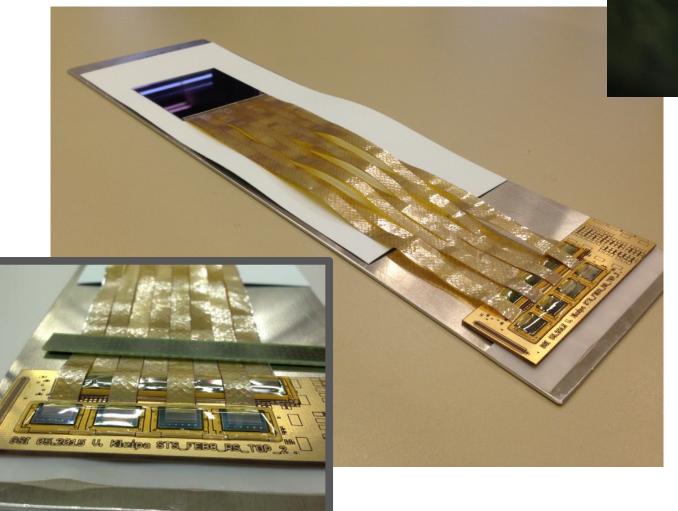

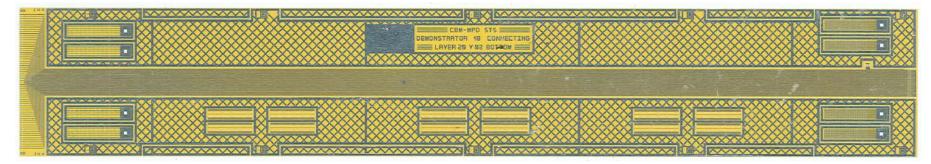

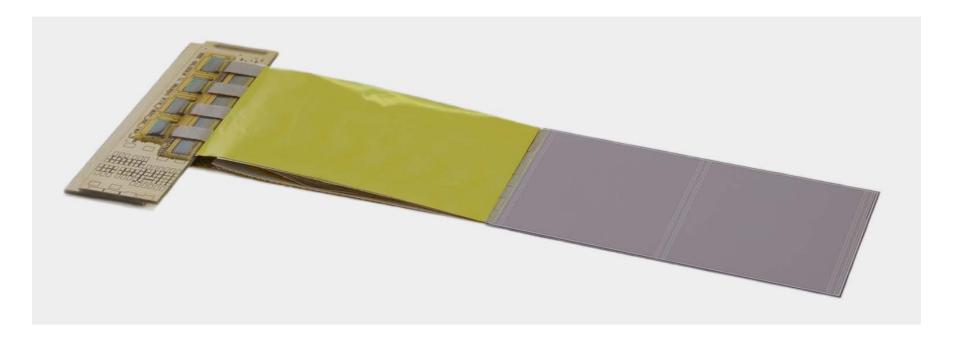

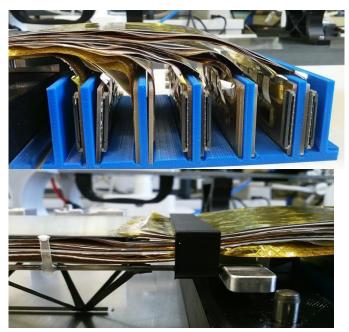

## CBM-STS-moduleassembly

- 1000 Modules

- 32 cables per module

- 2048 ch per module

- Tab bonding

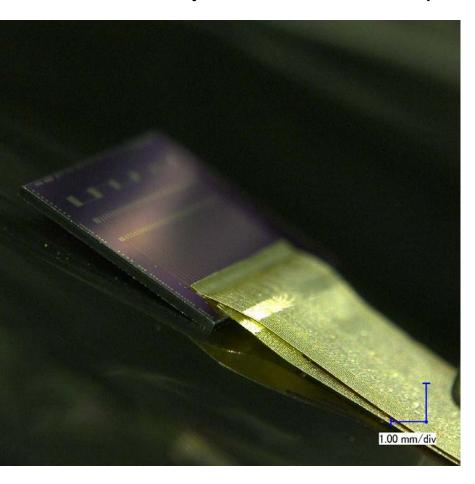

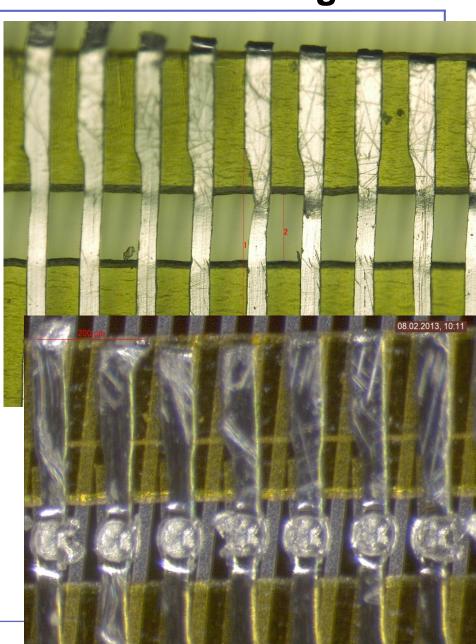

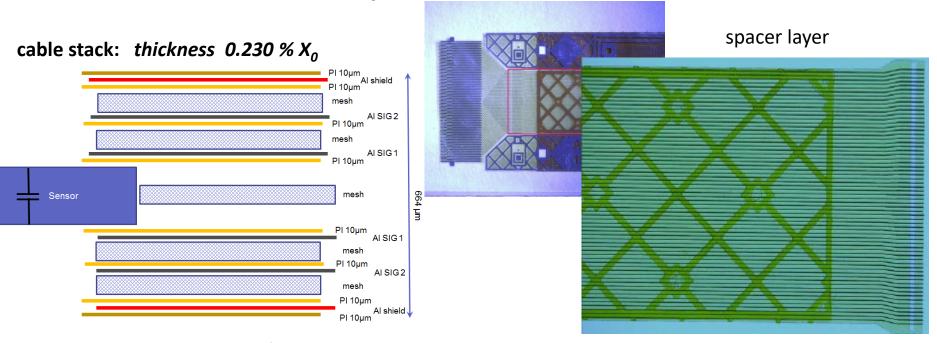

- Micro cables: 10µ Polyimide14µ Al traces

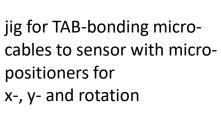

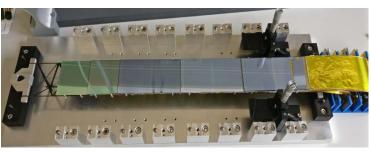

### Micro Cable Technology with TAB-Bonding

double cable layer bonded onto chip

#### 32.000 read-out cables

cooperation with LTU, Ukraine

signal layer: 64 Al lines of 116 μm pitch, 14 μm thick on 10 μm polyimide, lengths up to 55 cm

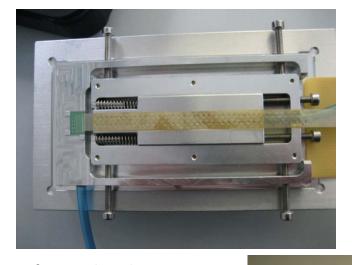

### **Assembly Jigs**

jig for TAB-bonding 1st microcable layer to ASIC

jig for TAB-bonding 1st and 2nd micro-cable layer to ASIC

#### **Tab-Bonding Chip-Cables to Silicon Sensor**

R-ASIC's

- fixing of the microcables with vacuum and alignment

- TAB-bonding of 16 microcables to the sensor (two rows at 8 microcables)

- protection of the TAB-bonds with Globtop after QA-measurements

Wire Bonding Chip-Cables to Readout Board

... and then the other side...

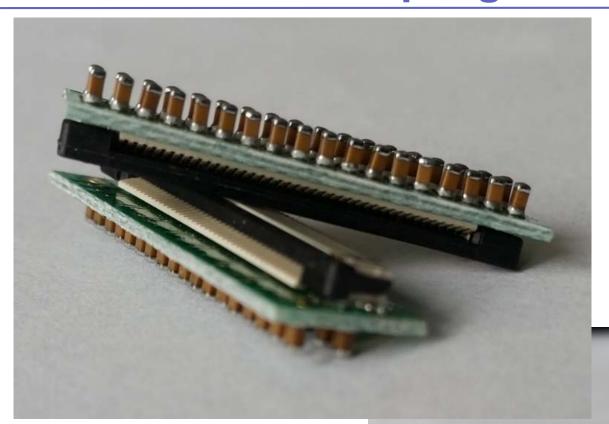

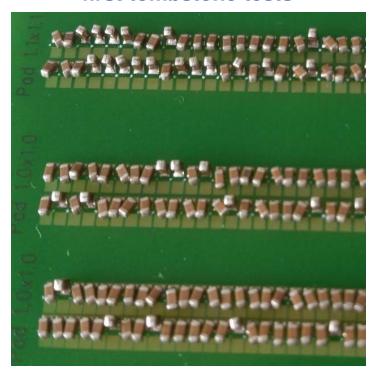

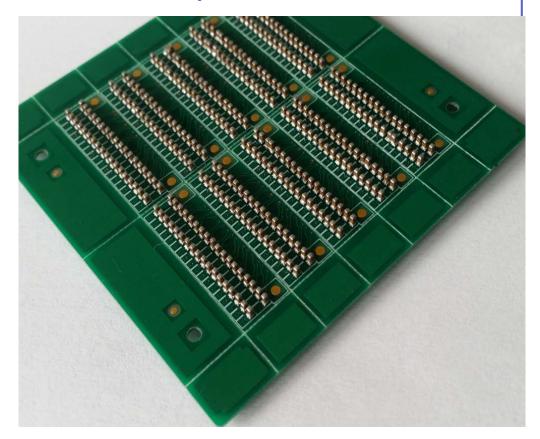

## **ZIF 500V-AC-Coupling Connector Part**

Mounted device sensitive to shear forces: need to add glue for robustness.

- 40-pin 0.5mm pitch ZIF

- Compatible to 40-line commercial shielded flat cable

- Height to be optimized

- good for up to 18 up-links

#### **Digital Interfacing: Bridging Signals to Gnd – 3D arrangement**

#### first tombstone tests

#### ...after optimization

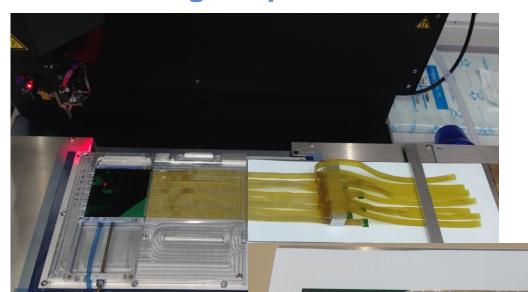

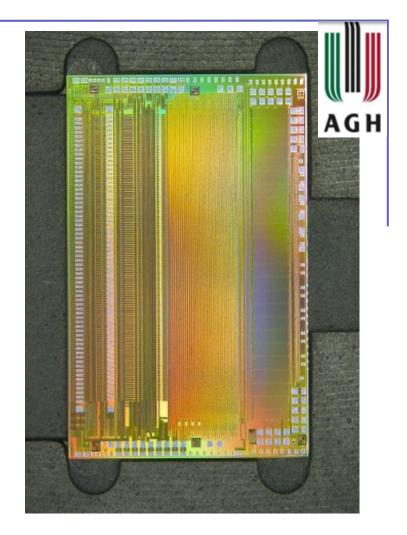

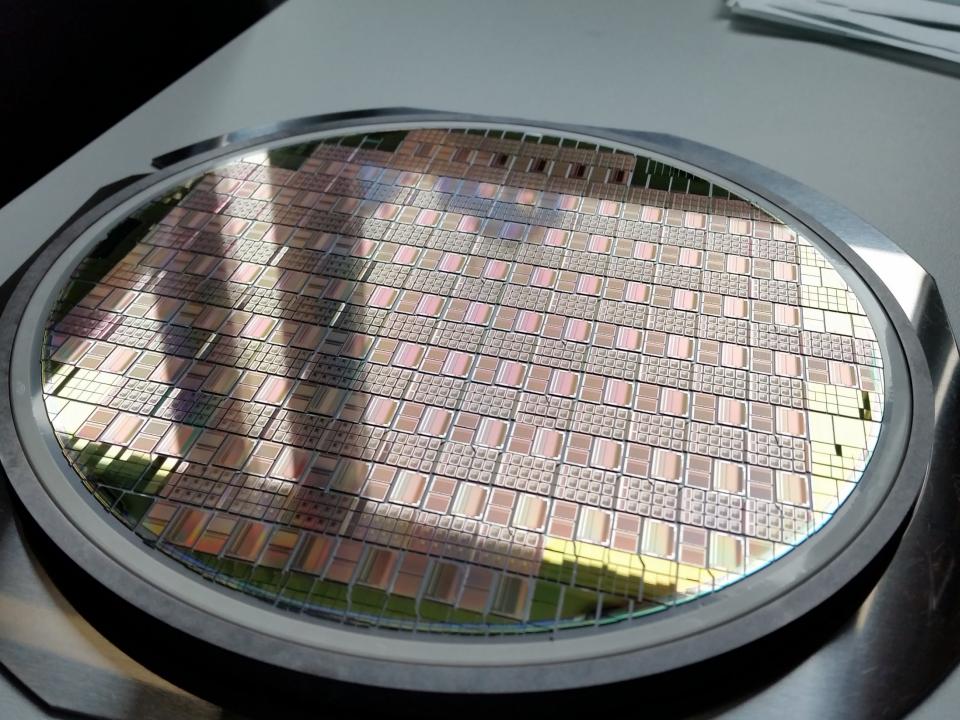

#### 128ch Readout ASIC serves as STS-XYTER and Much-XYTER r/o

- Moderate Time (~5ns) and Energy res. (5bit)

- 1000 electrons noise

- Switchable Gain, Identical Readout Logic

- GBTx-based DAQ, 32 Mhit/s each chip

- Power optimized, radiation tolerant

- Microchip ASIC developed at AGH Krakow,

- Design internationally reviewed,

- Detector Integration by international groups

#### **STS-XYTER Readout Microchip Analog Front End**

Krzysztof Kasinski and Robert Szczygiel of AGH Krakow, Poland

Switchable gain (5x smaller for MUCH) + trimming 2 bit **FAST PATH for TIME MEASURE** circuit stretcher  $C_{TEST}$ threshold O IN D to back-end Switchable (90ns - 280ns)in 4 steps **CSA PSC** digital peak ADC detector SLOW PATH for AMPLITUDE MEASUREMENT

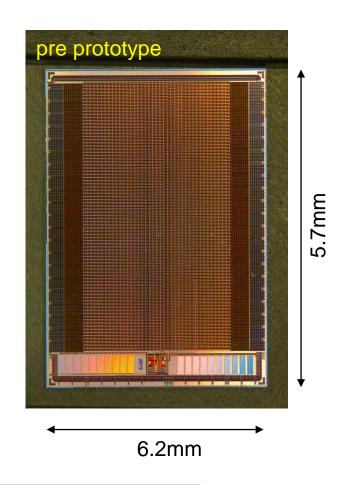

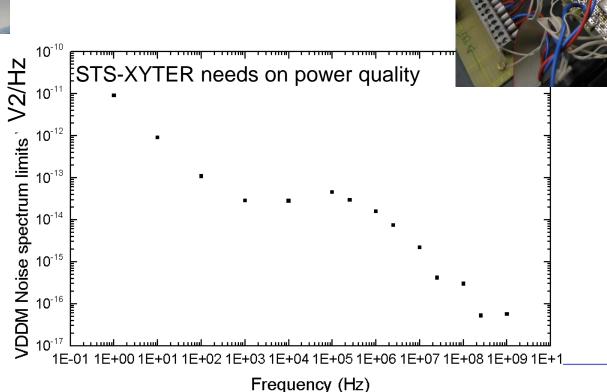

### Skimming LDOs: Development at SCL Chandigarh

- Output noise (100kHz to 100MHz) < 70µV RMS</p>

- 1/3 of STS-XYTER power-pin related signal noise (210 µV RMS),

- 1/10 noise power contribution

- Final size: 5.7mm x 6.2mm

- Two versions: 1.8V/1.6A and 1.2V/1.6A

- Ripple rejection up to 100kHz

- Junction temp up to 100°C

- No self-restart upon overcurrent

- Output enable

- 5 external parts (R, 4 Caps)

#### Power distribution in harsh environments

## Towards Rad Hard LDOs Cooperation with SCL Chandigarh

Three LDO chips survived 4x10<sup>13</sup>/cm<sup>2</sup> 2 GeV protons, no SEU observed

P. Koczon, S. Loechner, P. Wieczorek

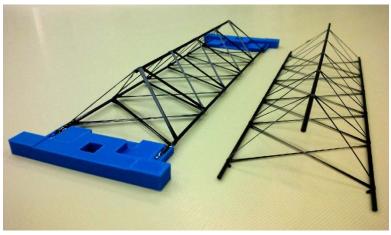

### **Final STS-Module:**

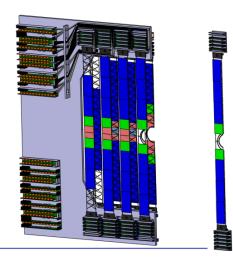

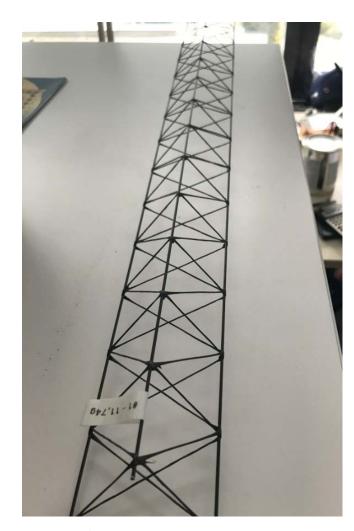

#### Concept inherited from ALICE ITS: Carbon fiber ladders

11g for 1m long ladder

mount 10 silicon modules onto one ladder

### **Assembly Tests: Modules onto Prototype Ladder**

**Dummy module - I**

**Dummy module - III**

**Dummy module - II**

**Dummy module - IV**

**Dummy module - V**

# Ladder assembly imposes mechanical challenges during assembly of modules onto ladder

- Cable stack is thick and stiff

- Need precise lengths of cables so they won't fold up

- While mounting on frame, handling difficulty.

# Mini-CBM @ FAIR Phase 0: fully assemble and operate small functional CBM subset

Currently: pre-series modules employed in the miniSTS of mCBM@SIS18

13 modules, arranged on 5 ladders, forming 2 tracking stations mCBM run 02/2019: mCBM run scheduled May 2020: 4 modules on 2 ladders further 9 modules on 3 ladders

## The CBM Collaboration

First physics beam targeted in 2024

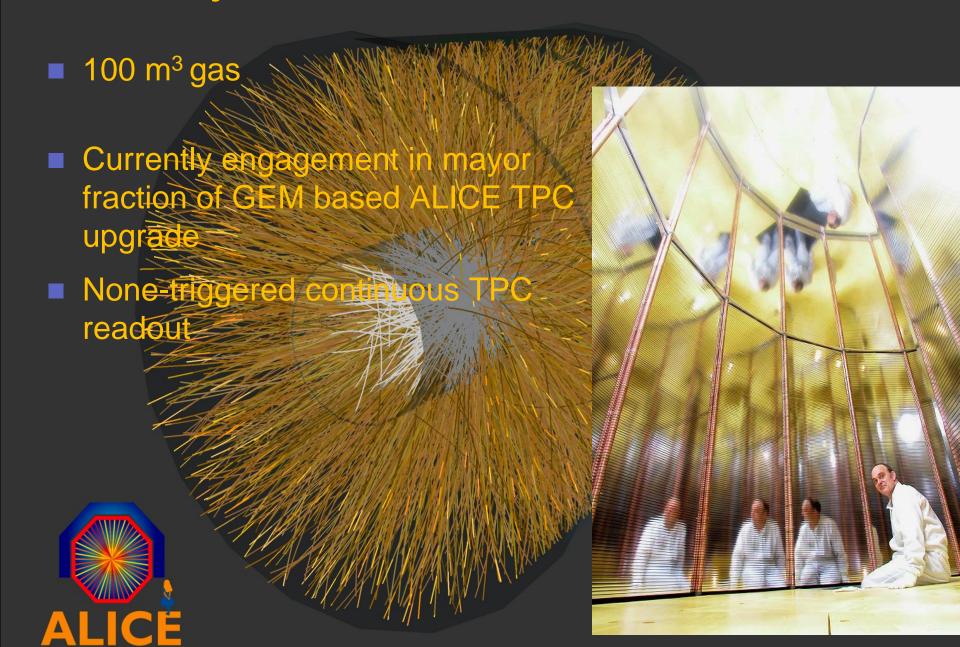

### Time Projection Chamber, the Queen of Trackers

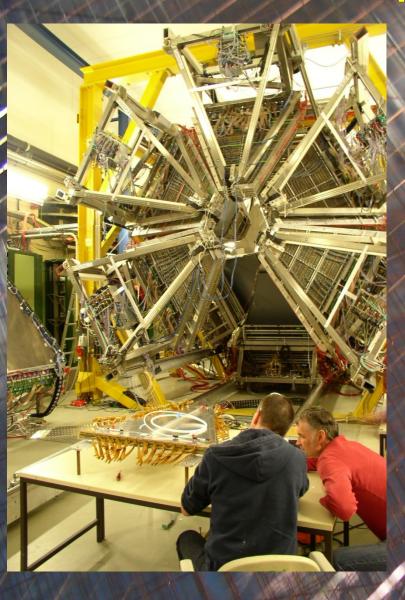

## HADES- The GSI Dilepton Spectrometer

Detector lab engagement in HADES Drift.

Chamber design and production