# The HitDetection ASIC A Customised IC for PANDA Readout

Holger Flemming

GSI Experiment Electronics / ASIC Design

#### **Contents**

- The first idea

- The Hit detection ASIC concept

- The hit detection unit

- The integration level

- Open Questions

- Rough estimated time schedule

#### The First Idea

- First idea of this chip in a proposal of Igor Konorov from July 2007

- New initiativ for a customised digitising IC for PANDA EMC end of 2009

- Different types of architectures have been discussed

- GSI ASIC design proposed to use the hit detection ASIC architecture

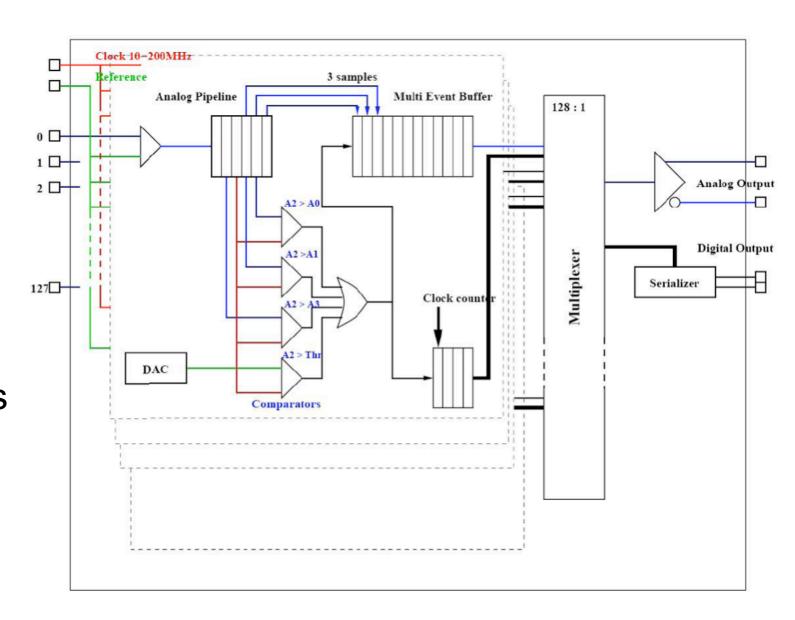

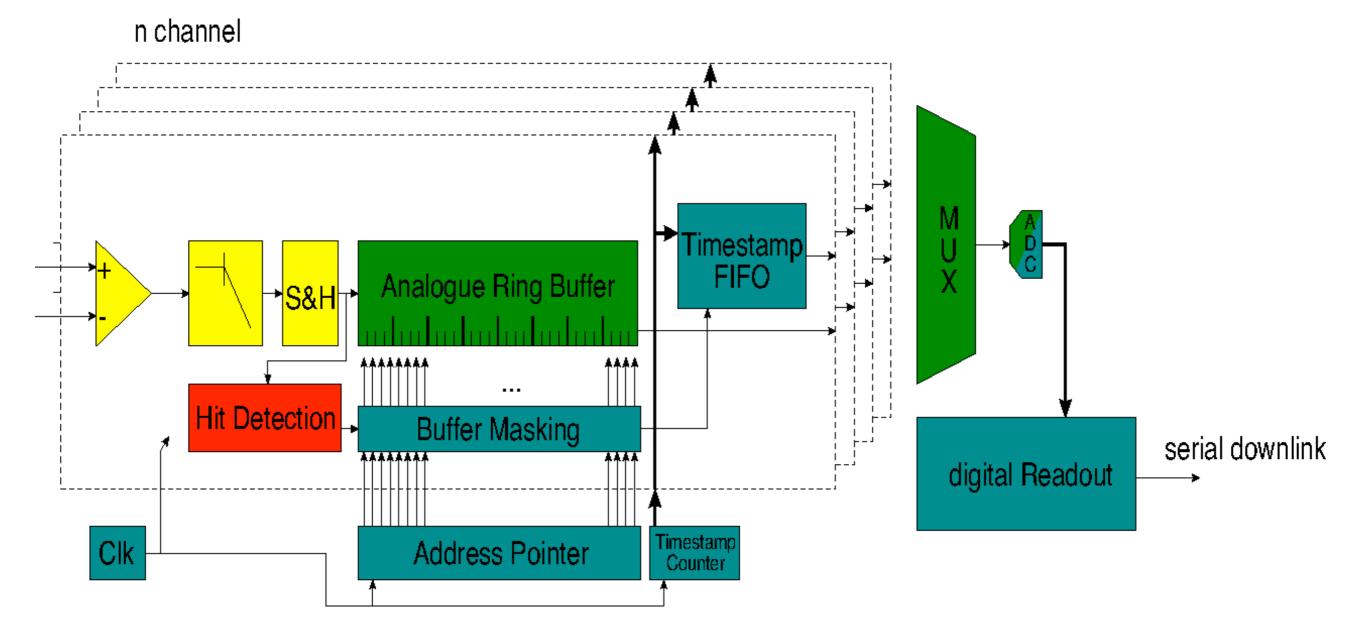

### **The Hit Detection ASIC Concept**

- Self triggered transient recorder

- Configurable sampling rate and record length

- On chip ADC ⇒ digital readout

#### **The Hit Detection Unit**

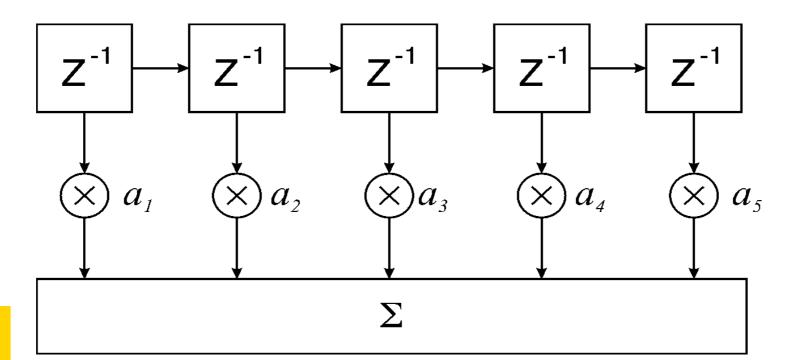

- In the proposal of Igor: A FIR Filter (Finite Impulse Respond)

- A continous level, discrete time filter

- FIR filter should be able to detect hits in a pile up situation

- Drawback: Very complex circuit

- Do we realy need a FIR filter?

- Order of this filter

- Do we need free configurable filter coefficients or are fixed coefficients sufficient?

## **Integration Level**

- Channel Pitch is given by bonding Pads

- Differential Inputs ⇒ 2 Pads / Channel

- With staggered input Pads ⇒ Channel Pitch = 100 μm

| Number of channels | size    | comments                                        |

|--------------------|---------|-------------------------------------------------|

| 32                 | 3.2 mm  |                                                 |

| 64                 | 6.4 mm  |                                                 |

| 128                | 12.8 mm | large chip may lead into yield problems / power |

## **Open Questions**

- Input specifications

- Common mode range / dynamic range

- Sample frequency

- Anti aliasing filter needed?

- Transient records

- How many samples are needed?

- Event rates?

- Radiation environment

## Time Schedule (rough estimation)

- Hit detection core development:

- 2010 : First Testchip with analogue buffer teststructures with fast write and slow readout

- 2011: Second Testchip with improved components from first testchip

- 2012 : First prototype?

- ADC development in parallel

- There is interest from PI Heidelberg to participate at this part