| •0 |  |  |

|----|--|--|

|    |  |  |

The HDL description of FPGA-based system allows to assign initial values to the internal signals

| <b>•</b> 0 |  |  |

|------------|--|--|

|            |  |  |

- The HDL description of FPGA-based system allows to assign initial values to the internal signals

- However, sometimes more complex initialization procedure may be needed

| <b>●</b> 0 |  |  |

|------------|--|--|

|            |  |  |

同トイヨトイヨト

- The HDL description of FPGA-based system allows to assign initial values to the internal signals

- However, sometimes more complex initialization procedure may be needed

- In simple cases it may provided by small state machines

| <b>•</b> 0 |  |  |

|------------|--|--|

|            |  |  |

- The HDL description of FPGA-based system allows to assign initial values to the internal signals

- However, sometimes more complex initialization procedure may be needed

- In simple cases it may provided by small state machines

- In more complicated cases initialization via control bus may be needed

| •o |  |  |

|----|--|--|

|    |  |  |

- The HDL description of FPGA-based system allows to assign initial values to the internal signals

- However, sometimes more complex initialization procedure may be needed

- In simple cases it may provided by small state machines

- In more complicated cases initialization via control bus may be needed

- Similarly debugging and testing of the system usually requires access via control bus

| <b>●</b> ○ |  |  |

|------------|--|--|

|            |  |  |

- The HDL description of FPGA-based system allows to assign initial values to the internal signals

- However, sometimes more complex initialization procedure may be needed

- In simple cases it may provided by small state machines

- In more complicated cases initialization via control bus may be needed

- Similarly debugging and testing of the system usually requires access via control bus

- Those tasks may be done from external computer via control interface, e.g., IPbus

| •0 |  |  |

|----|--|--|

|    |  |  |

(ロ) (日) (日) (日)

- The HDL description of FPGA-based system allows to assign initial values to the internal signals

- However, sometimes more complex initialization procedure may be needed

- In simple cases it may provided by small state machines

- In more complicated cases initialization via control bus may be needed

- Similarly debugging and testing of the system usually requires access via control bus

- Those tasks may be done from external computer via control interface, e.g., IPbus

- However, in case if we need an autonomous initialization of our system, the local CPU may be needed

| Introduction |  |  |

|--------------|--|--|

|              |  |  |

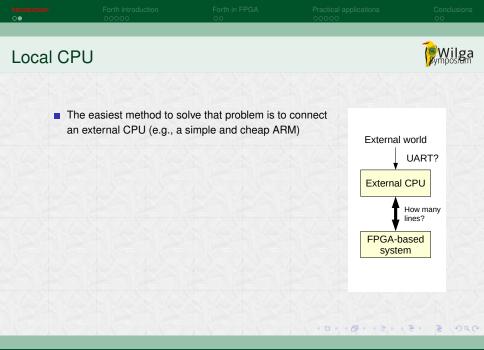

- The easiest method to solve that problem is to connect an external CPU (e.g., a simple and cheap ARM)

- That must be done at the PCB design stage, and increases complexity of the board

イロン (部) (き) (き)/(き

| 00 |  |  |

|----|--|--|

|    |  |  |

- The easiest method to solve that problem is to connect an external CPU (e.g., a simple and cheap ARM)

- That must be done at the PCB design stage, and increases complexity of the board

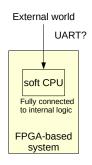

- Another possibility is to use a soft CPU implemented in FPGA

イロン (部) (ヨ) (ヨ)/ヨ

| 00 |  |  |

|----|--|--|

|    |  |  |

- The easiest method to solve that problem is to connect an external CPU (e.g., a simple and cheap ARM)

- That must be done at the PCB design stage, and increases complexity of the board

- Another possibility is to use a soft CPU implemented in FPGA

- There are many soft CPUs that may be programmed in C - LatticeMico32, microblaze, RiscV and many more...

(ロ) (部)(さ)(さ)(き)/ほ

| 00 |  |  |

|----|--|--|

|    |  |  |

- The easiest method to solve that problem is to connect an external CPU (e.g., a simple and cheap ARM)

- That must be done at the PCB design stage, and increases complexity of the board

- Another possibility is to use a soft CPU implemented in FPGA

- There are many soft CPUs that may be programmed in C - LatticeMico32, microblaze, RiscV and many more...

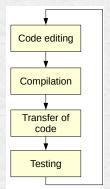

- Modification of the program is long (requires editing of source code and recompilation), and the dedicated C toolchain must be available

イロン (日) (日) (日) (日)/日

| 00 |  |  |

|----|--|--|

|    |  |  |

- The easiest method to solve that problem is to connect an external CPU (e.g., a simple and cheap ARM)

- That must be done at the PCB design stage, and increases complexity of the board

- Another possibility is to use a soft CPU implemented in FPGA

- There are many soft CPUs that may be programmed in C - LatticeMico32, microblaze, RiscV and many more...

- Modification of the program is long (requires editing of source code and recompilation), and the dedicated C toolchain must be available

- Another possibility is to use Forth-capable CPU

イロン (日) (日) (日) (日)/日

|       |         | Forth introdu |           |        |          |           |          |                               |       |

|-------|---------|---------------|-----------|--------|----------|-----------|----------|-------------------------------|-------|

|       |         |               |           |        |          |           |          |                               |       |

| Forth | ı langu | age           |           |        |          |           |          | Ī                             | Wilga |

|       | Lang    | uage cre      | eated for | embedd | ed and r | real-time | applicat | ions [ <mark>1</mark> ]       |       |

|       |         |               |           |        |          |           |          |                               |       |

|       |         |               |           |        |          |           |          |                               |       |

|       |         |               |           |        |          |           |          |                               |       |

|       |         |               |           |        |          |           |          |                               |       |

|       |         |               |           |        |          |           |          |                               |       |

| 1170  | 14.70   | 11070         | 1. 70     | 170    |          |           |          | <ul><li>&lt; 王 &gt;</li></ul> | E Dag |

|            | Forth introduction    |                 |                          |    |

|------------|-----------------------|-----------------|--------------------------|----|

|            |                       |                 |                          |    |

| Forth lang | guage                 |                 |                          |    |

|            |                       |                 |                          |    |

| 🔳 La       | nguage created for    | or embedded and | real-time applications [ | 1] |

| Ve         | ry efficient for inte | eractive work   |                          |    |

|            |                       |                 |                          |    |

|            |                       |                 |                          |    |

|            |                       |                 |                          |    |

|            |                       |                 |                          |    |

|            |                       |                 |                          |    |

|            |                       |                 |                          |    |

|            |                       |                 |                          |    |

| Introduction | Forth introduction<br>●0000 | Forth in FPGA | Practical applications | Conclusions |

|--------------|-----------------------------|---------------|------------------------|-------------|

|              |                             |               |                        |             |

| Forth lar    | • •                         |               |                        |             |

- Language created for embedded and real-time applications [1]

- Very efficient for interactive work

- Typically development is done using the bottom-up approach

- Language created for embedded and real-time applications [1]

- Very efficient for interactive work

- Typically development is done using the bottom-up approach

- Complex routines (words) are created from well tested simple lower level words

## Forth language

- Language created for embedded and real-time applications [1]

- Very efficient for interactive work

- Typically development is done using the bottom-up approach

- Complex routines (words) are created from well tested simple lower level words

- Forth offers compact code with reasonable speed od execution

## Forth language

イロン (部) (ヨ) (ヨ)/ヨ

- Language created for embedded and real-time applications [1]

- Very efficient for interactive work

- Typically development is done using the bottom-up approach

- Complex routines (words) are created from well tested simple lower level words

- Forth offers compact code with reasonable speed od execution

- It is possible to create complex, modular applications via incremental compilation

## Forth language

イロン (部) (ヨ) (ヨ)/ヨ

- Language created for embedded and real-time applications [1]

- Very efficient for interactive work

- Typically development is done using the bottom-up approach

- Complex routines (words) are created from well tested simple lower level words

- Forth offers compact code with reasonable speed od execution

- It is possible to create complex, modular applications via incremental compilation

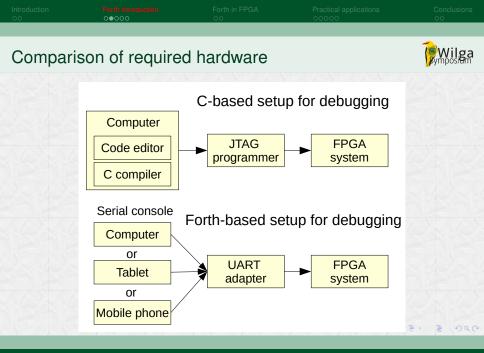

- The whole compiler and Forth CPU may be implemented in simple hardware, all what is needed for development is a serial console

Forth CPU for FPGA

| Introduction | Forth introduct             | lion  | Forth in F | PGA                 | Practical<br>00000 | applications |                                | Conclusions        |

|--------------|-----------------------------|-------|------------|---------------------|--------------------|--------------|--------------------------------|--------------------|

| Typical w    | vork with I                 | Forth |            |                     |                    |              | Ĩ                              | Wilga<br>Symposium |

|              | se defined w<br>teractively | vords |            | >2 3 *<br>6 ok<br>> |                    |              |                                |                    |

|              |                             |       |            |                     |                    |              |                                |                    |

|              |                             |       |            |                     |                    |              |                                |                    |

|              |                             |       |            |                     |                    |              |                                |                    |

|              |                             |       |            |                     |                    |              | <ul><li>・&lt; 差 &gt;</li></ul> | き うへで              |

| Forth introduction |  |  |

|--------------------|--|--|

|                    |  |  |

## Typical work with Forth

Use defined words >: fac interactively

Create new words with usefull sequences of existing words

ok

>: fac ( n -- n! )

1 swap 1+ 1

?do i \*

loop ;

ok

| Introduction |                           | Forth in FPGA       | Practical applications | Conclusions<br>00 |

|--------------|---------------------------|---------------------|------------------------|-------------------|

|              |                           |                     |                        |                   |

| Typical w    | work with Forth           |                     |                        | Wilga             |

|              | Jse defined words         | > 2 3               | + fac                  |                   |

|              | nteractively              | ok                  |                        |                   |

| <b>C</b>     | Create new words with     | >.                  |                        |                   |

| u            | sefull sequences of exist | ting <sup>120</sup> | ok                     | 11-22-51-2        |

>

イロン (日) (日) (日) (日)

words

Use the new words together with the previous ones

| Introduction |                                                                         | Forth in FPGA       | Practical applications | Conclusions<br>00 |

|--------------|-------------------------------------------------------------------------|---------------------|------------------------|-------------------|

|              |                                                                         |                     |                        |                   |

| Туріс        | al work with Forth                                                      |                     |                        |                   |

|              | <ul> <li>Use defined words<br/>interactively</li> </ul>                 | > 2 3<br>ok         | + fac                  |                   |

|              | Create new words with                                                   | >.                  |                        |                   |

|              | usefull sequences of exist                                              | ting <sup>120</sup> | ok                     |                   |

|              | words                                                                   | >                   |                        |                   |

|              | <ul> <li>Use the new words togeth<br/>with the previous ones</li> </ul> | ner                 |                        |                   |

イロン イヨン イヨン

4 = >

How to avoid filling memory with incorrect definitions?

| 00     |                                                                                        | 0               |     | 00                 |

|--------|----------------------------------------------------------------------------------------|-----------------|-----|--------------------|

| Туріса | al work with Forth                                                                     | _               |     | Wilga<br>Symposium |

|        | <ul> <li>Use defined words<br/>interactively</li> </ul>                                | > 2 3 +<br>ok   | fac |                    |

|        | <ul> <li>Create new words with<br/>usefull sequences of existi<br/>words</li> </ul>    | >.<br>ng 120 ok |     |                    |

| -      | Use the new words togethe<br>with the previous ones                                    | er              |     |                    |

|        | How to avoid filling memor<br>with incorrect definitions?                              | у               |     |                    |

|        | It is possible to save the st<br>of the system using the<br>marker word, and restore i |                 |     |                    |

|        | later                                                                                  |                 |     | ► 990              |

| Introduction | Forth introduction | Forth in FPGA  | Practical applications | Conclusions<br>00 |

|--------------|--------------------|----------------|------------------------|-------------------|

|              |                    |                |                        |                   |

| Interactiv   | ve work and cr     | eating of prog | grams                  |                   |

|              |                    |                |                        |                   |

How to create the program when working in interactive mode?

| Forth introduction |  |  |

|--------------------|--|--|

|                    |  |  |

- How to create the program when working in interactive mode?

- We may simply dump the code memory contents at the end of the session and load it at the begining of the new one. But what if we want sources?

| Forth introduction |  |  |

|--------------------|--|--|

|                    |  |  |

- How to create the program when working in interactive mode?

- We may simply dump the code memory contents at the end of the session and load it at the begining of the new one. But what if we want sources?

- If sources are not available, then we have "write only language"...

| Forth introduction |  |  |

|--------------------|--|--|

|                    |  |  |

- How to create the program when working in interactive mode?

- We may simply dump the code memory contents at the end of the session and load it at the begining of the new one. But what if we want sources?

- If sources are not available, then we have "write only language"...

- We can capture our commands in the terminal program.

| Forth introduction |  |  |

|--------------------|--|--|

|                    |  |  |

- How to create the program when working in interactive mode?

- We may simply dump the code memory contents at the end of the session and load it at the begining of the new one. But what if we want sources?

- If sources are not available, then we have "write only language"...

- We can capture our commands in the terminal program.

- The captured definitions may be then moved to the source files.

| Forth introduction |  |  |

|--------------------|--|--|

|                    |  |  |

ロン (個) (日) (日)

- How to create the program when working in interactive mode?

- We may simply dump the code memory contents at the end of the session and load it at the begining of the new one. But what if we want sources?

- If sources are not available, then we have "write only language"...

- We can capture our commands in the terminal program.

- The captured definitions may be then moved to the source files.

- At the begining of the new session we may transfer those files to the Forth CPU

|  |  | 00 |

|--|--|----|

## Examples of Forth code

- Stack based language

- Reverse Polish notation used in calculations

- Limited support for local variables

```

i2c_wr1 writes a single byte

i2c wr1 ( dta addr -- )

2* i2c slv

I2C REGS 3 + io!

64 16 or

I2C_REGS 4 + io!

begin

I2C_REGS 4 + i00

dup 2 and

while

drop

repeat

128 and if

\ NACK in data

134 err_halt

then

```

#### Forth for FPGA

イロン (日) (日) (日) (日)

- There are multiple implementations of Forth CPU in HDL (Verilog or VHDL)

- http://www.forth.org/cores.html

- http://www.ultratechnology.com/chips.htm

- We have tried to implement our own "tethered" version [2].

- The most successful implementation seems to be the J1 CPU designed by James Bowman [3].

- The original version is implemented in Verilog in 117 lines [4].

|         |          | Forth in FPGA<br>○● |  |

|---------|----------|---------------------|--|

|         |          |                     |  |

| J1B bas | ed Forth |                     |  |

# Wmpos Em

イロン (日) (日) (日) (日)/日

- The Forth CPU is only one component of the successful Forth system

- What's needed is also the Forth compiler/interpreter with libraries

## J1B based Forth

- The Forth CPU is only one component of the successful Forth system

- What's needed is also the Forth compiler/interpreter with libraries

- The Swapforth has been prepared for J1B and for other platforms

# J1B based Forth

(ロ) (部)(さ)(さ)(き)/ほ

- The Forth CPU is only one component of the successful Forth system

- What's needed is also the Forth compiler/interpreter with libraries

- The Swapforth has been prepared for J1B and for other platforms

- It is supplemented with convenient shell written in Python that supports:

- saving the commands to the history file

- dumping the memory contents to the file

- Ioading source files to the Forth CPU

# J1B based Forth

イロン (部) (ヨ) (ヨ)/ヨ

- The Forth CPU is only one component of the successful Forth system

- What's needed is also the Forth compiler/interpreter with libraries

- The Swapforth has been prepared for J1B and for other platforms

- It is supplemented with convenient shell written in Python that supports:

- saving the commands to the history file

- dumping the memory contents to the file

- Ioading source files to the Forth CPU

- The "cold" word, if defined, is executed after the powerup or reset

|  | •0000 |  |

|--|-------|--|

|  |       |  |

# Wilga

## AFCK board controller

- Project developed for AFCK boards used as DPB prototype in CBM experiment

- Forth CPU uses I2C interface

- to read the MAC address

- to configure the Silabs Si57x clock generator

- to configure clock switch matrix

- Support for Si57x required implementation of multiple precision arithmetics library

- The status of the initialization routine may be stored in register available for the firmware

(ロ) (部)(さ)(さ)(き)/ほ

|                 |                                                                                                                    |                               | Practical applications | Conclusions   |

|-----------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------|---------------|

|                 |                                                                                                                    |                               |                        |               |

| Example         | e word from ari                                                                                                    | thmetics libra                | ry                     |               |

|                 |                                                                                                                    |                               |                        |               |

| : ud<<br>\<br>r | finition of the a<br>( a0 a1 b0 b1 -<br>If MSW are equa<br>ot ( a0 b0 b1 a1<br>ver over = if ( a<br>\ MSWs are equ | flag )<br>l, check the L<br>) | SW                     |               |

|                 | drop drop ( al                                                                                                     |                               |                        |               |

|                 | u<                                                                                                                 |                               |                        |               |

|                 | <pre>lse ( a0 b0 b1 a</pre>                                                                                        | equal, so the                 | eir comparison pro     | oduces the :  |

| ; /             |                                                                                                                    |                               |                        | 7. 1. 1. 7. 1 |

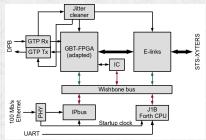

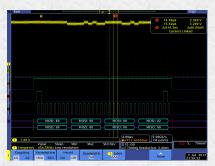

## GBTxEMU System controller

- Forth CPU is one of three masters of the internal Wishbone bus

- Its task is to initialize the system at powerup so that it can be further controlled via optical link

- Later on it can be used for interactive debugging and testing

- Access to internal registers is supported by address tables generated by the addr\_gen\_wb framework.

イロン (部) (ヨ) (ヨ)/ヨ

|  | 00000 |  |

|--|-------|--|

|  |       |  |

# Wilga

# Sayma board controller

- Library developed for Sinara project

- Implements support for many SPI connected peripherals

|  | Practical applications |          |

|--|------------------------|----------|

|  |                        |          |

|  |                        | <b>*</b> |

### How to start with Forth

- Experimenting with Forth does not require FPGA board

- J1B provides also the emulated environment based on Verilator

- Gforth is available for PC

- There are many implementations for microcontrollers. Just a few examples:

- Mecrisp for ARMs

- FlashForth for AVR and PIC microcontrollers

- Amforth for AVR and RISC-V

- Punyforth for ESP8266

#### Conclusions

- Forth based CPU may be a convenient tool for initialization and interactive debugging of FPGA-based systems

- It allows interactive debugging and testing of hardware

|  |  | Conclusions |

|--|--|-------------|

|  |  |             |

## Conclusions

- Forth based CPU may be a convenient tool for initialization and interactive debugging of FPGA-based systems

- It allows interactive debugging and testing of hardware

- Words created in interactive session may be used to create complex applications, e.g. used for initialization of the hardware.

- The ready application may be automatically started after power-up

## Conclusions

イロン (日) (日) (日) (日)

- Forth based CPU may be a convenient tool for initialization and interactive debugging of FPGA-based systems

- It allows interactive debugging and testing of hardware

- Words created in interactive session may be used to create complex applications, e.g. used for initialization of the hardware.

- The ready application may be automatically started after power-up

- Forth may be a good solution for interactive in-field debugging or testing also of MCU-based systems

|        |                                                                                                 |                   |                       | Conclusions<br>⊙● |

|--------|-------------------------------------------------------------------------------------------------|-------------------|-----------------------|-------------------|

|        |                                                                                                 |                   |                       |                   |

| Biblic | graphy                                                                                          |                   |                       | Wilga             |

| [1]    | Leo Brodie.<br>Thinking Forth.<br>http://thinking-forth                                         | sourceforge.net/  |                       |                   |

| [2]    | Paweł Goździkowski and Wo<br>Tethered Forth system for FF<br><i>Proc. SPIE</i> , 8903:89031M, C | PGA applications. |                       |                   |

| [3]    | James Bowman.<br>The J1 forth CPU, 2010.<br>https://www.excamera.co                             | om/sphinx/fpga-j1 | L.html.               |                   |

| [4]    | James Bowman.<br>The J1B source code, 2010.<br>https:<br>//github.com/jamesbowma                | an/swapforth/blob | o/master/jlb/verilog/ | j1.v.             |