## Automatic management of local bus address space in complex FPGA-implemented hierarchical systems

Wojciech M. Zabołotny<sup>1</sup>, Marek Gumiński<sup>1</sup>, Michał Kruszewski<sup>1</sup>,

<sup>1</sup>Institute of Electronic Systems, Warsaw University of Technology

XLIV-th IEEE-SPIE Joint Symposium Wilga 2019

(ロ) (部)(さ)(さ)(き)/ほ

### Introduction

- The data processing systems are often implemented in FPGA as parameterized, complex, multilevel hierarchical systems

- Its configuration and diagnostics requires convenient access to the internal blocks via control interface

- Scalable and flexible implementation of the control interface is particularly important in systems developed by many independent teams, or in subsystems designed for reuse. An example may be firmware components and subsystems developed for CBM experiment.

### Introduction

- The data processing systems are often implemented in FPGA as parameterized, complex, multilevel hierarchical systems

- Its configuration and diagnostics requires convenient access to the internal blocks via control interface

- Scalable and flexible implementation of the control interface is particularly important in systems developed by many independent teams, or in subsystems designed for reuse. An example may be firmware components and subsystems developed for CBM experiment.

- The key questions in such interfaces are:

- routing of control interface between blocks

- creating of address maps (assignment of addresses both for HW and SW)

(ロ) (部) (ヨ) (ヨ)

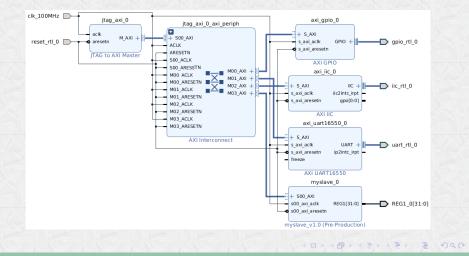

### Vendor tools - Xilinx - block design

### Vendor tools - Xilinx - address allocation

| Slave Interface | Base Name                            | Offset Address                                   | Range                                                                                | High Address                                                                                                                            |

|-----------------|--------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

|                 |                                      |                                                  |                                                                                      |                                                                                                                                         |

| its : 4G)       |                                      |                                                  |                                                                                      |                                                                                                                                         |

| S_AXI           | Reg                                  | 0x4000_0000                                      | 64K 🔻                                                                                | 0x4000_FFFF                                                                                                                             |

| S_AXI           | Reg                                  | 0x4080_0000                                      | 64K 👻                                                                                | 0x4080_FFFF                                                                                                                             |

| S_AXI           | Reg                                  | 0x44A0_0000                                      | 64K 👻                                                                                | 0x44A0_FFFF                                                                                                                             |

| S00_AXI         | S00_AXI_reg                          | 0x44A1_0000                                      | 64K 👻                                                                                | 0x44A1_FFFF                                                                                                                             |

|                 |                                      |                                                  |                                                                                      |                                                                                                                                         |

|                 |                                      |                                                  |                                                                                      |                                                                                                                                         |

|                 | its : 4G)<br>S_AXI<br>S_AXI<br>S_AXI | tts : 4G)<br>S_AXI Reg<br>S_AXI Reg<br>S_AXI Reg | its : 4G)<br>S_AXI Reg 0x4000_0000<br>S_AXI Reg 0x4080_0000<br>S_AXI Reg 0x44A0_0000 | its : 4G)<br>S_AXI Reg 0x4000_0000 64K <del>~</del><br>S_AXI Reg 0x4080_0000 64K <del>~</del><br>S_AXI Reg 0x4480_0000 64K <del>~</del> |

# Wilga

### Vendor tools - summary

- Well integrated with GUI

- Intuitive user interface

- Automatic assignment of addresses

(ロ) (同) (ヨ) (ヨ) (

### Vendor tools - summary

- Well integrated with GUI

- Intuitive user interface

- Automatic assignment of addresses

- Poor support for parametrized number of blocks

・同・イヨト・ヨト

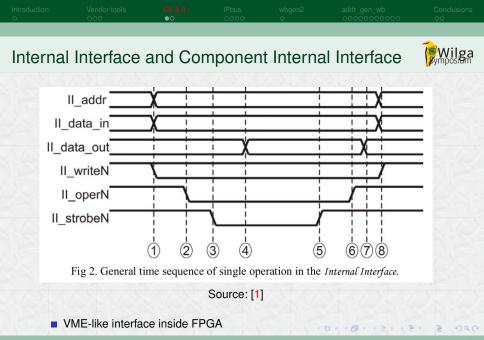

### Internal Interface and Component Internal Interface

Sophisticated solution resulting in complex FPGA logic, not Open Source

|  | ●000 |  |  |

|--|------|--|--|

|  |      |  |  |

### IPbus addressing scheme

- IPbus is well established standard for Ethernet communication with FPGA-based systems

- It is fully Open Sourced

- It uses nice XML tables for defining addresses of slaves

- There are software libraries for Python and C++

```

<node id="crob">

<node id="crob addr ver" address="0x0" permission="r"/>

<node id="sys_ctrl" address="0x200" permission="rw">

<node id="febs mode" mask="0x000000E"/>

</node>

<node id="link mask[0]" address="0x201" permission="rw"/>

<node id="link mask[1]" address="0x202" permission="rw"/>

<node id="ic">

<node id="ctrl" address="0x203" permission="rw">

<node id="reset" mask="0x00000001"/>

<node id="start write" mask="0x00000002"/>

<node id="start read" mask="0x00000004"/>

<node id="addr" mask="0x0000FF00"/>

</node>

<node id="tx rega nbtr" address="0x204" permission="rw">

<node id="reg addr" mask="0x0000FFFF"/>

<node id="bytes_to_read" mask="0xFFFF0000"/>

</node>

<node id="tx data" address="0x205" permission="rw"/>

<node id="status" address="0x1" permission="r">

<node id="ready" mask="0x00000001"/>

<node id="empty" mask="0x00000002"/>

<node id="addr" mask="0x0000FF00"/>

</node>

<node id="rx mptr nbw" address="0x2" permission="r">

<node id="mem ptr" mask="0x0000FFFF"/>

<node id="words read" mask="0xFFFF0000"/>

</node>

<node id="rx data" address="0x3" permission="r"/>

</node>

</node>

(ロ) (部)(さ)(さ)(き))を

```

|  | ●000 |  |  |

|--|------|--|--|

|  |      |  |  |

### IPbus addressing scheme

- IPbus is well established standard for Ethernet communication with FPGA-based systems

- It is fully Open Sourced

- It uses nice XML tables for defining addresses of slaves

- There are software libraries for Python and C++

- Unfortunately, it provides very limited support for automatic generation of address tables

```

<node id="crob">

<node id="crob addr ver" address="0x0" permission="r"/>

<node id="sys ctrl" address="0x200" permission="rw">

<node id="febs mode" mask="0x000000E"/>

</node>

<node id="link mask[0]" address="0x201" permission="rw"/>

<node id="link mask[1]" address="0x202" permission="rw"/>

<node id="ic">

<node id="ctrl" address="0x203" permission="rw">

<node id="reset" mask="0x00000001"/>

<node id="start write" mask="0x00000002"/>

<node id="start read" mask="0x00000004"/>

<node id="addr" mask="0x0000FF00"/>

</node>

<node id="tx rega nbtr" address="0x204" permission="rw">

<node id="reg addr" mask="0x0000FFFF"/>

<node id="bytes to read" mask="0xFFFF0000"/>

</node>

<node id="tx data" address="0x205" permission="rw"/>

<node id="status" address="0x1" permission="r">

<node id="ready" mask="0x00000001"/>

<node id="empty" mask="0x00000002"/>

<node id="addr" mask="0x0000FF00"/>

</node>

<node id="rx mptr nbw" address="0x2" permission="r">

<node id="mem ptr" mask="0x0000FFFF"/>

<node id="words read" mask="0xFFFF0000"/>

</node>

<node id="rx data" address="0x3" permission="r"/>

</node>

</node>

(ロ) (部)(さ)(さ)(き))を

```

|  |      |  | Conclusions |

|--|------|--|-------------|

|  | 0000 |  | 00          |

|  |      |  |             |

### IPbus extension - adr\_gen

- To support automatic generation of address maps for IPbus, the "adr\_gen" [3] system was created

- It uses the standard IPbus ipbus\_ctrlreg\_v block which provides vector of control registers and vector of status registers

- Similar block may be also generated for AXI bus instead of IPbus

- The hierarchy of connected blocks and registers is described in Python

- The registers in connected hierarchy of blocks are assigned consecutive addresses (that may result in inefficient decoding)

- The addresses are generated in VHDL package, in IPbus XML and in Python module

```

TOP

+-SREG: top status

+-CREG: svs control

+-CREG: resets

+-N OF A X ABlocks

+-SREG: A_status

+-CREG: A_control

+-N OF I2C SLAVES X I2CBlock

+-CREG: I2C_Config

+-SREG: I2C Status

+-CREG: I2C Command

+-N OF SPI SLAVES X SPIBlock

+-CREG: SPI Config

+-SREG: SPI_Status

+-CREG: SPT TX

+-SREG: SPI_RX

+-N_OF_B x BBlocks

+- N OF CELLS X CREG: Out data

+- N OF CELLS X SREG: In data

+- SREG: B status

+- CREG: B config

```

|  | IPbus<br>○○●○ |  |  |

|--|---------------|--|--|

|  |               |  |  |

### IPbus extension - adr\_gen

### #!/usr/bin/python3 ("i2c command", creq def), from addr gen import #Definitions of constants used in the package #Define registers and subblocks in the ABlock c.ADDR VERSION=int(time.time()) abl def=aobi("ABLOCK",[ c.N OF A = 13("a status", creg def), c.N OF I2C SLAVES = 6 ("a control", creg def, 2), C.N OF SPI SLAVES = 8 ("spi", spi\_def, c.N\_OF\_SPI\_SLAVES), c.N OF B = 5("i2c", spi def.c.N OF I2C SLAVES), c.N OF CELLS = 12 #Define registers in the BBlock #Define registers and subblocks in the TOP block bbl def=aobj("BBLOCK",[ top def=aobj("TOP",[ ("out data", sreg def.c.N OF CELLS), ("addr ver", sreg def), ("in data", sreg def.c.N OF CELLS). ("top st", sreg def), ("sys ctrl", sreq def), ("resets", creg def).

```

#Define registers in SPI block

spi_def=abj("SPI",[

("spi_config".creg_def),

("spi_status",sreg_def),

("spi_tx".creg_def),

("spi_tx".sreg_def),

])

```

```

#Define registers in I2C block

i2c_def=aobj("I2C",[

("i2c_config",creg_def),

("i2c_status",sreg_def),

```

("ab", abl\_def, c.N\_OF\_A),

("bb", bbl def, c.N OF B),

#Generate package with constants

gen\_vhdl\_const\_package("top\_const\_pkg")

#Generate package with types and addresses

gen\_vhdl\_addr\_package("top\_adr\_pkg","",crob\_def,0,0)

イロン イポン イヨン トラン ヨ

#Generate Python module with addresses

gen\_python\_addr\_module("top\_adr",crob\_def,0,0)

|  | 0000 |  |  |

|--|------|--|--|

|  |      |  |  |

### IPbus extension - adr\_gen

## Wilga

### VHDL code with type definitions

```

type T_12C_CTRL is record

i2c_config : std_logic_vector(31 downto 0);

i2c_command : std_logic_vector(31 downto 0);

end record T_12C_CTRL;

type T_12C_CTRL_ARR is array(natural range(>)

of T_12C_CTRL;

```

```

type T_SPI_CTRL is record

spi_config : std_logic_vector(31 downto 0);

spi_command : std_logic_vector(31 downto 0);

end record T_SPI_CTRL;

type T_SPI_CTRL, ARR is array(natural range())

of T SPI CTRL;

```

type T\_ABL\_CTRL is record a\_control: std\_logic\_vector(31 downto 0); spi : T\_SPI\_CTRL\_ARR(0 to N\_OF\_SPI\_SLAVES-1); i2c : T\_I2C\_CTRL\_ARR(0 to N\_OF\_I2C\_SLAVES-1); end record T\_ABL\_CTRL;

### VHDL code for connecting registers

```

-- Process for connecting the signals

process (all) is

begin -- process

stat reg(tad addr.addr ver) <=

std logic vector(to unsigned(32, ADDR VERSION));

stat_reg(tad_addr.top_st) <= s_top_status;</pre>

s top control <= ctrl reg(tad addr.sys ctrl);

s resets <= ctrl reg(tad addr.resets);

for an in 0 to N OF A-1 loop

stat reg(tad addr.ab(an).a status) <=s a stat(an).a status;</pre>

s a ctrl(an) <= ctrl reg(tad addr.ab(an).a control);</pre>

for spin in 0 to N OF SPI SLAVES loop

s a ctrl(an).spi(spin).spi config <=

ctrl_reg(tad_addr.ab(an).spi(spin).spi_config;

stat reg(tad addr.ab(an).spi(spin).spi status) <=</pre>

s a stat(an).spi(spin).spi status;

s_a_ctrl(an).spi(spin).spi_command <=</pre>

ctrl reg(tad addr.ab(an).spi(spin).spi command;

end loop: -- spin

end loop; -- an

-- Similar loop for B Blocks

end process;

```

イロン (部) (ヨ) (ヨ)/ヨ

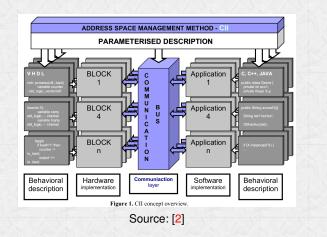

### Wishbone slave generator (wbgen2)

- It is fully Open Source (written in lua)

- Uses C-like description of the peripheral

- Generates the HDL (VHDL/Verilog) code for FPGA

- Generates the C headers to access registers

- Generates very nice documentation in LATEX, texinfo or HTML

### Wishbone slave generator (wbgen2)

- It is fully Open Source (written in lua)

- Uses C-like description of the peripheral

- Generates the HDL (VHDL/Verilog) code for FPGA

- Generates the C headers to access registers

- Generates very nice documentation in LATEX, texinfo or HTML

- Unfortunately, it does not handle vectors of registers and hierarchy of blocks

(ロ) (母) (ヨ) (ヨ)/ ヨ

|  |  | <mark>addr_gen_wb</mark><br>●○○○○○○○○○○ |  |

|--|--|-----------------------------------------|--|

|  |  |                                         |  |

|  |  |                                         |  |

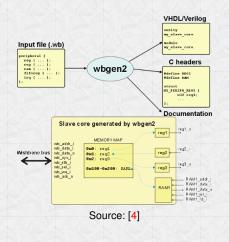

- All existing solutions had certain limitations

- It appeared that none of them may be easily extended for our needs

- It was necessary to create a new system

- The aim was to combine the best features of the existing solutions

同トイラトイラト

### addr\_gen\_wb selection of the bus

- The solution was inspired by wbgen2

- Wishbone bus is a standard Open Source internal bus for FPGA-based system

- IPbus slaves may be controlled by Wishbone bus

- IPbus masters may control Wishbone bus in classic single mode

- There are bridges enabling control of Wishbone bus from AXI masters

- Therefore Wishbone bus (WB) was selected as an FPGA internel bus

イロン (部) (ヨ) (ヨ)/ヨ

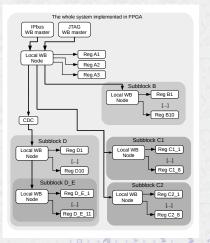

### addr\_gen\_wb structure of created system

- It is possible to describe complex multilevel hierarchical system

- It is possible to create vectors of registers and blocks

- The external control connections in each block are limited to two records

- The internal control interface (Local WB node) for each node is automatically generated

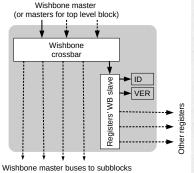

### addr\_gen\_wb local WB node

- The local WB node includes standard WB crossbar

- It is possible to implement crossbar in registered mode to shorten critical path (at cost of increased latency)

(ロ) (部)(さ)(さ)(き))を

(one array for each vector of subblocks)

| Introduction<br>O                                                                                                                                                                  | Vendor tools                                                                                                | CII & II<br>00                                        | IPbus<br>0000    | wbgen2<br>O     | <mark>addr_gen_wb</mark><br>oooo●oooooo | Conclusions        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|-----------------|-----------------------------------------|--------------------|

|                                                                                                                                                                                    |                                                                                                             |                                                       |                  |                 |                                         |                    |

| addr_ge                                                                                                                                                                            | en_wb sys                                                                                                   | stem des                                              | cription         |                 |                                         | Wilga<br>Symposium |

|                                                                                                                                                                                    | The system is c                                                                                             | lescribed wi                                          | th XML file:     | 6               |                                         |                    |

| <creg<br><fie< th=""><th>name="SYS1"&gt;<br/>name="CTRL" desc="Co<br/>eld name="START" widt</th><td>h="1"/&gt;</td><td>tb="1"&gt;</td><td></td><td></td><td></td></fie<></creg<br> | name="SYS1"><br>name="CTRL" desc="Co<br>eld name="START" widt                                               | h="1"/>                                               | tb="1">          |                 |                                         |                    |

| <sreg<br><creg< th=""><th>name="STATUS" desc="<br/>name="ENABLEs" desc=</th><td>Status register"</td><td></td><td>default="0x0"/3</td><td></td><td></td></creg<></sreg<br>         | name="STATUS" desc="<br>name="ENABLEs" desc=                                                                | Status register"                                      |                  | default="0x0"/3 |                                         |                    |

| <subbl< th=""><th>name="MAIN"&gt;<br/>lock name="LINKS" typ</th><td></td><td></td><td></td><td></td><td></td></subbl<>                                                             | name="MAIN"><br>lock name="LINKS" typ                                                                       |                                                       |                  |                 |                                         |                    |

| <pre><sreg <creg="" <fie<="" pre=""></sreg></pre>                                                                                                                                  | <pre>cbox name="EXTERN" ty<br/>name="INS" desc="Inp<br/>name="CTRL" desc="Co<br/>ld name="CLK_ENABLE"</pre> | ut registers" rep<br>ntrol register in<br>width="1"/> | s="2" ack="1" /> | 1               | stb="1">                                |                    |

|                                                                                                                                                                                    |                                                                                                             |                                                       |                  |                 |                                         |                    |

| <th>f&gt;</th> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                   | f>                                                                                                          |                                                       |                  |                 |                                         |                    |

|                                                                                                                                                                                    |                                                                                                             |                                                       |                  |                 |                                         |                    |

900 E + E + E + E + 000

|  |  | addr_gen_wb<br>○○○○○●○○○○○ |  |

|--|--|----------------------------|--|

|  |  |                            |  |

### addr\_gen\_wb VHDL package

For registers with bitfields, the VHDL package with complex data types is generated

```

package body MAIN wb pkg is

library ieee;

use ieee.std logic 1164.all;

function stlv2t CTRL(x : std logic vector) return t CTRL is

use ieee.numeric std.all;

variable res : t CTRL;

library work:

begin

use work.wishbone pkg.all;

res.CLK ENABLE := std logic vector(x(0 downto 0));

res.CLK FREQ := std logic vector(x(4 downto 1));

package MAIN wb pkg is

res.PLL RESET := std logic vector(x(5 downto 5));

return res:

subtype t INS is std logic vector (31 downto 0);

end stlv2t CTRL:

type t INS array is array(0 to 1) of t INS;

function t CTRL2stlv(x : t CTRL) return std logic vector is

type t CTRL is record

variable res : std logic vector(31 downto 0);

CLK ENABLE: std logic vector (0 downto 0);

begin

CLK FREQ:std logic vector (3 downto 0);

res := (others => '0');

res(0 downto 0) := std logic vector(x.CLK ENABLE);

PLL RESET: std logic vector (0 downto 0);

end record;

res(4 downto 1) := std logic vector(x.CLK FREO);

res (5 downto 5) := std logic vector (x.PLL RESET);

function stlv2t CTRL(x : std logic vector) return t CTRL;

return res;

function t CTRL2stlv(x : t CTRL) return std logic vector;

end t CTRL2stlv;

end MAIN wb pkg;

end MAIN wb pkg;

```

イロン (部) (ヨ) (ヨ)/ヨ

|                                                                                       | Vendor tools                             | CII & II<br>00                                                                            | IPbus<br>0000                   | wbgen2<br>O | addr_gen_wb<br>○○○○○●○○○○ | Conclusions |

|---------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------|-------------|---------------------------|-------------|

|                                                                                       |                                          |                                                                                           |                                 |             |                           |             |

| addr_ge                                                                               | en_wb VH                                 | DL for lo                                                                                 | ocal WE                         | 3 node      |                           | Wilga       |

| use ieee<br>library<br>use work                                                       | e.std_logic_1164.a<br>e.numeric_std.all; | ;                                                                                         |                                 |             |                           |             |

| entity M                                                                              | MAIN_wb is                               |                                                                                           |                                 |             |                           |             |

| port (<br>slave<br>EXTER<br>EXTER<br>LINKS<br>LINKS<br>INS_I<br>CTRL<br>CTRL<br>rst_r |                                          | _slave_out;<br>shbone_master_out_<br>hbone_master_out_<br>oone_master_out_<br>ic;<br>gic; | rray(0 to 2);<br>array(0 to 4); |             |                           |             |

| end MAIN<br>[<br>(Imp.                                                                |                                          | entity is omi                                                                             | itted)                          |             |                           |             |

|                                                                                       |                                          |                                                                                           |                                 |             |                           | 5 E 990     |

# Wilga

### addr\_gen\_wb algorithm for address allocation

- The algorithm starts from the most nested blocks

- For each block required number of addresses N is calculated from the number of its registers

- The power of 2  $2^{K} \ge N$  is found. *K* is the number of address bits required by the block

- For the parent block the required number of addresses is calculated basing on the number of its registers and requirements (2<sup>K</sup>) of the child blocks.

- The blocks are sorted in the order of decreasing number of addresses.

- The based addresses are assigned starting from address 0. Each 2<sup>M</sup> group of addresses is aligned to the 2<sup>M</sup> boundary. That simplifies address decoders.

- In the parent blocks the addresses for child blocks are allocated in the same way, starting from the base address of the parent.

(ロ) (日) (日) (日) (日)

| addr_gen_wb IPbus compatible address table |

|--------------------------------------------|

|--------------------------------------------|

| <node id="MAIN"></node>                                                                         |

|-------------------------------------------------------------------------------------------------|

| <pre><node address="0x00000000" id="EXTERN[0]" module="file://EXTERN_address.xml"></node></pre> |

| <pre><node address="0x00000400" id="EXTERN[1]" module="file://EXTERN_address.xml"></node></pre> |

| <pre><node address="0x00000800" id="EXTERN[2]" module="file://EXTERN_address.xml"></node></pre> |

| <pre><node address="0x00001000" id="LINKS[0]" module="file://SYS1_address.xml"></node></pre>    |

| <pre><node address="0x00001010" id="LINKS[1]" module="file://SYS1_address.xml"></node></pre>    |

| <pre><node address="0x00001020" id="LINKS[2]" module="file://SYS1_address.xml"></node></pre>    |

| <pre><node address="0x00001030" id="LINKS[3]" module="file://SYS1_address.xml"></node></pre>    |

| <pre><node address="0x00001040" id="LINKS[4]" module="file://SYS1_address.xml"></node></pre>    |

| <node address="0x00001080" id="ID" permission="r"></node>                                       |

| <node address="0x00001081" id="VER" permission="r"></node>                                      |

| <node address="0x00001082" id="INS[0]" permission="r"></node>                                   |

| <node address="0x00001083" id="INS[1]" permission="r"></node>                                   |

| <node address="0x00001084" id="CTRL" permission="rw"></node>                                    |

| <node id="CLK_ENABLE" mask="0x00000001"></node>                                                 |

| <node id="CLK_FREQ" mask="0x0000001e"></node>                                                   |

| <node id="PLL_RESET" mask="0x00000020"></node>                                                  |

|                                                                                                 |

|                                                                                                 |

</node>

|  |  | <mark>addr_gen_wb</mark><br>⊙⊙⊙⊙⊙⊙⊙⊙⊙●⊙ |  |

|--|--|-----------------------------------------|--|

|  |  |                                         |  |

|  |  |                                         |  |

### addr\_gen\_wb Forth compatible address table

| : | <b>%/</b> \$0 ;                                |

|---|------------------------------------------------|

| : | %/#EXTERN %/ \$0 + swap \$400 * + ;            |

| : | %/#LINKS %/ \$1000 + swap \$10 * + ;           |

| : | <pre>%/#LINKS_ID %/#LINKS \$0 + ;</pre>        |

| : | %/#LINKS_VER %/#LINKS \$1 + ;                  |

| : | %/#LINKS_CTRL %/#LINKS \$2 + ;                 |

| : | %/#LINKS_CTRL.START %/#LINKS_CTRL \$1 \$0 ;    |

| : | %/#LINKS_CTRL.STOP %/#LINKS_CTRL \$2 \$1 ;     |

| : | %/#LINKS_STATUS %/#LINKS \$3 + ;               |

| : | %/#LINKS#ENABLEs %/#LINKS + \$4 + ;            |

| : | %/_ID %/ \$1080 + ;                            |

| : | %/_VER %/ \$1081 + ;                           |

| : | %/#INS %/ + \$1082 + ;                         |

| : | %/_CTRL %/ \$1084 + ;                          |

| : | %/_CTRL.CLK_ENABLE %/_CTRL \$1 \$0 ;           |

| : | <pre>%/_CTRL.CLK_FREQ %/_CTRL \$1e \$1 ;</pre> |

| : | %/_CTRL.PLL_RESET %/_CTRL \$20 \$5 ;           |

### addr\_gen\_wb - latest extensions

The system is intensively developed and certain extensions were added after the preparation of the SPIE paper:

- Possibility to include XML files (with special <!- include path/to/file.xml -> metacomment)

- Possibility to define constants and use expressions inside of the system definition

```

<sysdef top="MAIN">

<constant name="NEXTERNS" val="4" />

<constant name="NSEL BITS" val="3" />

<constant name="NSEL MAX" val="(1 &lt; &lt; NSEL BITS)-1" />

<!-- include block1.xml -->

<block name="MAIN">

<subblock name="LINKS" type="SYS1" reps="NSEL MAX+1"/>

<blackbox name="EXTERN" type="EXTTEST" addrbits="10" reps="NEXTERNS" />

<creg name="CTRL" desc="Control register in the main block" default="0x11">

<field name="CLK ENABLE" width="NSEL BITS"/>

<field name="CLK FREQ" width="4"/>

<field name="PLL RESET" width="1"/>

</creg>

</block>

</svsdef>

(日) (日) (日) (日) (日) (日)

```

|  |  |  | Conclusions<br>●○ |

|--|--|--|-------------------|

|  |  |  |                   |

- addr\_gen\_wb supports automated allocation of the addresses for registers in the complex, hierarchical data processing systems implemented in the FPGA.

- addr\_gen\_wb automatically generates VHDL code needed to provide Wishbone bus connectivity for nested blocks.

- It is possible to create vectors of registers or blocks.

- For registers with bitfields the VHDL record types and conversion functions are automatically created.

- addr\_gen\_wb supports parameterized definition of the system.

|  |  |  | Conclusions<br>●○ |

|--|--|--|-------------------|

|  |  |  |                   |

- addr\_gen\_wb supports automated allocation of the addresses for registers in the complex, hierarchical data processing systems implemented in the FPGA.

- addr\_gen\_wb automatically generates VHDL code needed to provide Wishbone bus connectivity for nested blocks.

- It is possible to create vectors of registers or blocks.

- For registers with bitfields the VHDL record types and conversion functions are automatically created.

- addr\_gen\_wb supports parameterized definition of the system.

- The blocks comprising the system are well isolated regarding their interconnection with the control bus. That facilitates development and maintaining of systems assembled from blocks developed different teams independently. That's an essential feature in electronics created e.g., for High Energy Physics experiments.

(ロ) (日) (日) (日) (日)

|  |  |  | Conclusions<br>●○ |

|--|--|--|-------------------|

|  |  |  |                   |

- addr\_gen\_wb supports automated allocation of the addresses for registers in the complex, hierarchical data processing systems implemented in the FPGA.

- addr\_gen\_wb automatically generates VHDL code needed to provide Wishbone bus connectivity for nested blocks.

- It is possible to create vectors of registers or blocks.

- For registers with bitfields the VHDL record types and conversion functions are automatically created.

- addr\_gen\_wb supports parameterized definition of the system.

- The blocks comprising the system are well isolated regarding their interconnection with the control bus. That facilitates development and maintaining of systems assembled from blocks developed different teams independently. That's an essential feature in electronics created e.g., for High Energy Physics experiments.

- addr\_gen\_wb has been successfully used in the development of FPGA firmware for the GBTX emulator for CBM experiment. It is also planned as a tool to integrate various blocks in the future CRI firmware for the CBM experiment.

イロン(日)(日)(日)(日)

|  |  |  | Conclusions<br>●○ |

|--|--|--|-------------------|

|  |  |  |                   |

- addr\_gen\_wb supports automated allocation of the addresses for registers in the complex, hierarchical data processing systems implemented in the FPGA.

- addr\_gen\_wb automatically generates VHDL code needed to provide Wishbone bus connectivity for nested blocks.

- It is possible to create vectors of registers or blocks.

- For registers with bitfields the VHDL record types and conversion functions are automatically created.

- addr\_gen\_wb supports parameterized definition of the system.

- The blocks comprising the system are well isolated regarding their interconnection with the control bus. That facilitates development and maintaining of systems assembled from blocks developed different teams independently. That's an essential feature in electronics created e.g., for High Energy Physics experiments.

- addr\_gen\_wb has been successfully used in the development of FPGA firmware for the GBTX emulator for CBM experiment. It is also planned as a tool to integrate various blocks in the future CRI firmware for the CBM experiment.

- Sources of addr\_gen\_wb are available in the Github repository

https://github.com/wzab/addr\_gen\_wb [5].

(ロ) (日) (日) (日) (日) (日)

|  |  |  | Conclusions |

|--|--|--|-------------|

|  |  |  |             |

## Bibliography

| [1] | Krzysztof T. Poźniak.<br>Internal interface i/o communication with fpga circuits and hardware description standard for applications in hep<br>and fel electronics ver. 1.0, 2005.<br>Available from the website<br>https://flash.desy.de/reports_publications/tesla_reports/tesla_reports_2005/. |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2] | Pawel Drabik and Krzysztof T. Pozniak.                                                                                                                                                                                                                                                           |

|     | Maintaining complex and distributed measurement systems with component internal interface framework.<br>In Ryszard S. Romaniuk and Krzysztof S. Kulpa, editors, <i>Proc. SPIE</i> , volume 7502, page 75022C, Wilga, Poland, June 2009.                                                          |

| [3] | Adr_gen - automatic address generator.<br>https://github.com/wzab/wzab-hdl-library/tree/master/addr_gen.                                                                                                                                                                                         |

| [4] | Wishbone slave generator.                                                                                                                                                                                                                                                                        |

|     | https://www.ohwr.org/project/wishbone-gen.                                                                                                                                                                                                                                                       |

| [5] | Wojciech M. Zabołotny.                                                                                                                                                                                                                                                                           |

|     | adr_gen_wb.py - register access for hierarchical wishbone connected systems, 2017.<br>https://github.com/wzab/addr_gen_wb.                                                                                                                                                                       |

・ロン・日ン・ヨン・ヨン/ヨ