## Noise Performance Analysis for the Silicon Tracking System Detector and Front-End Electronics

Weronika Zubrzycka, Krzysztof Kasiński

zubrzycka@agh.edu.pl, kasinski@agh.edu.pl

Department of Measurement and Electronics AGH University of Science and Technology, Cracow, Poland

XLII-nd IEEE-SPIE Joint Symposium Wilga 2018 2018.06.05

This work was funded by Ministry of Science and Higher Education Poland, from the scientific budget in years 2016-2019 – a research project in the programme "Diamentowy Grant".

## Agenda

- Brief intro: Silicon Tracking System in the CBM experiment.

- Motivation.

- Sources of noise in a detection system.

- Impact of shaping amplifiers and preamplifier on noise.

- Noise reduction options.

- MiniASIC architecture proposals.

- Summary.

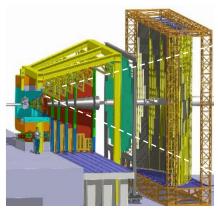

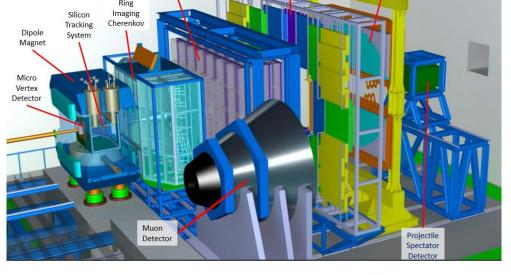

## CBM experiment, GSI, Darmstadt, Germany

**CBM**

**Aim:** creation of the highest baryon densities in nucleus-nucleus collisions for the exploration of the properties of the superdense nuclear matter. Exploration of the QCD phase diagram in the region of very high baryon densities

Radiation Detector

#### STS metrics:

>1 790 000 channels >14 000 ASICs 1752 FEBs 600 ROBs 78 DPBs

#### STS (Silicon Tracking System) detector

Particles' track and momentum determination Interaction rate 10 MHz Silicon strip detectors

Time of Flight

MUCH (Muon Chamber) detector

Gaseous detector (GEM)

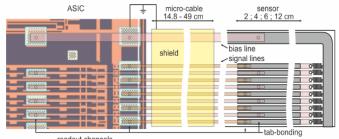

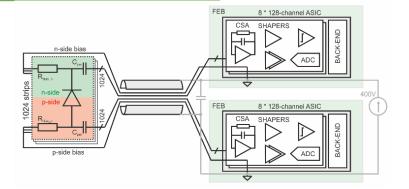

**Read-out electronics** at the perimeter of the detection stations (FEB: 8 chips/board) + data concentrator (based on GBTx)

multi-line micro-cables-> sensors' read-out

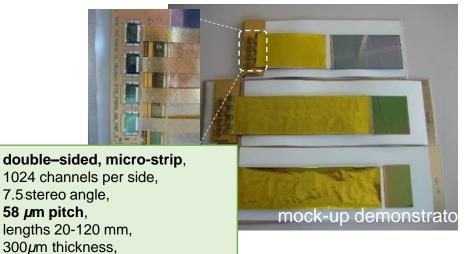

double—sided, micro-strip sensors,1024 CH/side, 7.5° stereo angle, **58 µm** strip pitch

**EMCAL**

## STS system overview

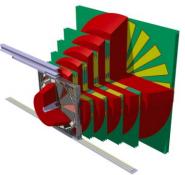

#### **Read-out electronics**

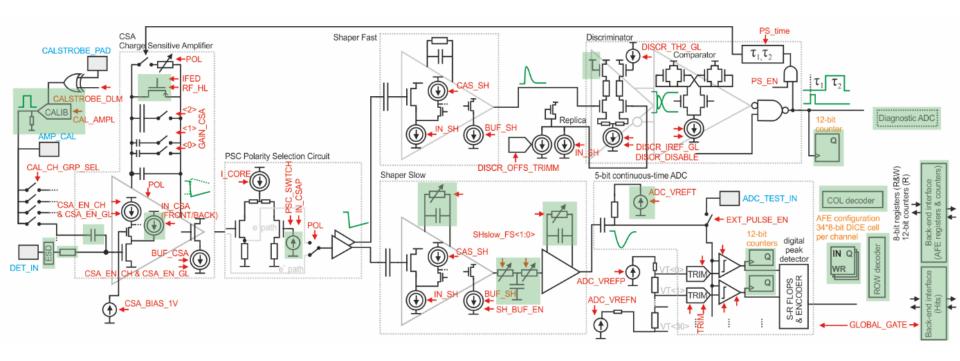

#### The STS/MUCH-XYTER2 (SMX2):

- developed at AGH University Cracow

- 10 mm × 6.8 mm, 288 pads

- 128 readout channels + 2 test channels

- Power: 1.1 1.3 W per chip

- 5-bit continuous-time ADC + 14-bit Timestamp

- Range of operation: 0-15 fC (STS)

- 250 kHit/s/channel (fast reset enabled)

- 9.41-47 Mhit/s/chip

#### Total ENC: < 1000 e<sup>-</sup> rms in system

Power: <10 mW / channel

CSA gain: 10 mV/fC SH\_slow gain: 35 mV/fC SH\_fast gain: 75 mV/fC

Peaking time (slow path): 90 ns Peaking time (fast path): 40 ns

#### **Sensor and micro-cable**

readout channels with staggered input pads

#### **FEB (Front-end Board):**

8 ASICs - read-out of a single side of 1024 strip sensor Rad-hard LDOs (VECC India) AC-coupling of SLVS e-links

## Motivation

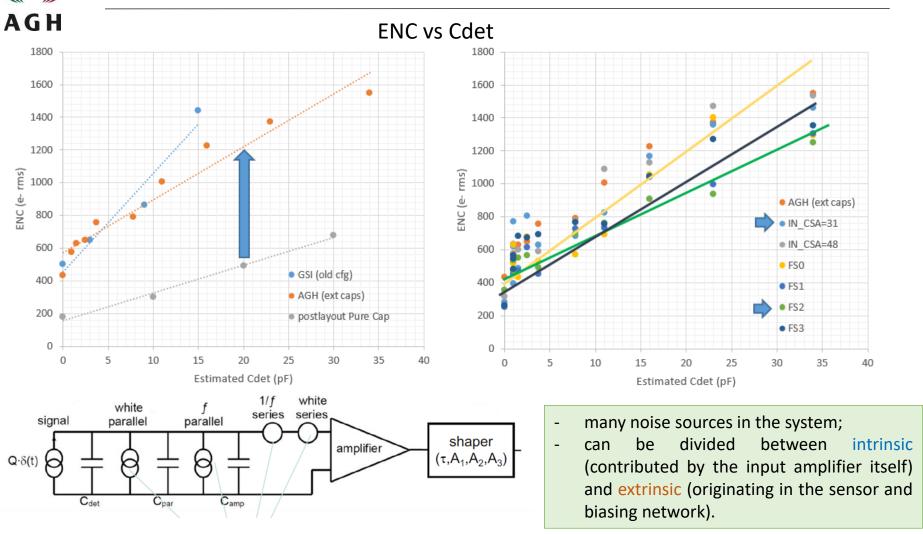

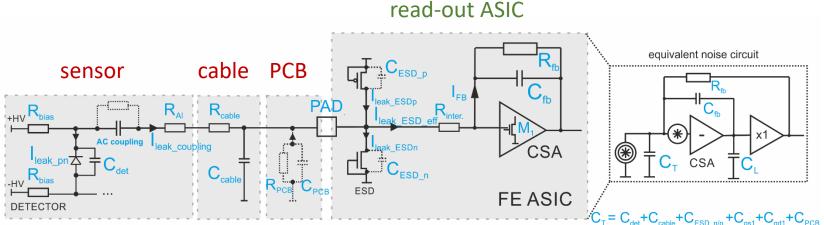

## Noise sources in the detection system

#### 1. parallel current noise:

- detector leakage current shot noise (I<sub>L</sub>),

- detector bias shunt resistance R<sub>bias</sub>,

- leakage current flowing through transistors in the Electrostatic Discharge (ESD) protection circuit,

- current thermal noise from feedback resistance.

#### 2. series white noise:

- input transistor thermal noise (M1<sub>th</sub>),

- various series resistors' (sensor's metal strip, cable, interconnect on-chip) thermal noise.

#### 3. series 1/f (or flicker) noise:

• CSA input transistor flicker (1/f) noise (M1f).

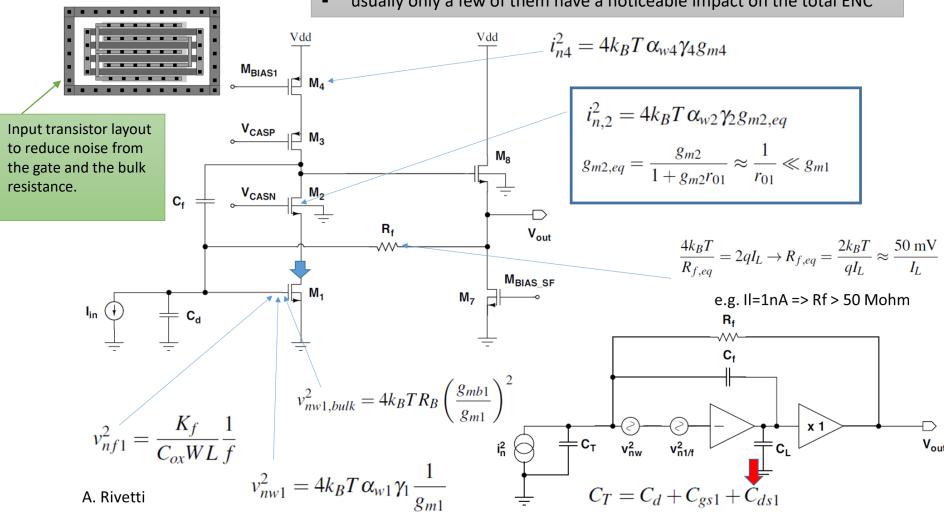

## Noise at CSA output - detailed considerations

- all devices forming the core amplifier and its feedback network contribute to the overall noise,

- usually only a few of them have a noticeable impact on the total ENC

<sup>&</sup>quot;CMOS Front-end Electronics for Radiation Sensors"

## Noise at CSA output - detailed considerations

$$P_{av,out} = \langle y(t)^2 \rangle = \int_{-\infty}^{\infty} S_{xx}(f) |H(f)|^2 df$$

#### Parallel, Current Noise

$$< v_{out}^2 >_{ni} = i_n^2 R_f^2 \int_0^\infty \left| \frac{1}{(1 + s\tau_f)(1 + s\tau_r)} \right|^2 df$$

$$\int_0^\infty \left| \frac{1}{\left(1 + s\tau_f\right)\left(1 + s\tau_r\right)} \right|^2 df = \frac{1}{4\left(\tau_f + \tau_r\right)} \approx \frac{1}{4\tau_f}$$

$$< v_{out}^2 >_{ni} = \frac{i_n^2}{4} \frac{R_f}{C_f}$$

$i_n^2 = 2qI_L$   $< v_{out}^2 >_{ni} = \frac{qI_L}{2} \frac{R_f}{C_f}$

$$/(1/C_f^2)$$

$$ENC_i^2 = \frac{i_n^2}{4} \frac{R_f C_f}{q^2} \implies i_n^2 = 2qI_L \implies ENC_i = \sqrt{\frac{I_L \tau_f}{2q}}$$

$$i_n^2 = \frac{4k_B T}{R_f} \implies ENC_i = \frac{1}{q} \sqrt{k_B T C_f}$$

- τ<sub>f</sub> falling time, related to the CSA feedback capacitor discharge time constant

- $\tau_r$  rising time, related to the CSA bandwidth (~40 ns for the CSA GBW ~9 GHz) -> the input of the CSA bandwidth has no strong impact on the ENC

Preferably, the total noise is limited to the one produced by the input transistor. The noise introduced by other devices can be neglected.

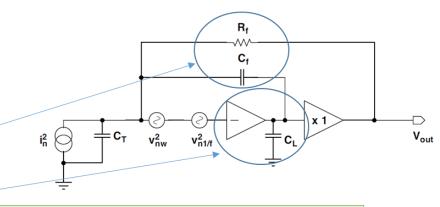

## Noise at CSA output - detailed considerations

Series, Voltage Noise => convert to current by  $v_{nv}^2 s^2 C_T^2$

#### White series

$$< v_{out}^2 >_{nw} = v_{nw}^2 C_T^2 R_f^2 \frac{1}{4R_f^2 C_f^2 \frac{C_T C_L}{g_{m1} C_f}}$$

$$v_{nw1,bulk}^2 = 4k_B T \alpha_{w1} \gamma_1 \frac{1}{g_{m1}}$$

$$v_{nw1}^2 = 4k_B T \alpha_{w1} \gamma_1 \frac{1}{g_{m1}}$$

CSA bandwidth

$< v_{out}^2 >_{nw} = : \gamma k_B T \frac{C_T}{C_f C_L} ENC_w = \frac{1}{q} \sqrt{\gamma k_B T \frac{C_T C_f}{C_L}}$

1/f series noise

$$v_{nf1}^2 = \frac{K_f}{C_{ox}WL} \left(\frac{1}{f}\right)$$

$$\int_{0}^{\infty} \left| \frac{j2\pi f}{\left(1 + j2\pi f \tau_{f}\right)\left(1 + j2\pi f \tau_{r}\right)} \right|^{2} df = \frac{1}{4\tau_{f}\tau_{r}\left(\tau_{f} + \tau_{r}\right)} \approx \frac{1}{4\tau_{f}^{2}\tau_{r}} \right| < v_{out}^{2} >_{nf} = \frac{K_{f}}{C_{ox}W_{1}L_{1}} C_{T}^{2} R_{f}^{2} \int_{0}^{\infty} \frac{1}{f} \frac{j2\pi f}{\left(1 + j2\pi f \tau_{f}\right)\left(1 + j2\pi f \tau_{r}\right)} \right|^{2} df$$

$$\int_0^\infty \frac{1}{f} \left| \frac{j2\pi f}{\left(1 + j2\pi f \tau_f\right) \left(1 + j2\pi f \tau_r\right)} \right|^2 df = \left( \frac{\ln\left(\frac{\tau_r}{\tau_f}\right)}{\tau_r^2 - \tau_f^2} \right) \approx \frac{1}{\tau_f^2} \ln\left(\frac{\tau_f}{\tau_r}\right)$$

$$v_{nw1,bulk}^{2} = 4k_{B}TR_{B} \left(\frac{g_{mb1}}{g_{m1}}\right)^{2} < v_{out}^{2} >_{nf} = \frac{K_{f}}{C_{ox}W_{1}L_{1}} \frac{C_{T}^{2}}{C_{f}^{2}} \ln \left(R_{f}C_{f} \frac{g_{m1}C_{f}}{C_{T}C_{L}}\right)$$

$$ENC_f = \frac{C_T}{q} \sqrt{\frac{K_f}{C_{ox}W_1L_1}} \sqrt{\ln\left(R_f C_f \frac{g_{m1}C_f}{C_T C_L}\right)}$$

- CSA output noise related to input in ENC is strongly dependent on the CSA transfer function

- The noise spectral density at CSA output is dependent on the total input capacitance (including detector capacitance), feedback capacitance and CSA load capacitance.

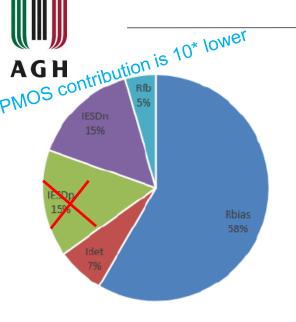

## Noise contributors

| Source       | Typ. value                        | Used for calc.              |

|--------------|-----------------------------------|-----------------------------|

| $R_{bias}$   | $500 \ k\Omega$ - $1.5 \ M\Omega$ | $1.5 M\Omega$               |

| $I_{det}$    | 1 - 8  nA/cm                      | 4 nA                        |

| $I_{ESDn}$   | 1 - 10  nA                        | 9 nA                        |

| $I_{ESDp}$   | 1 - 10  nA                        | 9 nA                        |

| $R_{fb}$     | $5M\Omega$ - $30M\Omega$          | $20~M\Omega$                |

| $R_{Al}$     | $10.5 \Omega/cm$                  | 42 Ω                        |

| $R_{cable}$  | $0.635 \Omega/cm$                 | 12.7 Ω                      |

| $R_{inter.}$ | 10 Ω - 25 Ω                       | 15 Ω                        |

| $M_{1,th}$   | Tech. dep.                        | $\alpha = 0.5, \gamma = 1,$ |

|              |                                   | $g_m$ =0.044 $A/V$          |

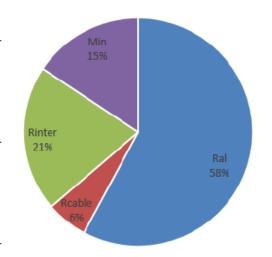

Figure 1: Components of the current noise.

Figure 2: Components of the voltage noise.

$$i_n^2 = \frac{4k_BT}{R} + \frac{4k_BT}{R} + 2qI_{det} + 2qI_{ESDn} + 2qI_{ESDp}$$

$$i_n^2 = \frac{4k_BT}{R_{bias}} + \frac{4k_BT}{R_{EB}} + 2qI_{det} + 2qI_{ESDn} + 2qI_{ESDp} \qquad v_{nw}^2 = 4k_BTR_{Al} + \frac{4}{3}k_BTR_{cable} + 4k_BTR_{inter} + 4k_BT\alpha_w\gamma^{-1}/g_m$$

Input transistor flicker noise

$$v_{nf}^2 = \frac{k_f}{c_{ox}WLf}$$

Total noise at shaper's output:

$$ENC^{2} = ENC_{i}^{2} + ENC_{w}^{2} + ENC_{1/f}^{2} \rightarrow ENC^{2} = \tau_{p} \cdot A_{i} \cdot i_{n}^{2} + \frac{1}{\tau_{p}} \cdot v_{n}^{2} \cdot A_{w} \cdot C_{T}^{2} + A_{1/f} \cdot v_{nf}^{2} \cdot C_{T}^{2}$$

where Ct is the total capacitance connected to CSA input:  $C_t = C_g + C_{fb} + C_{calib} + C_{DET}$ ,  $A_{w}$ ,  $A_{i}$  and  $A_{1/f}$  are weighting coefficients for thermal, current and flicker noise respectively (depending on the filter type and order) and  $au_p$  is the peaking time.

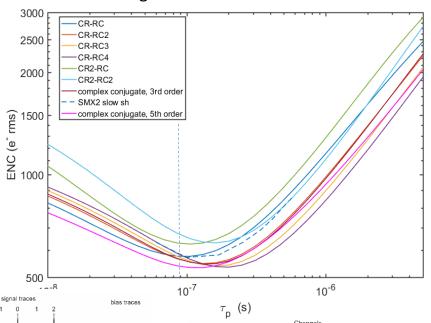

## ENC calculations – shaping amplifier's output

|                                                | $A_{\mathrm{w}}$ | $A_{1/f}$ | $A_i$ |

|------------------------------------------------|------------------|-----------|-------|

| CR-RC                                          | 0.92             | 3.69      | 0.92  |

| CR-RC <sup>2</sup>                             | 0.85             | 3.41      | 0.64  |

| CR-RC <sup>3</sup>                             | 0.93             | 3.32      | 0.52  |

| CR-RC <sup>4</sup>                             | 1.02             | 3.27      | 0.45  |

| CR <sup>2</sup> -RC                            | 1.03             | 4.70      | 1.00  |

| CR <sup>2</sup> -RC <sup>2</sup>               | 1.16             | 4.89      | 0.72  |

| Complex conjugate poles, 3 <sup>rd</sup> order | 0.85             | 3.39      | 0.61  |

| Complex conjugate poles, 5 <sup>th</sup> order | 0.96             | 3.27      | 0.45  |

The total noise at shapre's output containing simplified expressions for each type of noise:

$$ENC^{2} = A_{w} \frac{1}{\tau_{p}} \frac{4kT\gamma}{g_{m}} C_{T}^{2} + A_{f}K_{f}C_{T}^{2} + A_{i}\tau_{p} \left[2q\left(I_{det} + I_{fb}\right) + \frac{4kT}{R_{bias}} + \frac{4kT}{R_{fb}}\right]$$

where  $g_m$  and  $\gamma$  are parameters of the CSA input transistor:

$$g_m = \frac{I_{DS}}{n\varphi_T} f(i_f), f(i_f) = \frac{1}{\sqrt{i_f + 0.5\sqrt{i_f} + 1}}, \gamma = \frac{1}{2} + \frac{1}{6} \frac{i_f}{i_f + 1}$$

#### **Decisions (ASIC):**

- Minimize R<sub>inter</sub> (~50%)

- Remove ESD

#### **Decisions (Sensor):**

- Minimize Al strip resistance

- Maximize R<sub>hias</sub> (>5Mohm)

**ASIC:** Weighting coefficients of filters and peaking time can be used for multi-dimensional ENC minimization based on given conditions.

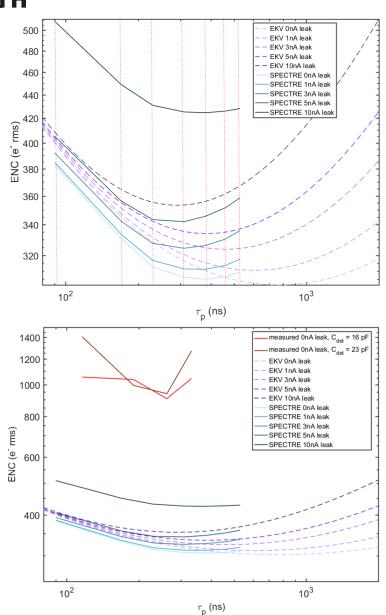

## Results – EKV model and simulations

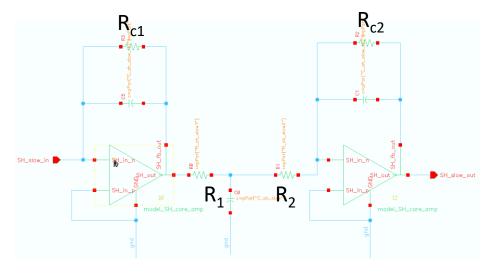

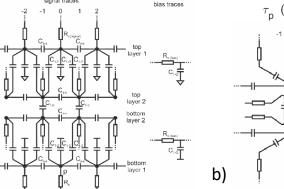

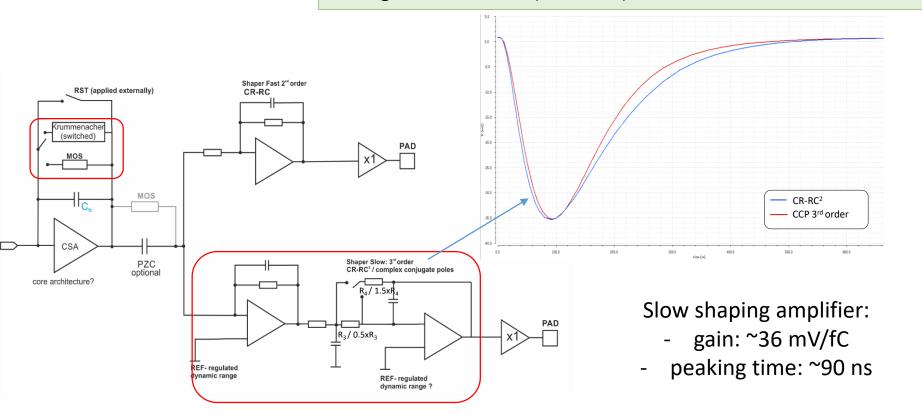

Model of the slow shaper implemented in SMX2 chip.

## CR-RC<sup>2</sup> peaking times

| R <sub>c1,</sub> R <sub>c2</sub> , R <sub>1,</sub> R <sub>2</sub> | t <sub>p</sub> for<br>electrons | t <sub>p</sub> for<br>holes |

|-------------------------------------------------------------------|---------------------------------|-----------------------------|

|                                                                   | (ns)                            | (ns)                        |

| 200k, 45k, 10k, 10k                                               | 90                              | 90                          |

| 400k, 90k, 20k, 20k                                               | 170                             | 170                         |

| 600k, 135k, 30k, 30k                                              | 230                             | 230                         |

| 800k, 180k, 40k, 40k                                              | 310                             | 310                         |

| 1M, 225k, 50k, 50k                                                | 380                             | 390                         |

| 1.2M, 270k, 60k, 60k                                              | 460                             | 460                         |

| 1.4M, 315k, 70k, 70k                                              | 530                             | 530                         |

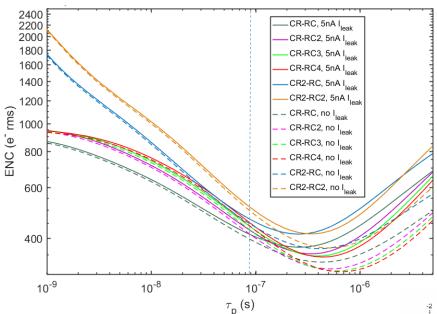

## Simulations results – various shapers architectures

- R<sub>fb</sub> noisy,

- ESD attached,

- pure capacitance (20 pF),

- detector leakage equal to 0 and 5 nA.

Simulation models of a) the cable and b) the double-sided sensor used for simulations; cable length = 49 cm and sensor length = 4 cm.

- R<sub>fb</sub> noisy,

- ESD attached,

- detector model + shunt bias resistances+ interconnect series resistances,

- detector leakage 5 nA.

a)

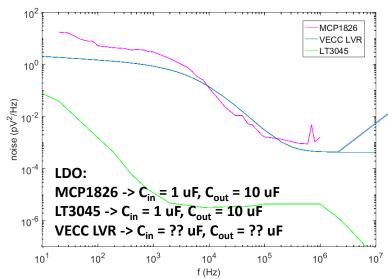

## Simulations results with LDO – various shapers

3000

2800

#### LDO noise model (VECC LVR),

- R<sub>fb</sub> noisy,

- ESD attached,

- detector model (detector length 4 cm, cable length 49 cm),

- interconnect series resistances,

- detector leakage 5 nA.

#### CR-RC 2600 CR-RC2 2400 CR-RC3 2200 CR-RC4 complex conjugate, 3rd order 2000 SMX2 slow sh ENC (e Lms) 1000 1400 complex conjugate, 5th order 1200 1000 800 10<sup>-7</sup> 10<sup>-8</sup> 10<sup>-6</sup> $\tau_{\rm p}$ (s)

ENC (e<sup>-</sup> rms) vs. peaking time

#### **Output Noise Voltage Density vs. Frequency**

According to simulation results power supply lines inside the chip filter the supply noise to only a small excent, which is not noticeable in the output noise level.

## Noise sources – SMX2 chip example

#### **Noise-related changes:**

- Add 3pF decoupling capacitor at PSC reference in each channel

- Fix even/odd problem by adding decoupling pad

- Make sure biasing resistance of sensors is enlarged > 5 Mohm

- Minimize series resistance of pad-to-CSA connection (10, 25 Ohm)

- Remove ESD protection and extend power lines

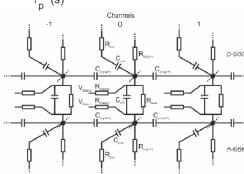

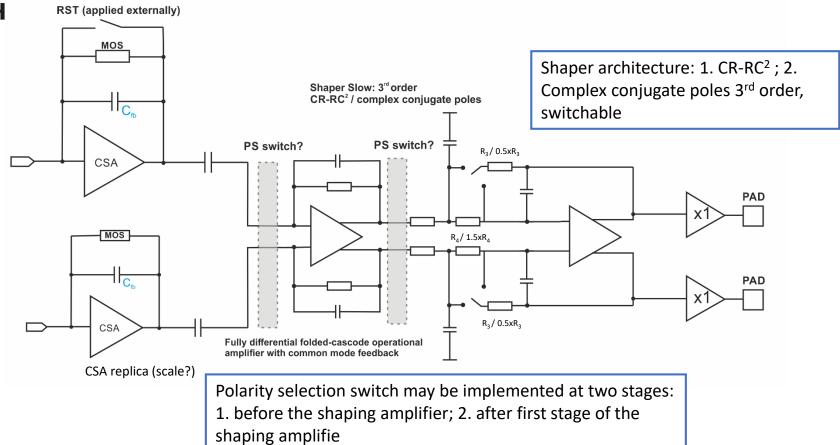

#### New channel architecture

(UMC180, mini@sic, run:july 2018)

# 1.5x1.5 mm6-8 channels4 single-ended, 4 differential digital interface for configuration

#### Key features:

- Eliminate PSC (inverting stage): equalize noise for both polarities

- Switchable shaper architectures:

- Complex conjugate poles (3<sup>rd</sup> order)

- Improved CR-RC<sup>2</sup> architecture

- Pseudo-differential architecture to reject power supply noise and digital interference (next slide)

## Channels' architecture – (pseudo-)differential

Optionally: adding a digital register generating noise to check system immunity to substrate noise induced by digital part switching activity.

Eliminate power supply noise (LDOs contribution quite high!)

### Conclusions

- There are multiple contributors to the total noise of a detection system.

- The total preamplifier input related noise (ENC) depends also on the total input capacitance, peaking time and weighting coefficients (shaping amplifier transfer function).

- Proper selection of the shaping amplifier architecture and peaking time value can decrease the total output noise by a few tens of electrons.

- The more severe effect on the total noise can be attributed to the power supply noise.

- CMRR of the pseudo-differential shaping stage can prove useful in rejecting power supply & digital –related noise sources at the cost of power|noise penalty.

## Thank you for your attention.

zubrzycka@agh.edu.pl, kasinski@agh.edu.pl

This work was funded by Ministry of Science and Higher Education Poland, from the scientific budget in years 2016-2019 – a research project in the programme "Diamentowy Grant".