# Design of Efficient Secure Data Communication Techniques for Reconfigurable Hardware Platform

## Suman Sau A.K.Choudhury School of Information Technology University of Calcutta

A thesis submitted for the degree of  $Doctor\ of\ Philosophy\ (Technology)$  date

#### Acknowledgements

I would like to acknowledge my supervisor, Professor Amlan Chakrabarti, for his guidance and mentorship during the course of this research work. I would also like to thank Dr Subhasis Chattopadhyay, Scientific Officer (H+), Variable Energy Cyclotron Centre, Department of Atomic Energy, Govt of India, Kolkata for his support in helping me to carry out my Ph.D study in Compressed Baryonic Matter-Facility for Antiproton and Ion Research (CBM-FAIR) India group. I sincerely thank all my colleagues in the research lab of A.K. Choudhury School of IT, University of Calcutta and CBM India group.

I would like to express my sincere gratitude towards my mother Niyati Sau, my father Haripada Sau, my brother Sibnarayan Sau and my sisters Nila Sau, Sila Sau and Mala Sau. Their cooperation and encouragement helped me in the completion of this project.

I would like to express my special gratitude and thanks to all the other faculties and staff of A.K. Choudhury School of IT.

Thanks to Sangita Ghosh for her motivation and support during this journey of mine. Finally, thanks to all my friends, mentioned or not mentioned here, for always being there with me whenever asked for.

#### Abstract

We are in the era of emerging and inclusive technologies where data communication plays a pivotal role. The key enablers are high data rate, secured communication and and fault resiliency which can assure both performance and reliability. This dissertation focuses on these key performance parameters for design of efficient data communication techniques with a special motivation towards embedded applications. The design strategies proposed in this thesis though emphasizes on high speed data communication applications, but can also be adopted for general purpose embedded applications through proper customization.

State of the art methodologies for designing efficient data communication systems in embedded platform includes explicit software, explicit hardware and software-hardware co-design approaches. In this dissertation, we have emphasized upon all these approaches and have proposed various design and implementation techniques which can suitably meet the requirements of high speed data communication, data security and error detection and correction policies. Field Programmable Gate Array (FPGA) is a popular choice for implementation of present day embedded systems, as it offers a shorter turnaround time and also provides the scope of hardware reconfigurability (full and partial) along with spatial parallelism in terms of logic operations. We have chosen FPGA as the implementation platform for prototyping the various systems and subsystems designed in the course of this research work. We have successfully designed systems based on embedded processor cores, dedicated hardware logic cores and software hardware co-design involving processor with dedicated hardware logic cores to meet the demands of the various application scenarios briefed in this dissertation.

This dissertation proposes a hardware optimization for some of the important cryptographic functions like exponential modulus of a large key, parallelization of the advanced encryption system (AES) function for speedup and also enhancing the AES hardware core through the incorporation of error detection and correction schemes. In order to validate our design, we have designed and implemented various test setups involving communication links like RS232, Ethernet and optical which can estimate the performance of the designed sub system in terms of real time parameters, security and error resiliency. Apart from developing the suitable hardware infrastructure for efficient data communication applications, in this dissertation we have also proposed a first of its kind dedicated hardware logic core for the implementation of gigabit transceiver (GBT) protocol for inter system communication catering the need of high data rate applications. A new scheme of error handling for FPGA configuration memory has been designed, which exploits Bose, Chaudhuri, Hocquenghem (BCH), modified matrix code (MMC) etc. coding techniques and also utilizes partial reconfiguration methodology for correcting the affected logic during the run time. The novelty of this technique is well justified as it increased the performance of the system in terms latency, speed up and error resiliency. In a nutshell, this dissertation contributes to the sate of the art research in the domain of embedded systems through the various new methodologies and their system level implementations that have been achieved in the due course of this research.

## Contents

| C                         | ontei                | nts     |                                                            | V    |  |

|---------------------------|----------------------|---------|------------------------------------------------------------|------|--|

| $\mathbf{L}_{\mathbf{i}}$ | ist of               | Figure  | es                                                         | ix   |  |

| Li                        | ist of               | Tables  | 5                                                          | xii  |  |

| N                         | omei                 | nclatur | e                                                          | xiii |  |

| 1                         | Inti                 | roducti | ion                                                        | 1    |  |

|                           | 1.1                  | Motiva  | ation and scope of the work                                | 5    |  |

|                           |                      | 1.1.1   | Need of efficient hardware design for secure data communi- |      |  |

|                           |                      |         | cation                                                     | 6    |  |

|                           |                      | 1.1.2   | Cryptographic Algorithms in FPGAs                          | 7    |  |

|                           |                      | 1.1.3   | Need of detection and correction of errors in high speed   |      |  |

|                           |                      |         | secure data communication beyond 1Tb/s                     | 9    |  |

|                           | 1.2                  | Organ   | ization of the Thesis                                      | 10   |  |

| 2                         | $\operatorname{Rel}$ | ated R  | esearch Works                                              | 12   |  |

|                           | 2.1                  | Introd  | $egin{array}{llllllllllllllllllllllllllllllllllll$         | 12   |  |

|                           | 2.2                  | Basics  | of available design platform                               | 13   |  |

|                           |                      | 2.2.1   | Microprocessor and Micro-controller                        | 13   |  |

|                           |                      | 2.2.2   | Application Specific Integrated Circuits (ASICs)           | 13   |  |

|                           |                      | 2.2.3   | Field Programmable Gate Arrays (FPGAs)                     | 14   |  |

|                           |                      | 2.2.4   | FPGA Design Flow                                           | 18   |  |

|                           | 2.3                  | Relate  | ed work                                                    | 19   |  |

|                           |                      | 2.3.1   | Related work in secure communication                       | 20   |  |

|   |                | 2.3.2  | Related work in high speed communication and data acquisition                                                                                  | 22         |

|---|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|   |                | 2.3.3  | Related work on High speed communication with error de-                                                                                        | 22         |

|   |                | 2.0.0  | tection/correction                                                                                                                             | 23         |

| 3 | $\mathbf{Cry}$ | pto A  | lgorithms and its Embedded Processor Based Imple-                                                                                              |            |

|   | men            | tation |                                                                                                                                                | <b>2</b> 8 |

|   | 3.1            | Introd | $ uction \ldots \ldots$ | 29         |

|   | 3.2            | Design | 1 Overview                                                                                                                                     | 30         |

|   |                | 3.2.1  | RSA Algorithm                                                                                                                                  | 31         |

|   | 3.3            | First  | Algorithm for modulus exponentiation operation                                                                                                 | 31         |

|   |                |        | 3.3.0.1 Modular Exponential operation with Binary Method                                                                                       | 34         |

|   |                |        | 3.3.0.2 Description of Binary Method                                                                                                           | 35         |

|   | 3.4            | Embe   | dded Architectural Design                                                                                                                      | 37         |

|   | 3.5            | Hardw  | vare Architectural Design                                                                                                                      | 40         |

|   |                | 3.5.1  | MicroBlaze                                                                                                                                     | 40         |

|   |                | 3.5.2  | Power PC                                                                                                                                       | 40         |

|   |                | 3.5.3  | Microblaze based Hardware Design                                                                                                               | 41         |

|   |                |        | 3.5.3.1 RSA and ECC Single Microblaze                                                                                                          | 42         |

|   | 3.6            | Expe   | riment 1                                                                                                                                       | 42         |

|   | 3.7            | Expe   | riment 2                                                                                                                                       | 43         |

|   | 3.8            | Theore | etical Result                                                                                                                                  | 45         |

|   | 3.9            | Synthe | esis                                                                                                                                           | 46         |

|   | 3.10           | Impler | mentation and Results                                                                                                                          | 46         |

|   | 3.11           | Compa  | arison with Existing Work                                                                                                                      | 47         |

|   |                |        | nary                                                                                                                                           | 49         |

| 4 | Des            | ign of | Crypto Co-processor and its Implementation                                                                                                     | <b>50</b>  |

|   | 4.1            | Introd | uction                                                                                                                                         | 51         |

|   | 4.2            | Basics | of AES algorithm                                                                                                                               | 52         |

|   | 4.3            |        | n Architecture                                                                                                                                 | 54         |

|   |                | 4.3.1  | AES Core Design                                                                                                                                | 55         |

|   |                | 4.3.2  | Implementation of the Microblaze Soft Core Processor                                                                                           | 60         |

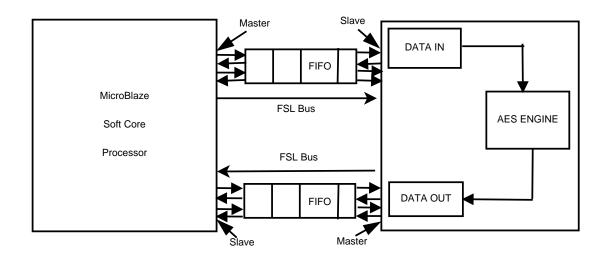

|   |      | 4.3.3 FSL Bus And AES Hardware Engine                           | 61        |

|---|------|-----------------------------------------------------------------|-----------|

|   | 4.4  | System Evaluation                                               | 62        |

|   | 4.5  | Summary                                                         | 68        |

| 5 | Hig  | h Speed Secure Communication System Design using Error          |           |

|   | Det  | ection and Correction Model                                     | <b>69</b> |

|   | 5.1  | Introduction                                                    | 70        |

|   | 5.2  | High speed DAQ design with secure communication for MUCH        |           |

|   |      | experiments                                                     | 72        |

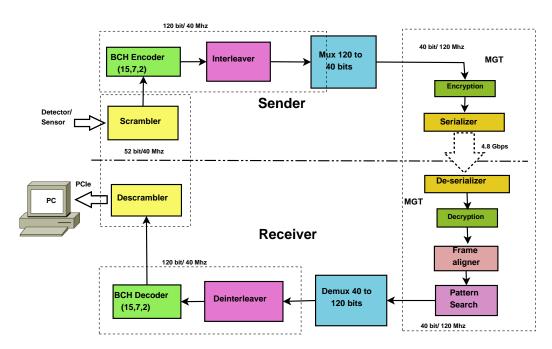

|   |      | 5.2.1 Scrambler/Descrambler                                     | 73        |

|   |      | 5.2.2 BCH Encoder/Decoder                                       | 73        |

|   |      | 5.2.2.1 BCH Coding Theory                                       | 73        |

|   |      | 5.2.2.2 Encoder/Decoder Hardware Block                          | 75        |

|   |      | 5.2.3 Interleaver/De-interleaver                                | 75        |

|   |      | 5.2.4 MUX/DEMUX and Clock Domain Crossing                       | 76        |

|   |      | 5.2.5 Encryption/Decryption                                     | 76        |

|   |      | 5.2.6 Serializer/De-serializer                                  | 77        |

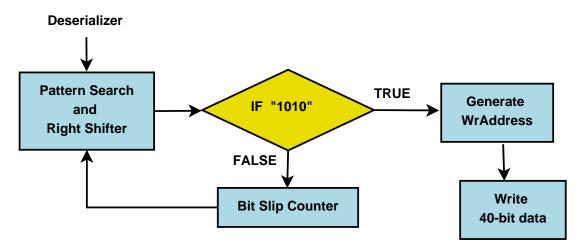

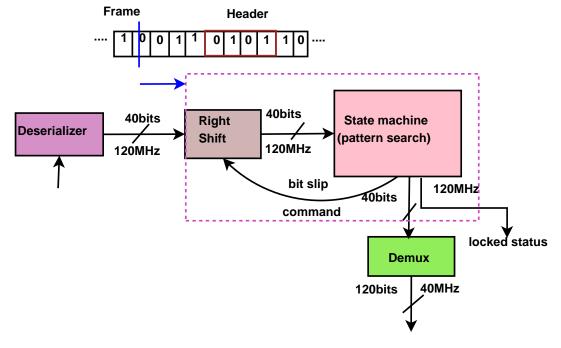

|   |      | 5.2.7 Frame Aligner and Pattern Search                          | 77        |

|   |      | 5.2.8 Data Transfer to back end system through PCIe             | 78        |

|   |      | 5.2.9 Overview of Secure Data Flow                              | 79        |

|   | 5.3  | Experimental Setup and performance                              |           |

|   |      | Analysis                                                        | 81        |

|   | 5.4  | Summary                                                         | 83        |

| 6 | Mu   | lti bit Error Correction Model for Crypto Co-processor Ar-      |           |

|   | chit | ecture                                                          | <b>85</b> |

|   | 6.1  | Introduction                                                    | 86        |

|   | 6.2  | Preliminaries                                                   | 88        |

|   |      | 6.2.1 BCH Coding                                                | 88        |

|   |      | 6.2.2 Multi bit Error Correction Scheme using BCH code          | 88        |

|   | 6.3  | AES Encryption and Decryption with Multibit error detection and |           |

|   |      | correction model                                                | 90        |

|   |      | 6.3.1 First fault model                                         | 90        |

#### CONTENTS

|                           | 6.4<br>6.5 |        | Second fault model                                | . 91<br>. 92<br>. 95<br>. 99 |

|---------------------------|------------|--------|---------------------------------------------------|------------------------------|

| 7                         | Soft       | Error  | r Mitigation technique in Configuration bit memor | ry                           |

|                           | FPC        | GA usi | ng Modified Matrix Code                           | 105                          |

|                           | 7.1        | Introd | $uction \dots \dots \dots \dots$                  | . 106                        |

|                           | 7.2        | Propos | sed Modified Matrix Code Algorithm                | . 107                        |

|                           | 7.3        | Hardy  | ware Architecture                                 | . 113                        |

|                           |            | 7.3.1  | Configuration Area                                | . 113                        |

|                           |            | 7.3.2  | Proposed ICAP block                               | . 113                        |

|                           |            |        | 7.3.2.1 Slave Interface:                          | . 114                        |

|                           |            |        | 7.3.2.2 MMC Block:                                | . 114                        |

|                           |            |        | 7.3.2.3 HWICAP:                                   | . 114                        |

|                           |            | 7.3.3  | Slave Interface Controller                        | . 115                        |

|                           |            | 7.3.4  | Master ICAP Controller and Secondary memory       | . 115                        |

|                           |            | 7.3.5  | Work flow                                         | . 115                        |

|                           | 7.4        | Result | s and performance analysis                        | . 117                        |

|                           | 7.5        | Summ   | ary                                               | . 120                        |

| 8                         | Con        | clusio | n and Future Scope                                | 121                          |

|                           | 8.1        | Conclu | ısion                                             | . 121                        |

|                           | 8.2        | Future | e Scope                                           | . 123                        |

|                           |            | 8.2.1  | Transaction                                       | . 124                        |

|                           |            | 8.2.2  | Journals                                          | . 124                        |

|                           |            | 8.2.3  | Conference                                        | . 124                        |

| $\mathbf{A}_{\mathbf{I}}$ | opdx       | A: Ab  | obreviations                                      | 129                          |

| R                         | efere      | nces   |                                                   | 122                          |

## List of Figures

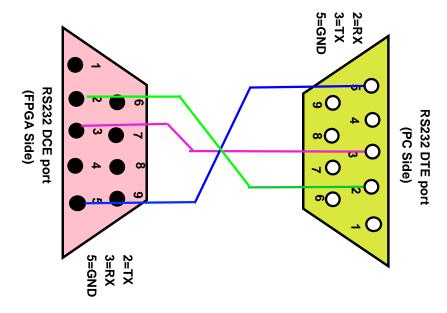

| 1.1 | RS232 DCE and DTE connection port                                 | 2  |

|-----|-------------------------------------------------------------------|----|

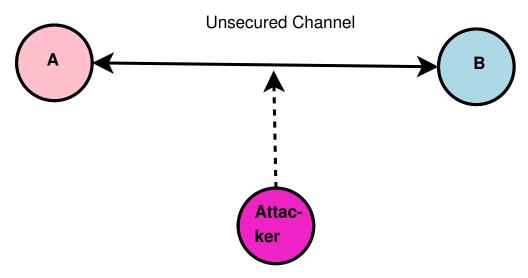

| 1.2 | Basic communication model                                         | 5  |

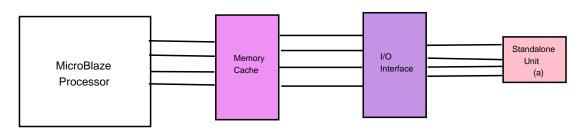

| 1.3 | External standalone processing unit (a)                           | 8  |

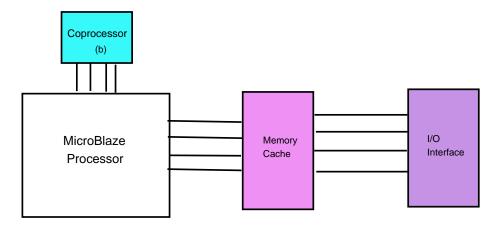

| 1.4 | Co-processor (b) unit with faster bus                             | 8  |

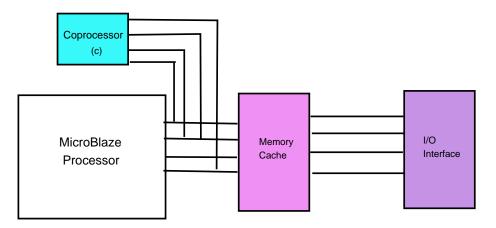

| 1.5 | Co-processor (c) unit with slower processor bus                   | 8  |

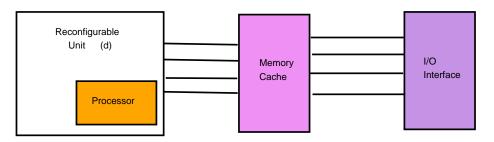

| 1.6 | Processor embedded in reconfigurable logic (d)                    | 9  |

| 1.7 | Chapter Organization                                              | 11 |

| 2.1 | Performance-flexibility graph among ASIC, FPGA and general        |    |

|     | purpose processor                                                 | 15 |

| 2.2 | A generic FPGA internal architecture                              | 17 |

| 2.3 | Xilinx Virtex-E/II FPGA CLB/slice architecture                    | 18 |

| 2.4 | HDL based design flow for FPGA based implementation               | 19 |

| 2.5 | User design routing of logic AND in an FPGA configuration memory  | 24 |

| 2.6 | SEU causes error in user design routing of logic AND in an FPGA   |    |

|     | configuration memory                                              | 24 |

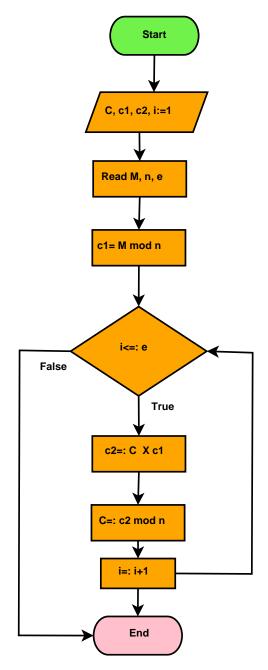

| 3.1 | Flow diagram for modulas exponential operation's hardware im-     |    |

|     | plementation                                                      | 33 |

| 3.2 | RSA Algorithm with modified binary method                         | 35 |

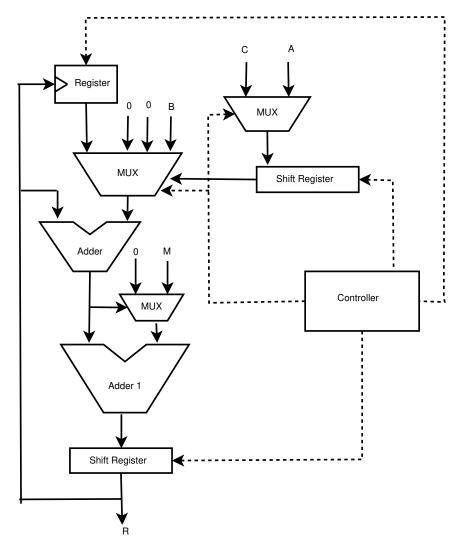

| 3.3 | Architecture of modified binary method                            | 36 |

| 3.4 | Processor and its peripherals of the designed system used in each |    |

|     | FPGA System                                                       | 38 |

| 3.5 | Abstract view of the complete system and secure communication     |    |

|     | flow using FPGA and Terminal                                      | 38 |

|     |                                                                   |    |

#### LIST OF FIGURES

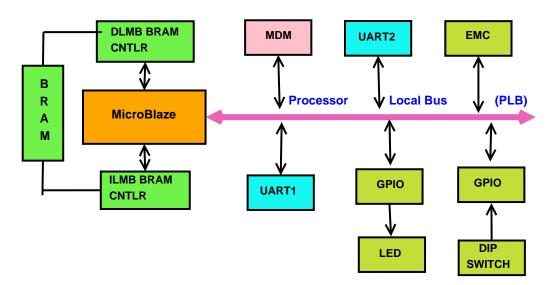

| 3.6  | UART system module attached with the Processor Local Bus         | 39 |

|------|------------------------------------------------------------------|----|

| 3.7  | Processor Based Architecture                                     | 41 |

| 3.8  | Single MicroBlaze architecture                                   | 42 |

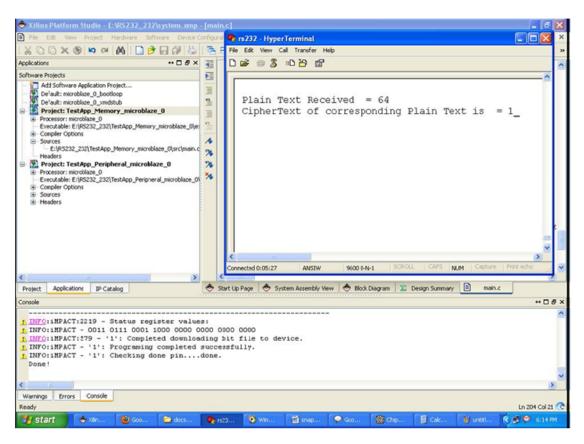

| 3.9  | Real time data accepted from keyboard to FPGA and the cipher     |    |

|      | text is shown on the hyper-terminal CAP                          | 43 |

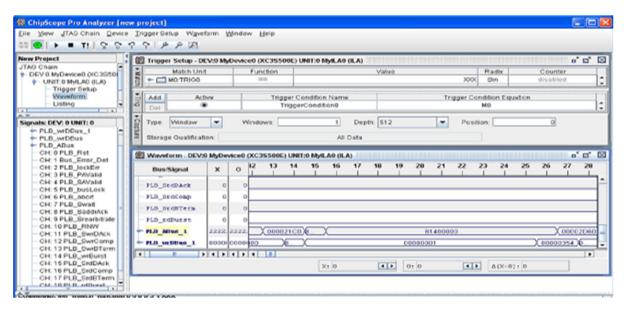

| 3.10 | Chipscope Pro analyzer results for experiment 1                  | 44 |

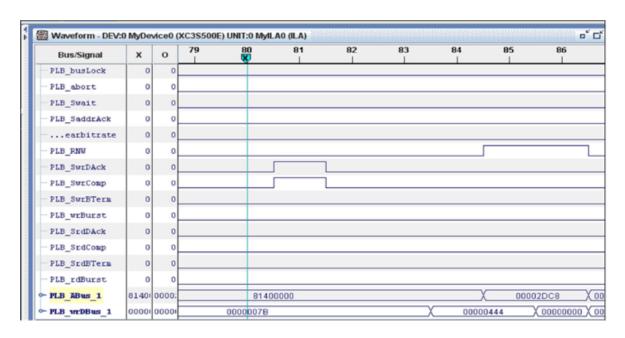

| 3.11 | Chipscope Pro analyzer results for experiment 2                  | 45 |

| 3.12 | Real lab picture of two connected Spartan 3E FPGA boards through |    |

|      | RS232 Cable                                                      | 46 |

| 3.13 | The Spartan 3E board                                             | 47 |

|      |                                                                  |    |

| 4.1  | Input and State array                                            | 53 |

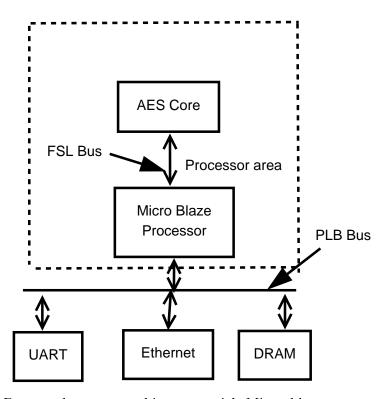

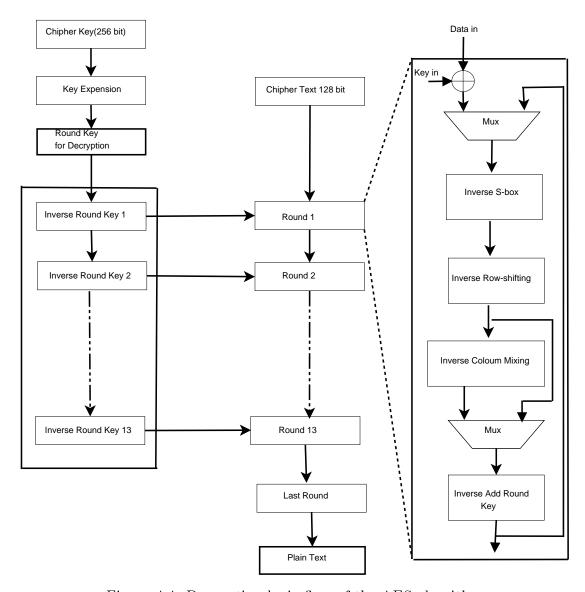

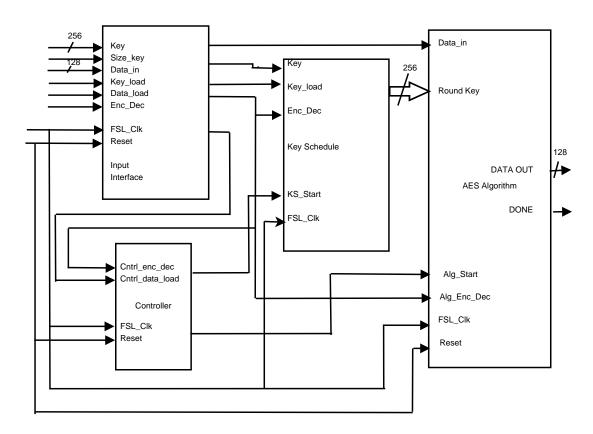

| 4.2  | Proposed system architecture with Micro blaze                    | 56 |

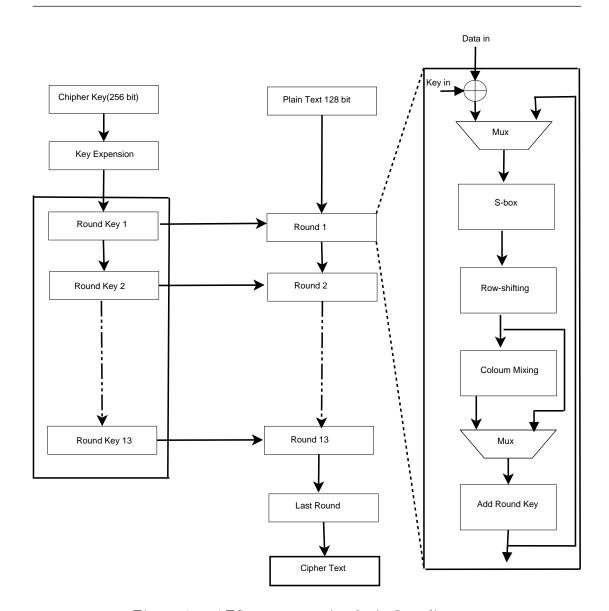

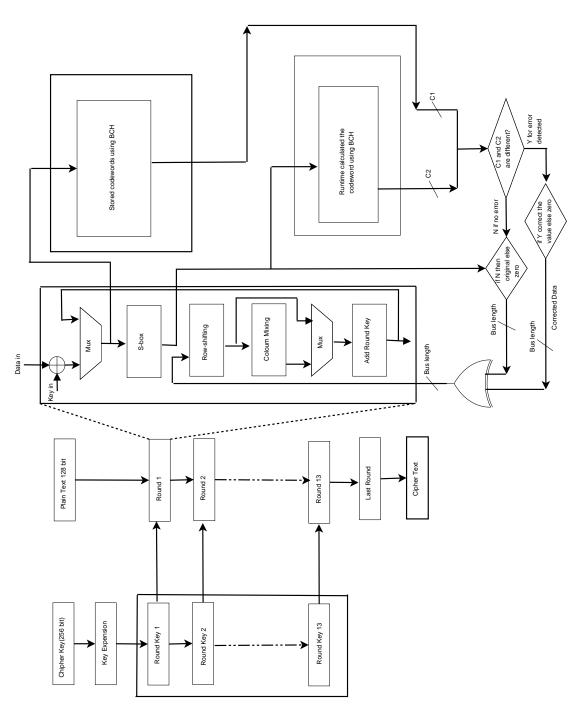

| 4.3  | AES 256 encryption logic flow diagram                            | 57 |

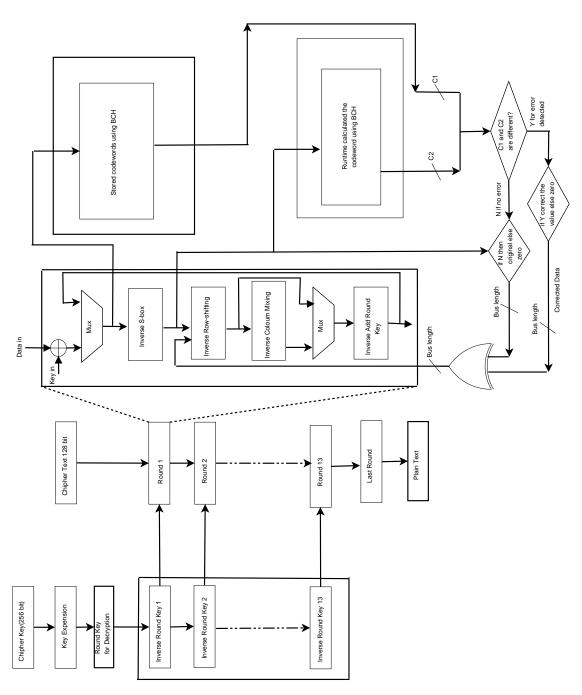

| 4.4  | Decryption logic flow of the AES algorithm                       | 58 |

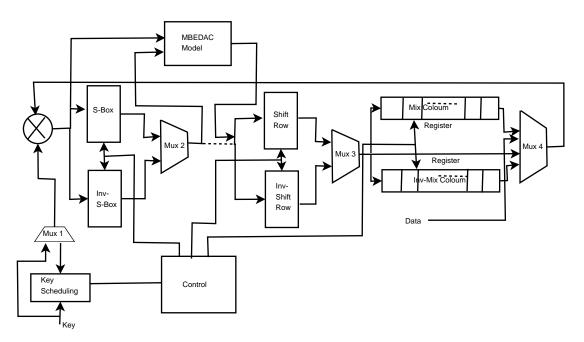

| 4.5  | Internal architecture of the AES Core                            | 59 |

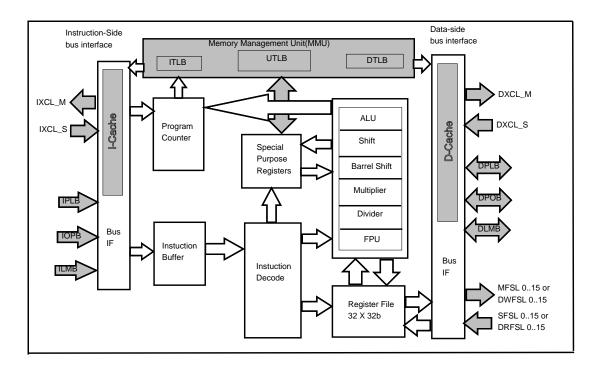

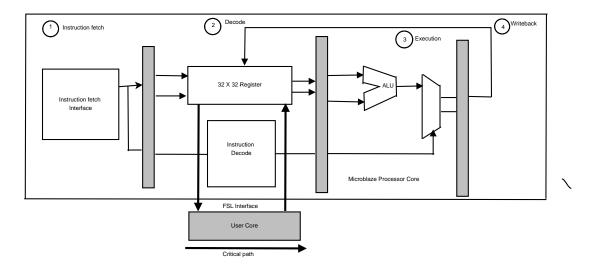

| 4.6  | Internal architecture of Microblaze processor core [1]           | 60 |

| 4.7  | User core connected with the Microblaze processor through the    |    |

|      | FSL link [2]                                                     | 61 |

| 4.8  | FSL bus communication between the AES co-processor and the       |    |

|      | Microblaze                                                       | 62 |

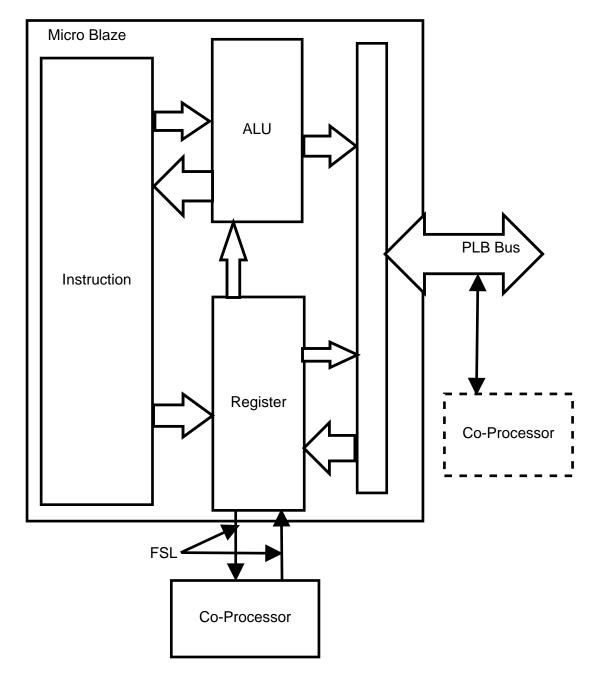

| 4.9  | Different ways of attaching a co-processor with the Microblaze   | 63 |

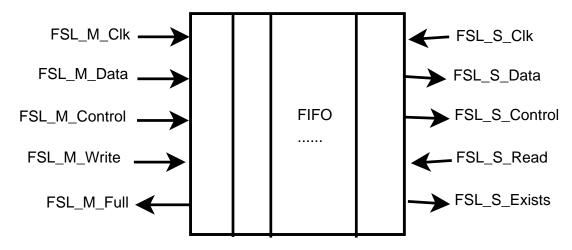

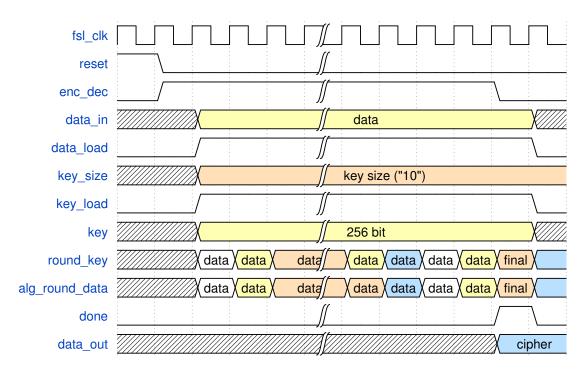

| 4.10 | FSL bus signals [2]                                              | 64 |

| 4.11 | Xilinx Virtex-5 LX110t-ft1136 board picture                      | 64 |

| ۲ 1  | Internal blacks of the surround surtons                          | 79 |

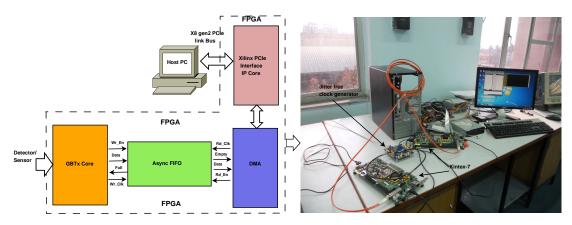

| 5.1  | Internal blocks of the proposed system                           | 73 |

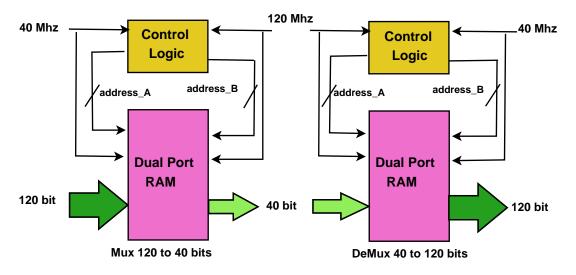

| 5.2  | Mux DeMux for clock domain crossing                              | 76 |

| 5.3  | Algorithm for Frame Aligner and Pattern Search                   | 78 |

| 5.4  | Data flow diagrams of the Frame Aligner and Pattern Search block | 78 |

| 5.5  | PCIe interfacing with blocks and Experimental setup of proposed  |    |

| ۰ -  | DAQ                                                              | 79 |

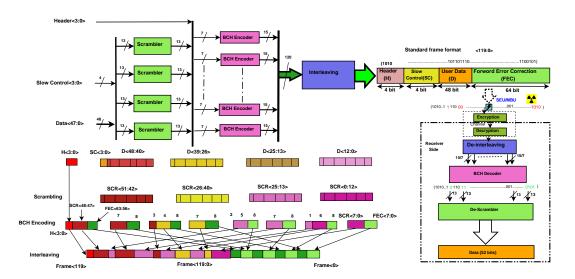

| 5.6  | Standard frame generation and Error correction flow with encryp- |    |

|      | tion/decryption                                                  | 80 |

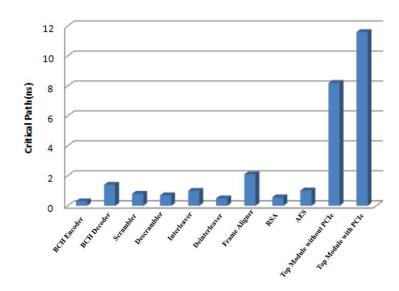

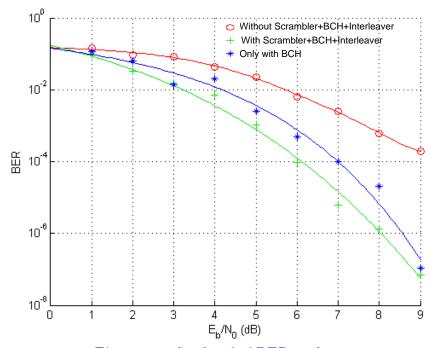

| 5.7  | Critical time for different block                                | 83 |

#### LIST OF FIGURES

| 5.8  | Study of of Bit Error Rate (BER) with noise                      | 83  |

|------|------------------------------------------------------------------|-----|

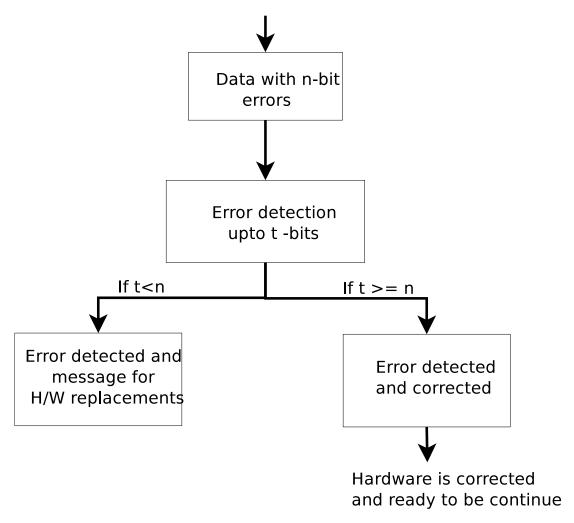

| 6.1  | Error detection and correction logic flow                        | 89  |

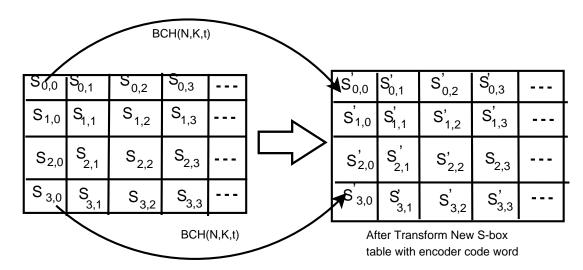

| 6.2  | Mapped encoder (codeword) table                                  | 91  |

| 6.3  | Sbox with fault model algorithm 1                                | 92  |

| 6.4  | Sbox with fault model algorithm 2                                | 93  |

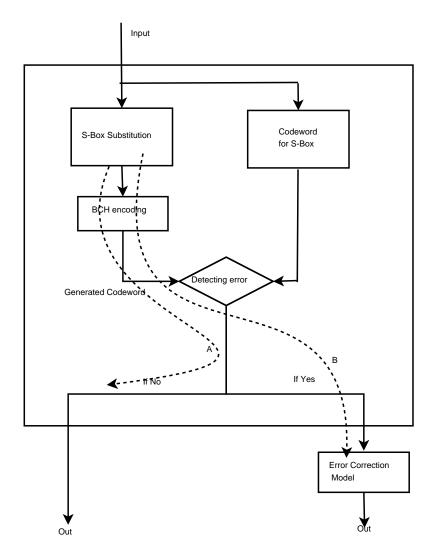

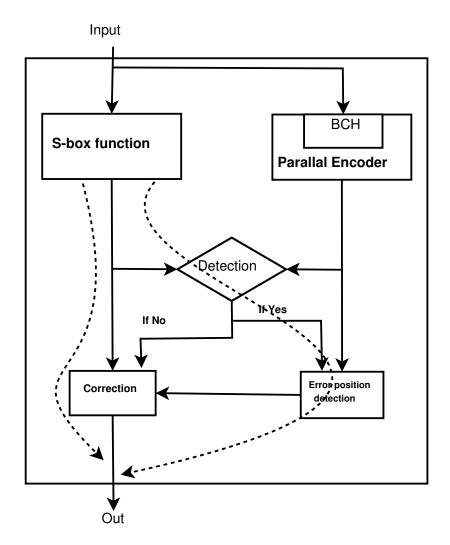

| 6.5  | Encryption flow with fault model                                 | 94  |

| 6.6  | Decryption flow with fault model                                 | 95  |

| 6.7  | AES Core with multi bit error detection and correction model     |     |

|      | (MBEDAC)                                                         | 96  |

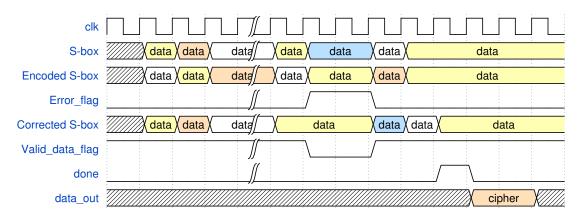

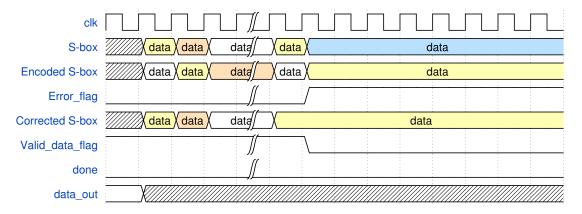

| 6.8  | Timing diagram of AES                                            | 100 |

| 6.9  | Timing diagram for multi bit error detection and correction      | 101 |

| 6.10 | Timing diagram for multi bit error detection without any correc- |     |

|      | tion due to number of error bits $> t$                           | 101 |

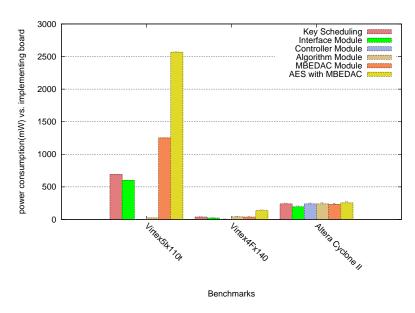

| 6.11 | Power consumption comparison between different board             | 103 |

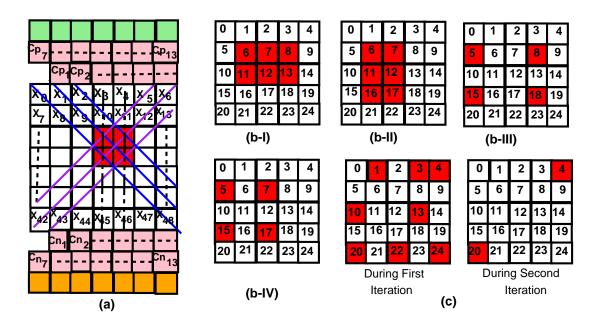

| 7.1  | a) Encoding/ Decoding using 7x7 window b) Different error pat-   |     |

|      | terns c) Error Correction using Multiple Iterations              | 108 |

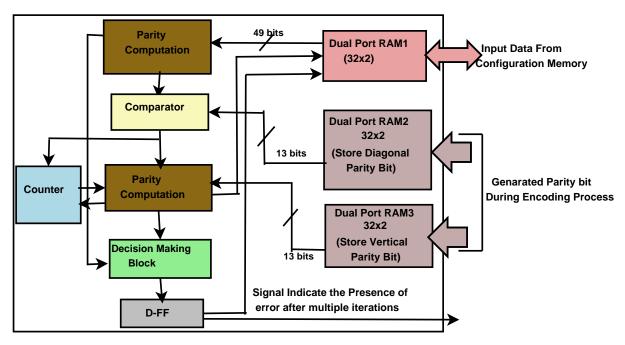

| 7.2  | Hardware Architecture of the proposed MMC code                   | 113 |

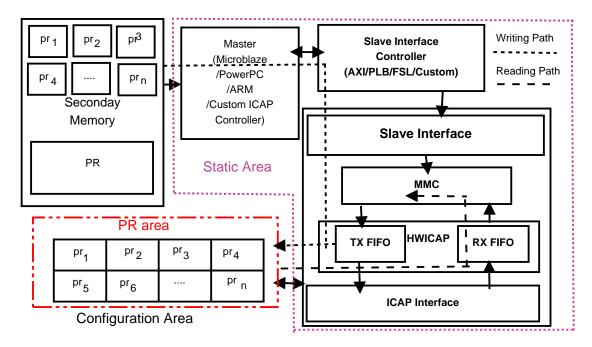

| 7.3  | Architecture of the proposed ICAP block                          | 114 |

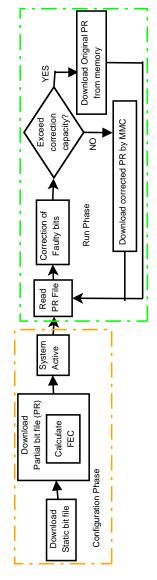

| 7.4  | Hardware implementation workflow for MMC $\dots$                 | 117 |

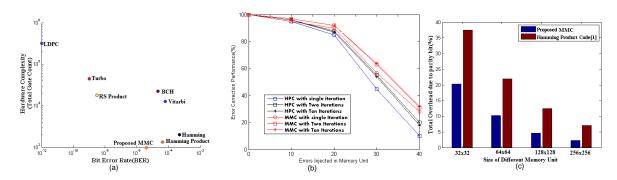

| 7.5  | a) Hardware Complexity vs BER b) Error correction performance    |     |

|      | on 32x32 memory unit c) Overhead comparison between proposed     |     |

|      | MMC code and HPC                                                 | 118 |

## List of Tables

| 3.1 | Stepwise results of mod calculation algorithm                                                                                  | 34  |

|-----|--------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Stepwise Result of Mod Calculation Algorithm                                                                                   | 37  |

| 3.3 | Encryption and decryption time (32 bit key size)                                                                               | 45  |

| 3.4 | Comparison of RSA implementation of key size(32 bit)                                                                           | 47  |

| 3.5 | Comparison of resource utilization and speed with existing 1024                                                                |     |

|     | bit RSA implementation                                                                                                         | 48  |

| 3.6 | FPGA-based ECC point multiplication on Koblitz curves                                                                          | 48  |

| 4.1 | Comparison with other AES implementations                                                                                      | 67  |

| 5.1 | Resource Utilization                                                                                                           | 82  |

| 5.2 | Module wise power consumption                                                                                                  | 82  |

| 5.3 | Comparison of related existing work with the proposed design                                                                   | 82  |

| 6.1 | Comparison of synthesis results of various AES implementations with and without error correction using various FPGA evaluation |     |

|     | boards [3]                                                                                                                     | 98  |

| 6.2 | Resource Utilization for BCH Model with Encryption and Decryption $$                                                           | 99  |

| 6.3 | Comparison of power dissipations of various blocks of the AES                                                                  |     |

|     | co-processor with error correction using the Xilinx Virtex FPGA                                                                |     |

|     | board                                                                                                                          | 102 |

| 6.4 | Comparison of power dissipations of various blocks of the AES                                                                  |     |

|     | co-processor with error correction using the Altera FPGA board .                                                               | 102 |

| 6.5 | $Comparision\ with\ existing\ single/multi\ error\ correction\ techniques$                                                     |     |

|     | with proposed model                                                                                                            | 103 |

#### LIST OF TABLES

| 7.1 | Comparison between Proposed Error Correcting scheme with the |     |

|-----|--------------------------------------------------------------|-----|

|     | other existing Error Correcting scheme                       | 119 |

## Chapter 1

#### Introduction

In the present era of high speed data communication, higher throughput and lower delay are the key drivers for efficient electronic system design. Successful operation of different sensitive embedded applications like Satellite link communication, Bio Medical device to device communication, High Energy Physics (HEP) read out chain, Internet of things (IoT) sensor etc. require efficient inter/intra system data communication methodologies. Due to increasing communication data rate, data is being moved within systems at much higher speed, which creates challenge in the design integration and implementation of the various sub-systems. Experiments like Compressed Baryonic Matter-Facility for Antiproton and Ion Research (CBM-FAIR), European Organization for Nuclear Research (CERN) need to capture and store data at a rate of over 1Tb/s. The success of the embedded applications developed for CBM-FAIR, CERN etc. depends on the communication speed between the front-end receiver sub-systems and the data aggregation unit and also the communicated data among data processing units and back end storage systems. So, an effective high speed communication protocol mechanism is very much needed for these type of embedded applications, otherwise the overall performance may be decreased. In general, the design of embedded systems for present day communication applications essentially needs to have various performance attributes such as high throughput communication protocols, error resiliency, security etc. Next, we give a brief overview of these performance attributes as below:

• High speed communication Protocol design: Several existing methods of communication mechanisms like RS232, Ethernet etc. can be used for inter/intra communications. RS232 is the one of the oldest methods in the era of digital communication through a serial link using RS232 standard. A RS232 standard Data Circuit-Terminal Equipment (DCE) and (Data Terminal Equipment (DTE) port transmit and receive wire connection is shown in Figure 1.1, where TX, RX,GND stands for transmit, receive and ground pin. This standard specifies signal timing, signal functions, signal voltages, a protocol for information exchange and mechanical connections. It has a maximum throughput of 120Kbps.

Figure 1.1: RS232 DCE and DTE connection port

On the other hand, Ethernet is a globally used standard protocol for data communications. But there are several disadvantages of using Ethernet in high speed communication process. Firstly, it uses predefined protocol like TCP/IP or UDP/IP. They are convenient but having several layers and all of them must be implemented and traversed for each data transmit/receive. Secondly, the hardware implementation of the protocol stack is costly and they are generally implemented in software layers. Lastly, overhead with respect to data packet traverse time, traversing the protocol stack also re-

sults in considerable overhead in the packet size, as a header is added at each protocol layer. Thus to support high data rate in present day communication systems there is a need of high speed data communication protocol design (CBM-FAIR [4]), radio telescope read out chain where data throughput may be higher than 1Tb/s. In order to achieve such high speed data communication, we need to design a suitable protocol for link management, flow control, synchronization, error control etc. and their efficient embedded implementation.

• Error control coding and correction: Hardware systems designed for data communication applications like satellite communication, HEP applications, IoT etc. are often affected by natural and experimental radiation and channel noises, which may lead to errors in the system's outcome. Errors can occur at (i) communication link (ii) internal processing blocks and (iii) memory. Here, we are considering the errors in the memory that can be two types soft and hard errors [5]. Faults created due to radiation effects can be categorized into (i) temporary and (ii) permanent. Temporary faults lead to temporary malfunctions that occur in solid state devices and their effect is manifested as soft error. Soft errors are not reproducible and sometimes lead to Single Event Upset (SEU) and multiple bit upsets (MBU) in different embedded devices. Permanent faults cause breakdown or punchthrough in the solid state devices that creates non-recoverable errors in the systems termed as hard error. Effect of soft errors in any logic will be transferred to the output of flip-flop or memory if its period of occurrence is higher than the period of the clock which drives the circuit. On the other hand hard errors are of two types: one is permanent recoverable errors and other one is permanent nonrecoverable errors. When charge particles permanently damage the logic or switching blocks within the systems, permanent nonrecoverable errors occur and it can only be sorted out by replacing the defective logic blocks physically (normally it is done by routing). On the other hand when SEUs or MBUs directly affect the configuration memory of embedded system, permanent recoverable errors may occur which can be corrected before they affect other logic blocks either by rewriting the content of memory and logic cell or by built-in error detection and correction code. This issues justify the need of different error correction and detection algorithms (Reed Solomon codes (RS), BCH encoding, modified matrix code (MMC) etc) to be incorporated within the high speed communication protocol to minimize the errors causing SEUs and MBUs in the system. Designing efficient error correction scheme in the hardware should also take into account the trade off between error coverage and hardware resource utilized. Attaining higher code coverage with low resource requirement is one of the key research issues in error correction mechanism.

• Secure communication: For inter/intra system communications, there is a high probability of tampering of the original data sequence by intentionally/unintentionally by unknown agents, which is a threat to security and authorized access of the system. In figure 1.2 a basic communication model is shown where 'A' and 'B' two nodes, communicating over an unsecured channel, and a attacker is trying to eavesdrop their communication. Data security can be implemented using different cryptographic algorithms on the channel data where instead of sending the original data over the unsecured channel, encryption and decryption is used. Encryption is the process of encoding messages or information with some randomly generated keys in such a way that only authorized persons who knows the exact key, can read (decrypt) it. In general, encryption techniques can be broadly classified as symmetric and asymmetric key encryption. In symmetric key encryption ( advanced encryption standard (AES) [6], Rivest Cipher 4 (RC4) [7] etc.) the same key is used for both encryption and decryption process whereas in asymmetric key encryption (Rivest-Shamir Adleman (RSA) [8], Diffie-Hellman key exchange [9], Elliptic curve cryptography (ECC) [10] etc.) different set of key is used for encryption and decryption process. Due to the inherent algorithmic computational complexity which occurs due to mathematical functions like exponential and mod operation in case of RSA, rounds operations depending on the key size for AES encryption/decryption etc. An efficient design and implementation of these algorithms needs to be performed in the design phase to enable secured communication. Authentication is the process by which the access signature of an user is verified for authorized access of the system. Authentication algorithms like Secure Hash Algorithm (SHA) [11], MD5 [12] etc. needs to be implemented to prevent unauthorized access of the system. So, the present generations of data communication system should be able to handle security issues like encryption and authentications in a resource optimized way.

Figure 1.2: Basic communication model

As a choice of target platform, the embedded designers have three choices namely, (i) standard micro-controller/microprocessor platform (ii) custom hardware platform based on Application-Specific Integrated Circuits (ASIC) and (iii) custom as well as re-configurable hardware platform based on Field Programmable Gate Arrays (FPGA) . Basic design architectures and design flow of these three platforms are described in the Section 2.2.1, Section 2.2.2 and Section 2.2.3 respectively.

#### 1.1 Motivation and scope of the work

A very famous quote by Cilardo et al. [13] who stated, "A mathematical construction with practical applications, such as a cryptographic algorithm, has no real interest, in an engineering sense, as long as methods

for feasible implementation are not available." In other words, efficient implementation techniques for cryptographic algorithms, secure communication protocol design, error correction and detection model in hardware level are necessary in order to use them in practice.

## 1.1.1 Need of efficient hardware design for secure data communication

Applications those are using cryptographic algorithms generally fixed with very fastened requirements for implementations. Low-cost applications, such as mobile handset devices, sensor networks, or smart cards, to name a few, often set tight constraints on available resources, such as logic, memory, or power. On the other hand, high-speed applications, such as data acquisition system used in satellite/ some real experiments bio medical application( [14] [15]CBM-FAIR [4], CERN [16] etc.), high-speed network servers require very high computation speeds in order to prevent cryptography from becoming the bottleneck [17], [18]. Therefore, design and implementation of fulfilling high speed communications protocol with security features (using cryptographic algorithm) requirements is often a challenging task and efficient implementation of cryptographic algorithms in hardware is a challenging research motivation.

Normally, general purpose microprocessors are used for implementing cryptographic algorithms but, in that case, the execution of computationally expensive secure cryptographic algorithms has bounded by the the limiting factor for overall performance [19]. Hence, dedicated hardware implementations are commonly required to cryptographic algorithmic implementation for better performance and security. Re programmable hardware such as FPGA has established itself as one of the most attractive platforms for cryptographic algorithms because of the combination of speed and flexibility [20]. This thesis concentrates on FPGA which are commonly considered very feasible implementation platforms among implementors of cryptographic algorithms [20].

The need of FPGA based real-time data communication is of special interest where FPGA based data acquisition systems are built to capture, store process and transmit the data generated from real time experiments [21] [22]. Also FPGA based system can work as an embedded system for network devices and communication gadgets, which requires security for real time data communication. FPGA vendors are providing hard and soft processor cores for this purpose, which can be effectively used for running the crypto algorithms on FPGA devices which is describe in section 1.1.2

#### 1.1.2 Cryptographic Algorithms in FPGAs

In order to accelerate the execution of complex mathematical tasks that are commonly performed in cryptographic processes, direct hardware execution of these tasks is a good choice. For an example, over one half of the processing time in Secure Sockets Layer (SSL) application is consumed in executing cryptographic algorithms [23]. A good plan is to have the most expensive operations of a cryptographic algorithm to be implemented as a custom logic block in the FPGA to have an accelerated performance, while the other parts of the application is implemented through software execution, performed by the general purpose processor like Microblaze, ARM cortex etc. Consider RSA algorithm as an example where the most expensive task is the modular exponentiation and hence, RSA can be accelerated by implementing exponentiations as a custom logic in the hardware while the main processor performs rest of the operations concurrently. The classification of reconfigurable systems are shown in figures mentioned below.

The external stand-alone processing unit (a) [24] shown in Figure 1.3 is best for applications which are computationally intensive but require little communication and the reconfigurable functional unit, e.g., reconfigurable instructions etc.

The attached co-processor classes (b) and (c) can be seen as a trade off between the fast dedicated bus [25] [8]. Figure 1.4 and Figure 1.5 describes co-processor classes (b) and (c) respectively.

The last class (d), where the processor is embedded in reconfigurable logic, is currently emerging research areas [8]. Figure 1.6 shows the block representation. This class of design implementation requires a device having a large number of

Figure 1.3: External standalone processing unit (a)

Figure 1.4: Co-processor (b) unit with faster bus

Figure 1.5: Co-processor (c) unit with slower processor bus

configurable blocks and thus will increase the system cost.

The embedded processors that are available in FPGAs can be either hard core such as PowerPC in Xilinx Virtex-4 FX, or soft core such as Microblaze in Xilinx FPGAs or Nios II in Altera FPGAs. All classes explained above, can be

Figure 1.6: Processor embedded in reconfigurable logic (d)

implemented with a stand-alone FPGA.

So to have the best design we have to find a correlation between these hardware and software design metrics that will be suitable for embedded secure communication, which seems to be a complex job.

## 1.1.3 Need of detection and correction of errors in high speed secure data communication beyond 1 Tb/s

High speed device to device data communication is needed in various applications like satellite communication, HEP experiments and Bio-medical analysis and visualization (involving audio/image/video data) for combined transmission of data, trigger, timing, fast and slow control and monitoring. In HEP experiments effect of radiation is pre-dominant in the detector side where radiation hardened electronics systems are used having higher cost and lower flexibility for upgradation. Whereas, the effect of radiation is much lower as we move outside the detector cave where the data acquisition (DAQ) electronics exist hence we can use commercial-off-the-self (COTS) FPGAs having efficient error handling techniques thus lowering the overall system cost. The success of these type of applications depend on the throughput, security and error handling capability of the entire DAQ chain. We need to built an error detection and correction mechanism to handle both SEU and MBU which can occur due to radiation in the environment. Forward error correction (FEC) has been considered as a strong and cost-effective way to improve the quality of transmission (QoT) that is used here for correction of errors happened due to SEU and MBU. The major research problems that have been considered in this phase of our research are given below:

- Enabling security in the embedded data communication process through encryption/decryption

- Design and implementation of an FPGA based system that can handle high speed communication (1 Tb/s) in embedded communication domain.

- Design and implementation of FEC as a hardware module for error correction capabilities for 1Tb/s optical fiber links.

- Handling configuration memory error in FPGA targets through MMC using partial reconfiguration techniques

#### 1.2 Organization of the Thesis

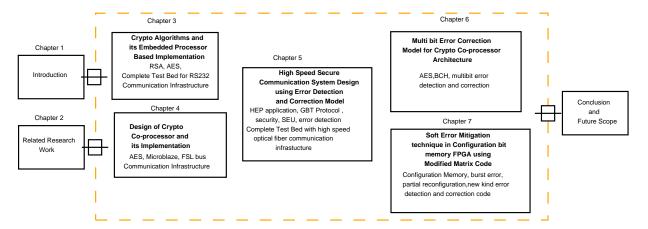

In this thesis, our contributions target some specific design and implementation issues to overcome some of the challenges existing in the present state-of-the-art embedded data communication systems. Related research work is described in Chapter 2. Crypto algorithms and its embedded processor based implementation along with a complete test setup for serial RS232 communication infrastructure is briefed in Chapter 3. The design of crypto co-processor and its implementation is described in Chapter 4. Chapter 5 and Chapter 6 described high speed secure communication system design using Bose, Chaudhuri, Hocquenghem (BCH) error detection and correction model and multi-bit error detection and correction model for crypto co-processor based architecture respectively. Chapter 7 briefs soft error mitigation technique caused by SEU or MBU in FPGA configuration bit memory using modified matrix code. The pictorial presentation of the dissertation is shown in Figure 1.7

Figure 1.7: Chapter Organization

## Chapter 2

#### Related Research Works

#### 2.1 Introduction

In the field of real time communications applications like radar communication [26], satellite communications networks, provide a global reach and wide area coverage to remote, rural and inaccessible regions in the earth. A few of its common applications include weather prediction, telephony services, telemedicine, multimedia services, internet connectivity, navigation through GPS, imaging through remote sensing satellites for resource monitoring and many important military applications. However security over these communication link is still a major concern in satellite/radar communications. On the other hand, applications like HEP applications [16] [4], bio-medical application [15] etc, also need a high speed, low latency and fault resilient communication channels for data sharing among different nodes of their network. In an other applications like smart grid [27], a next generations power control systems, there also a high speed communications network is needed among the different power grid for the data exchange. However with the increasing of the cyber attack in every critical applications which are mentioned here, the integration of high speed, reliable , error resilient and secure data communication networks is needed to manage the complex applications like radar communication [26], HEP applications [16] [4], bio-medical application [15] and smart grid [27] etc. with more effectively and intelligently

#### 2.2 Basics of available design platform

#### 2.2.1 Microprocessor and Micro-controller

Microprocessor based embedded system design relies on the on board microprocessor chip and the other component chips like memory and I/O controllers for successful implementation of the system. The functionality of the system is implemented through software instructions which are executed by the host processor utilizing the on board resources. The microprocessor based systems offer a generic infrastructure and not a custom infrastructure suited for the specific embedded application and hence cannot guarantee optimized performances. Some of the well known microprocessor platforms for embedded applications are 8008, 8085, 8086 etc.

Micro-controller based embedded systems are the most common choice for the traditional embedded programmers. Micro-controllers are single chip micro-computers, which include processing, memory and I/O elements in the same chip. They are normally used for specific application as they have limited resource and are driven by software instructions. Their performance is limited by the fact that they only provide generic processing core, which cannot satisfy the need of higher performance as compared to custom application specific cores. Some of the well known micro-controller platforms for embedded applications are 8051, ARM etc.

#### 2.2.2 Application Specific Integrated Circuits (ASICs)

ASICs are integrated circuits designed for specific application [28]. Unlike the general-purpose circuits, such as microprocessors and micro-controllers, ASICs are designed to perform a specific task or a function. Designs implemented in ASICs cannot be changed once the chip is fabricated or manufactured. There are

many embedded applications used in large experiments like CBM-FAIR, CERN etc. where upgradation of embedded hardware happens in repeated interval. In such cases to minimize the downtime of a system as well as to support the upgradation of the embedded hardware, FPGA is the only solution. Moreover, with the inclusion of partial programming capabilities in modern FPGAs, the downtime of the system is further reduced as the hardware upgradation in the partial reconfiguration region can work concurrently while, the other regions are on execution. The circuit implementation can be highly optimized in terms of speed, area and power consumption, but its inability to adapt design changes after manufacturing is a serious disadvantage. Modern ASIC fabrication processes are also costly and time consuming and hence, they are used predominantly in large volume different embedded gadgets, such as mobile phones, TV, micro oven medical devices etc..

#### 2.2.3 Field Programmable Gate Arrays (FPGAs)

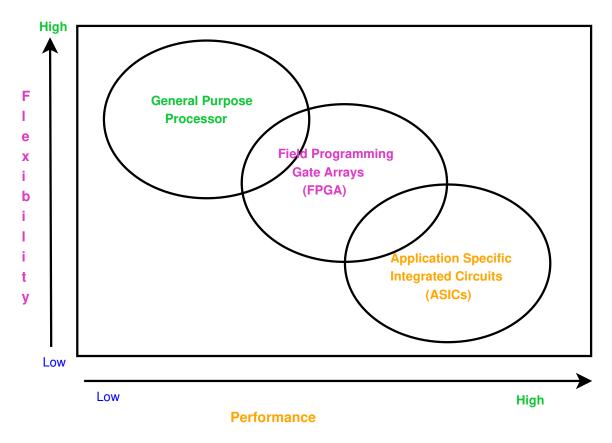

Programs and their implementation are flexible using general-purpose processors, in the sense that programs can be updated as per need by using high-level programming languages without modifying the underlying processor architecture. General purpose processors cannot cater the architectural requirement for a specific algorithm instead their focus is to support the processing need of a large variety of algorithms. Hence, on an average for any given algorithm the speed of execution in a general purpose processor is moderate and that leads to increasing processing time and energy expense. ASICs, on the other hand, offer higher performance and lower power consumption but are less flexible. Thus, there is a significant gap between general purpose processors and ASICs. Reconfigurable logic fills this gap and in an ideal case, combines the best of both; namely, the speed of ASICs to the flexibility of general-purpose processors. Figure 2.1 shows performance-flexibility graph.

Reconfigurable logic includes a wide scope of programmable devices including Programmable Logic Array (PLA), Programmable Array Logic (PAL), Complex Programmable Logic Device (CPLD), and FPGA. Though there are different programming devices available as said but from hardware cryptography imple-

Figure 2.1: Performance-flexibility graph among ASIC, FPGA and general purpose processor

mentation angles, we are interested on FPGAs and henceforth, the terms reconfigurable logic and device always refer to FPGAs in this thesis. In FPGA manufacturing world there are two leading vendors: Altera [29] and Xilinx [30]. Other FPGA manufacturers are Achronix, Actel, Atmel etc. Main units inside the FPGA are reconfigurable functional units, programmable switch matrix and I/O interfaces. For implementing any logic in the hardware, reconfigurable functional units are used and hardware blocks are interconnected by the re-configurable/programmable switch matrix.

Reconfigurability depends on the size of reconfigurable units referred to as granularity. There are two types of architecture used depending upon size of reconfigurable units: i) fine-grained and ii) coarse-grained. In fine-grained architecture, reconfigurable functional units are small whereas in coarse-grained recon-

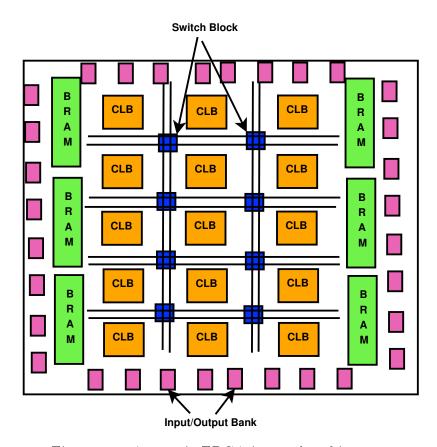

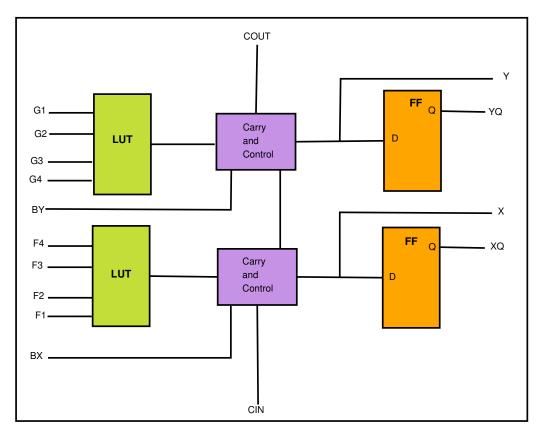

figurable units are larger. Look up table (LUT) is the basic unit in fine-grained architecture where with a small number of inputs and a single bit output [24]. Whereas in coarse-grained functional unit is an Arithmetic Logic Unit (ALU) [24] and, thus, complex arithmetic operations are fit better in coarse-grained architectures. The granularity of reconfigurable interconnections also varies in different re-programmable architectures so that fine-grained interconnections allow each bit to be connected separately whereas coarse-grained interconnections connect several bits at a time [24]. Present commercial FPGAs are mainly follow finegrained architectures where reconfigurable functional units are typically 4-to-1-bit LUTs which are arranged in clusters. A collection of LUT and flip-flop in FPGA is called configurable logic block (CLB). For an example a Xilinx Virtex-5 FPGA CLB contains 6 LUTs and 8 flip-flops. The number of LUTs and flip-flops per CLB varies depending on the different vendor specific FPGA boards. Internal interconnection among the CLBs are done by the switch box interconnection. A generic FPGA architecture with input/output block, CLB, block RAM (BRAM) is illustrated in the Figure 2.2. An example, Xilinx FPGA Virtex-E/II simplified CLB/slice architecture is shown in Figure 2.3. Modern FPGAs are also integrated with hard processor core (PowerPC, ARM etc.) and soft core(MicroBlaze, NIOS etc.) which can be used for any processor based complex embedded design using FPGAs.

Programming an FPGA means, implementation of the hardware in the FPGA logic blocks whereas for general purpose processor programming means providing a set of instructions to be executed by the processor. To know about the immanence of FPGA and its key features one can look into [31].

FPGAs bring new concepts due to their portability and their ability to reconfigure. In a nutshell they can offer the designers a sustained development process much faster and as efficient compared to the ASIC and microprocessor based design [31].

Nowadays FPGAs are widely used in embedded systems for their multiple advantages briefed as follows:

• FPGA can be used as a co-processor rather than a peripheral in a modern CPU using a high speed bus, like Peripheral Component Interconnect Express (PCIe)

Figure 2.2: A generic FPGA internal architecture

- Memory access inside the FPGA is just one clock cycle typically [32], and with an FPGA we have a far more fine-grained control over the memory data as compared to as the central processing unit (CPU). Low latency of memory access is one of the promising factors in increasing the FPGA performance as the waiting for the data during computations is less than a CPU

- FPGA supports partial reconfiguration where changing of a portion of reconfigurable hardware circuitry while the other part is still running/operating.

- They reduce time to market by reducing development cycle time

- They permit remote reconfiguration.

FPGAs are commonly used to achieve high performance computation as they offer spatial parallelism involving the configurable blocks.

Figure 2.3: Xilinx Virtex-E/II FPGA CLB/slice architecture

#### 2.2.4 FPGA Design Flow

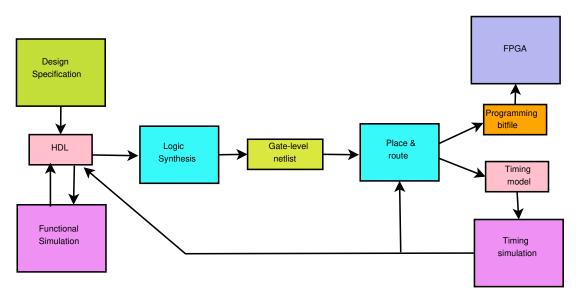

The design flow starts with the design specification and finishes into a working design in an FPGA. Figure 2.4 shows the design flow of FPGA-based implementations. The functionality of the hardware description language (HDL) is verified by functional simulations. After that a gate-level netlist with logic synthesis is mapped from the verified HDL. Using programmable switch matrix place and route process for the functional units are done. The place and route returns a programming bit file and a timing model description corresponding to the logic architecture. The timing model is verified to fulfill the timing requirements set in the specifications with timing simulations. Lastly, using the programming file commonly known as bit file, the FPGA is configured or programmed. Design softwares offered by the FPGA vendors support the complete design flow. Automatic mapping canbe also done by some tools like automatic HDL generators [33].

Figure 2.4: HDL based design flow for FPGA based implementation

Embedded systems are particularly vulnerable since physical access to these devices can be done at an ease. Indeed, the owner can be the attacker [34] explains that security has become an important issue in the embedded systems. Also an attacker may try to inject fault intentionally in the secure embedded system, secure communication channel etc. and thus comprising the security. In many of the cases the faults are caused unintentionally due to the natural effects e.g radiation, cosmic ray. Detecting the errors occurring due to these faults and also correcting them in the hardware will make the system more trustworthy. The design and implementation of efficient secure data communication techniques for reconfigurable hardware platform and making the system fault tolerant against the intentional/unintentional faults are the principal aim of this research work.

#### 2.3 Related work

Establishing communication security means integrity and confidentiality in the delivery of information to the receiver. Describe security in terms key features like confidentiality, authentication, integrity, access control, and key management, so that information over the communications remain correct and cannot be interpreted other than the actual

receiver [35]. While dealing with the security in satellite, radar, HEP and smart grid etc. communication, these key points always remain a major concern for the security measures. In general define the security key features as follows:

- Confidentiality means that only the appropriate users have access to the information.

- Authentication requires verification of a user's identity and right to access. It is achieved using a public key interchange protocol that ensures not only authentication but also the establishment of encryption keys.

- Integrity means that the information has not been corrupted. Information can be corrupted by the attacker injecting a error on it.

- Access control means that the system cannot be compromised by unauthorized access (e.g. pirating a satellite, pirating DAQ for HEP etc).

- Key management is the way how to manage the security keys (how dynamically generated, concealed and distributed, finally how well-kept by the actual target) users.

Thus for implementing secure communication framework, different cryptographic algorithms are need to be implemented in the transmitter and receiver sub-systems of a communication intensive application for secure data communication.

#### 2.3.1 Related work in secure communication

Most public-key algorithms involve operations such as modular multiplication and exponentiation, which are much more computationally expensive and time consuming. Among the existing public key algorithms the RSA is the most widely adopted [36]. Its security lies in the difficulty of factorizing large integers. Several Montgomery designs have been proposed for ASIC and FPGA implementations, based on limited resource availability to satisfy the computational burden [37], [38], [39]. A lot of research work

exists in the implementation of RSA algorithm on FPGA [40], [41] but there exists a very few research papers on the FPGA based implementation of RSA for real time data communication [42], which essentially involves execution of the security algorithm in coherence with the input data coming from the communication channel in real time. Another public key cryptography namely ECC and its implementation in FPGA can be found in related research works [43], [44], [45], [10]. In [46], a parallelization method utilizing point operation interleaving is proposed in FPGA implementation of ECC. Parallelization of scalable point multiplication that can support all 5 NIST Koblitz curves without reconfiguring structure is proposed in [47]. The above mentioned ECC implementations on FPGAs are standalone hardware implementation. A special care needed in hardware design to make them more faster, resource and power efficient for use in real communication field. Thus the need of FPGA based real-time data communication is of special interest where FPGA based data acquisition systems are built to capture, store process and transmit data generated from real time experiments [21] [22]. Also FPGA based system can work as an embedded system for network devices and communication gadgets, which requires security for real time data communication.

Though public key cryptography solves the problem of secure data exchange but still it has a big disadvantage, mainly speed, in comparison with the symmetric key based cryptography. Symmetric key cryptography is more suitable for the encryption of a large amount of data[3]. In 2000, the National Institute of Standards and Technology (NIST) announced Rijndael as the winner of AES contest, in an effort to address the threatened key size of Data Encryption Standard (DES) [6]. Though, we have a variety of software applications that provides security [48], [49], [50] but in comparison to hardware based implementations they are slow and are more resource hungry. Hence, there is an increasing need of implementation of security algorithms at the hardware level.

Research efforts have been made for the implementation of AES security algorithms on hardware for embedded system applications using FPGA [3], [51]. In [3], the authors have presented a parallel reconfigurable hardware implementation

of the AES cryptographic algorithm, which takes more clock cycles for encryption and decryption as it is based on a single processor core architecture. In the designs[51], [52] the user designed core is added with the Microblaze processor core [1] using the on chip peripheral bus (OPB), which is a slow bus and hence we need more clocks to send/receive data between the processor core and the user designed core. Microblaze is a Reduced instruction set computing (RISC) [53] soft core processor that is available in the Xilinx embedded devlopment kit [54]. A real time board to board communication with secure AES algorithm is shown in [55], where a software based implementation is done using Altera NIOS II processor core [56]. The other related research works on hardware based crypto-system design can be found in [57], [58], [55], [3], [59], [60], [51], [61]. As per the data provided by Xilinx, communication between a hardware and the Microblaze processor core is fastest for the case of Fast Simplex Link (FSL) bus connectivity [2], and hence FSL bus based design is well suited for high speed applications.

## 2.3.2 Related work in high speed communication and data acquisition

Real time embedded applications like radar communication, HEP applications, satellite communication, bio-medical application and smart grid applications etc discussed in section 2.1, a high speed, low latency and fault resilient data acquisition DAQ are of utmost need for control of the data communication. In a traditional DAQ system Frontend Electronics (FEE) data is captured from the sensors through a high speed differential Low-voltage differential signaling (LVDS) link [62], which is processed and then transmitted to the back end storage device using high speed links like Ethernet, PCIe, fiber optic etc. for further data analysis. A commonly faced problem in the traditional DAQ systems is adaptation with high data rate [63] and prone to SEU and MBU specially in case of radiation intense environment. Presently optical fiber and PCIe are the most suitable options in high speed data transmission over normal copper based LVDS line as they are less susceptible to noise and interference, bandwidth, range of transmission etc [64]. We are not considering open channel communication like

wireless medium in this context.

In [65] the authors brief a new protocol Gigabit Optical Serial Interface Protocol (GOSIP) for communication over optical fiber and implemented PCIe to optical link interface on FPGA for their DAQ system. This system gives a stable data rate of 1.6 Gbps. In [66], we find the implementation of optical link between two PCIe buses of computing nodes, which achieved the data rate of 8.5 Gbit/s. They have used PCIe hard IP available in ALTERA Stratix IV FPGA board. Liansheng Liu et.al presented the development of a fiber channel node with PCIe interface for avionics environments in [67]. Two nodes are connected by optical fiber through Small Form-factor Pluggable (SFP) and maximum data transfer rate achieved in this case is 2.125 Gbps. A high-speed data transmission protocol over optical fiber for real time data acquisition in Beijing Spectrometer III (BESIII) trigger system had been developed by Hao Xu et.al in [68]. Here they have used Multi Gigabit Transceiver (MGT) of Virtex-II Pro series FPGA for data transmission over optical fiber and achieved data rate of 1.75 Gbps. In [69], a high speed data transfer protocol named Serial Front Panel Data Port (SFPDP) over optical fiber is implemented on FPGA to capture the data from Digital Signal processor (DSP) through eXtended Attachment Unit Interface (XAUI) where the optical link can work on three distinct speeds: 1.0625 Gbaud, 2.125 Gbaud, and 2.5 Gbaud. In [70], authors have used a bus master, direct memory access (DMA) along with a 4-lane generation 2 PCIe link to transfer the stream data from FPGA to PC. The highest transfer rate achieved in this case is 784 Mbps. The above mentioned works are only focused on the high speed communication protocol design, they are not considering the security aspects on it. In this thesis we have considered high speed communication with security protocol as well as error resilient techniques in it.

# 2.3.3 Related work on High speed communication with error detection/correction

System designed for satellite communication, HEP experiments and others(section 2.1) with FPGA for high speed secure communications are effected by experimen-

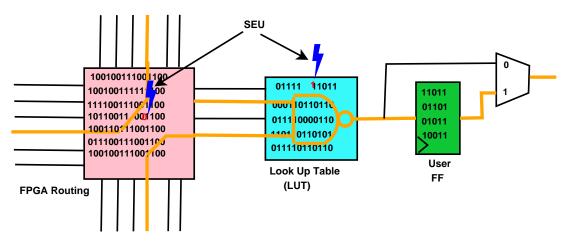

Figure 2.5: User design routing of logic AND in an FPGA configuration memory

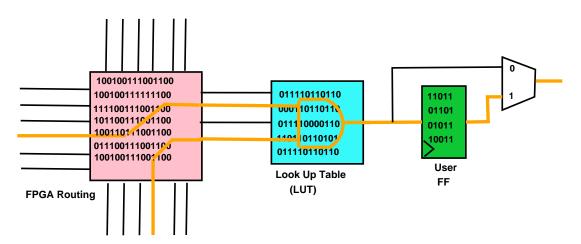

tal and natural radiation is a common phenomena [71]. Radiation effects reflected in FPGA's configuration memory. FPGA configuration memory architecture is described here and explain how it effected by faults. In Figure 2.5 configuration memory of FPGA with the series of 1's and 0's represents the function of the routing and logic elements interconnection switch, LUT , and Flip-Flop to implement an user design logical AND gate into FPGA.

Figure 2.6: SEU causes error in user design routing of logic AND in an FPGA configuration memory

Figure 2.6 shows a SEU (sometimes known as bit flips) which changes the configuration memory bit and an unintended signal rerouting and change in the logical function of the design happened due to this change in the configuration

memory bit.

Effect of SEU and MBU in FPGA can be broadly classified into two categories: Temporary or transient and permanent [72]. Effect of transient faults into any combinational or sequential logic will be transferred to the output of flip-flop or memory if its period of occurrence is higher than the period of the clock which drives the circuit. The transient faults frequently affect the user logic and memory elements and it can be corrected within a few seconds either by rewriting the memory content and logic cell(s) or by built-in error detection and correction code. Sometimes SEU or MBU can directly affect the configuration memory of FPGA. Then this effect is permanent in the sense that this error cannot be corrected unless we reconfigure the FPGA. This is also one kind of permanent fault, but it is recoverable [72]. When charge particles permanently damage the logic or switching blocks within the FPGA then it is also termed as permanent fault, but they are nonrecoverable. This error can be sorted out only by replacing the defective logic block physically (normally it is done by re-routing [73]). In [73], permanent recoverable faultshave only been considered.

One of the common solution to prevent FPGA devices from the effect of radiation is to use radiation hardened (Radhard) FPGAs. But they are more costly compared to the COTS FPGA [74] and are also few generation behind than COTS FPGAs. So in different commercial applications, COTS FPGAs are used with various error mitigation techniques. Triple modular redundancy (TMR) [75] and concurrent error detection (CED) [76] are most commonly used techniques in FPGA for error mitigation. In TMR, three identical logic blocks having the same functions are connected in tandem and final output from the system will be obtained through majority voting. An additional error detection circuit is used along with the main circuit in CED [76]. When any error is detected, the main circuit recomputes or rolls back the whole operation from the beginning. The above mentioned schemes consume large area, huge power and are not suitable for real time applications. Large area overhead of TMR can be reduced by using TMR only in critical portions of a circuit instead on the whole design which is known as partial TMR as described in [77]. The problem related to extra overhead can be reduced by using scrubbing. In scrubbing, before downloading the bit file into the configuration memory, one copy of original bit file (also known as the golden copy) is stored separately in a Radhard memory. During run time, this golden copy is downloaded into configuration memory with some periodic interval. It reduces the effect of accumulated error in FPGA and increases the lifespan of the FPGA [78]. An alternative to this method is known as configuration read back as described in [72]. In this scheme data from the configuration memory is continuously read back and cyclic redundancy check (CRC) operation is done in a separate memory. If error is detected, the FPGA has to be re-programmed again. Sometimes TMR can also be used intelligently with scrubbing to reduce the effect of single event upset as described in [79] for Virtex FPGAs.

The above mentioned schemes are not applicable in real time because they are based on either time or space redundancy or combination of both. The error detection and correction (EDAC) codes play an important role in many successful SEU and MBU mitigation schemes. The SEU and MBU can be protected by using single error correcting hamming code, which may not be sufficient for reliable communication in high speed DAQ system. So multiple error correction codes can be applied in this kind of high speed DAQ. Several multiple FEC have been presented in different papers e.g. BCH code [80], Reed Solomon encoding and Reed Muller codes [81]. Different commonly used error correcting codes like BCH, RS [82], low-density parity-check (LDPC) [83] can be an alternative solution to protect configuration memory of FPGA against soft error, but the hardware complexity and resource utilization of the above mentioned codes are very high. So simple low complexity error correcting codes are always preferable to protect configuration memory in FPGA. Error detection and correction on full configuration memory using different error correcting codes will increase system latency. At the same time downloading of the bit file after error correction will momentarily stop the system operations. These techniques are not a good choices for any real time applications. To alleviate these effects Dynamic Partial Reconfiguration (DPR) can be used with error detection and correction codes. In this case error correction code will correct only a particular portion of the configuration memory at a time and download only the corrected portion of the bit file without hampering the normal system operation involving the other blocks in the design.

In all of the above mentioned papers the authors did not considered anything

about SEU mitigation in high speed data acquisition system to work in an adverse environmental condition like deep space experiment [84] or in HEP experiment. The scope of our work also takes into consideration an efficient design of the various stages in the embedded DAQ chain to meet the high rate data acquisition requirements.

# Chapter 3

# Crypto Algorithms and its Embedded Processor Based Implementation

FPGA devices are coming very strongly in the embedded system design due to the availability of ready to use resources, parallel logic operations and reconfigurable designs. The usage of FPGA systems in real time domain is also a very fruitful proposition as the FPGA devices are coming with processing cores for real time data processing [85] [86]. In case of a complex embedded application environment involving a large amount of processing tasks and involving data communication among the nodes, we can use multiple FPGA devices acting as transmitter and receiver nodes respectively. To make this possible we have to establish a real time data communication between multiple FPGA devices and to make it even better, we have to apply data encryption techniques for making this communication secured.

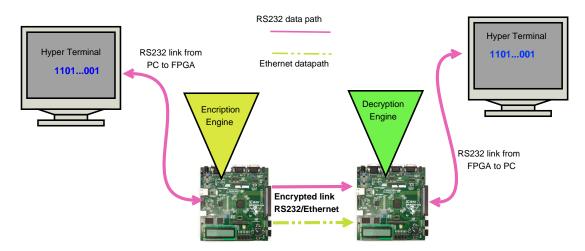

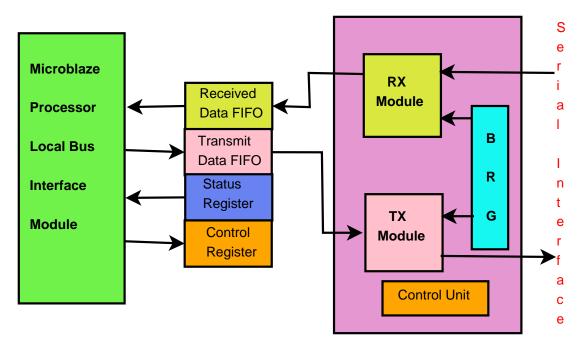

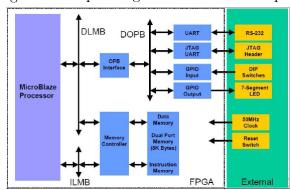

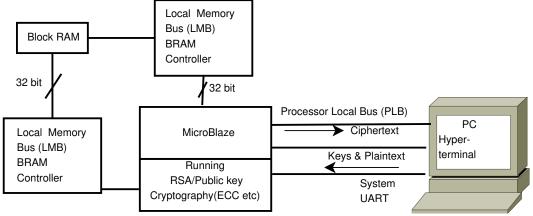

In this chapter we demonstrate the design and implementation of a RSA algorithms by developing suitable embedded system and Software design on Xilinx Spartan-3E (XC3S500E-FG320) device, the implementation has been tested successfully for real time serial data communication between multiple FPGA devices using the RS232 serial interface. This development work is also useful for the embedded applications, which requires on board execution of security algorithms.

The system is optimized in terms of execution speed and also has been verified using Xilinx ChipScope Pro a real time debugging tool.

#### 3.1 Introduction

Data security has been the key criterion of most of the present day applications like communication devices, network services on Internet, on-line money transactions, digital cash, electronic mail etc. These applications are implemented using various cryptographic techniques of varied nature. Cryptography is the art of using mathematics to address the issue of information security. Cryptographic systems can provide the objectives of information security: confidentiality, user authentication, data origin authentication, data integrity and nonrepudiation [87]. In contrast to symmetric-key crypto systems, public-key crypto systems are capable of fulfilling all of these objectives. However, in order to be fast enough and feasibly practical in the applications mentioned above, public-key schemes have to be implemented in embedded system, which is likely to provide the ease of installation as well as security from tampering. Among the existing public key algorithms the RSA is the most widely adopted [36]. Its security lies in the difficulty of factorizing large integers. Several Montgomery designs have been proposed for ASIC and FPGA implementations, based on limited resource availability to satisfy the computational burden [37], [38], [39]. FPGAs have large configurable logic resources in addition to dedicated high-speed ALU logic for operations such as multiplication. The key reasons for choosing FPGA for the implementation of the security algorithms lies in the flexibility to change key length or modify the embedded algorithm to respond to design flaws or changes in standards or data formats. A lot of research work exists in the implementation of RSA algorithm on FPGA [40], [41] but there exists a very few research papers on the FPGA based implementation of RSA for real time data communication [42], which essentially involves execution of the security algorithm in coherence with the input data coming from the communication channel in real time. The need of FPGA based real-time data communication is of special interest where FPGA based data acquisition systems are build to capture, store process and transmit data generated from real time experiments [21] [22].

Novelty and contribution in this chapters are,

- Efficient modified modular and binary modular exponential method has been proposed for design of embedded RSA processor

- Efficient implementation of another public key cryptography algorithm ECC as embedded processor in FPGA

- Established secure real time communication between multiple FPGAs through respective RS232.