# Single Event Upsets in the PANDA EMC

Results from neutron and proton irradiations of the digitiser board

M. Preston, P.-E. Tegnér (Stockholm University) H. Calén, T. Johansson, K. Makónyi, P. Marciniewski (Uppsala University)

M. Kavatsyuk, P. Schakel (University of Groningen)

PANDA FEE/DAQ Workshop, May 2018, GSI

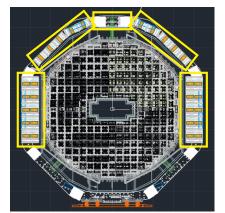

## Front-end electronics in the Electromagnetic Calorimeter

$\sim$  600 front-end digitiser boards in the EMC

375 in Barrel 225 in Forward Endcap

## Front-end electronics in the Electromagnetic Calorimeter

$\sim$  600 front-end digitiser boards in the EMC

375 in Barrel 225 in Forward Endcap

Figure courtesy of C. Schnier.

- Distributed over several crates placed around the detector perimeter.

- Two Xilinx Kintex-7 FPGAs per board.

- Of interest here: SEUs caused by neutrons and protons in FPGA.

- Interesting also for other subdetectors.

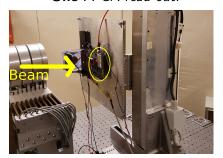

### Proton irradiation

▶ In November 2016 at the AGOR cyclotron at KVI.

### Proton irradiation

- ▶ In November 2016 at the AGOR cyclotron at KVI.

- Board perpendicular to the beam (covering half of the board).

One FPGA read out.

- Three proton energies:

- ▶ 184 MeV (primary beam energy)

- ▶ 80 and 100 MeV (with degrader)

- ► Total proton fluence:

- $\sim 4 \cdot 10^9 \text{ cm}^{-2}$ .

### High-energy neutron irradiation

- ▶ In June 2016 at the The Svedberg Laboratory (TSL) in Uppsala.

- ▶ Proton beam (180 MeV)  $\rightarrow$  W target  $\rightarrow$  Neutron beam. Board perpendicular to the beam. **One** FPGA read out.

### High-energy neutron irradiation

- ▶ In June 2016 at the The Svedberg Laboratory (TSL) in Uppsala.

- ▶ Proton beam (180 MeV)  $\rightarrow$  W target  $\rightarrow$  Neutron beam. Board perpendicular to the beam. **One** FPGA read out.

- ► Total neutron fluence:  $2 \cdot 10^9$  cm<sup>-2</sup> (>10 MeV).

### Low-energy neutron irradiation

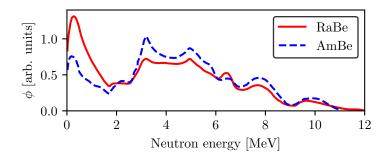

- ▶ In December 2017 January 2018 at Stockholm University.

- Separate measurements using RaBe and AmBe neutron sources. One FPGA read out.

### Low-energy neutron irradiation

- ▶ In December 2017 January 2018 at Stockholm University.

- Separate measurements using RaBe and AmBe neutron sources. One FPGA read out.

- ▶ Total neutron fluence:  $1 \cdot 10^{10}$  cm<sup>-2</sup>.

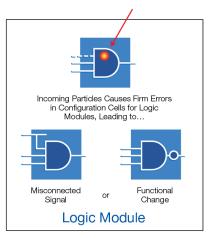

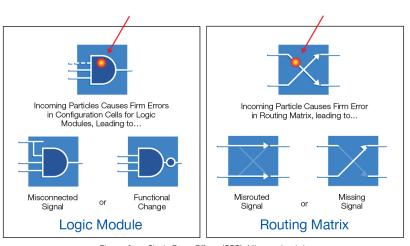

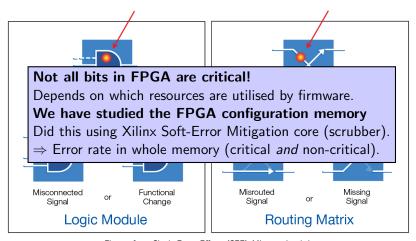

## Single Event Upsets (SEUs) in FPGAs

Figures from Single Event Effects (SEE), Microsemi website.

## Single Event Upsets (SEUs) in FPGAs

Figures from Single Event Effects (SEE), Microsemi website.

## Single Event Upsets (SEUs) in FPGAs

Figures from Single Event Effects (SEE), Microsemi website.

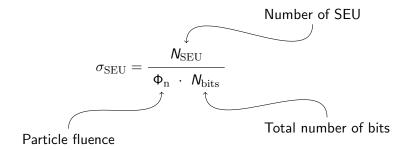

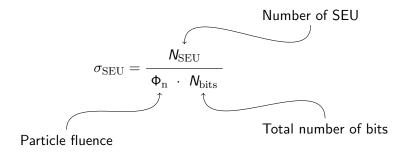

#### SEU cross section

The cross section (per bit) for an SEU in the FPGA is given by

#### SEU cross section

The cross section (per bit) for an SEU in the FPGA is given by

Once the cross section and particle flux are known, the *SEU rate* and *mean time between upsets* may be determined.

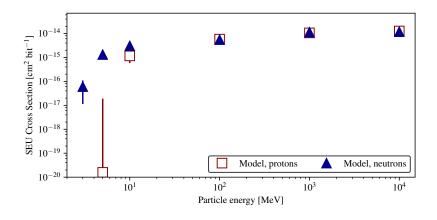

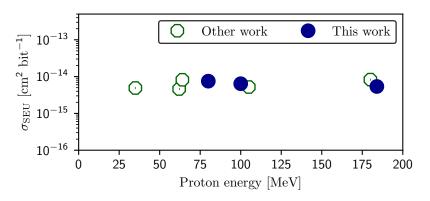

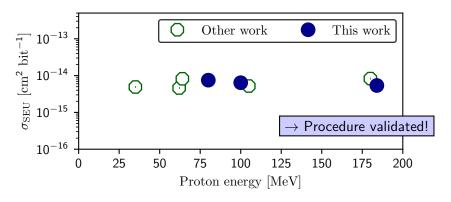

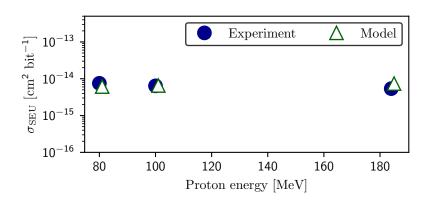

#### Proton irradiation

Good agreement with other measurements on Kintex-7:

Other work from for example ATLAS (LAr) and LHCb (RICH) groups.

#### Proton irradiation

Good agreement with other measurements on Kintex-7:

Other work from for example ATLAS (LAr) and LHCb (RICH) groups.

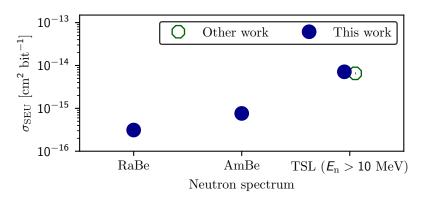

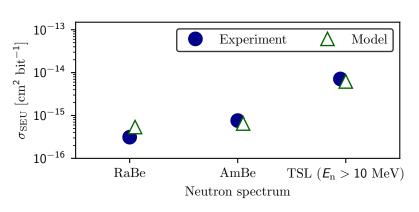

#### Neutron irradiations

Good agreement with other measurement on Kintex-7:

Other work from ATLAS (LAr) group.

TSL cross section determined from neutron fluence above 10 MeV.

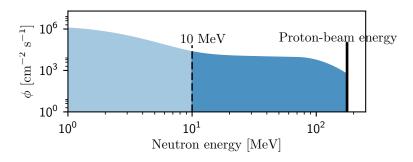

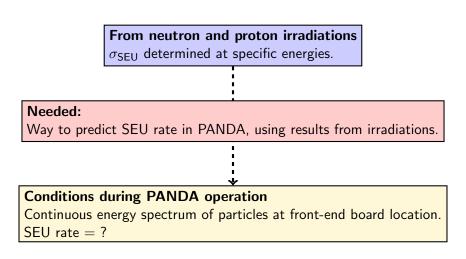

#### What does this mean for PANDA?

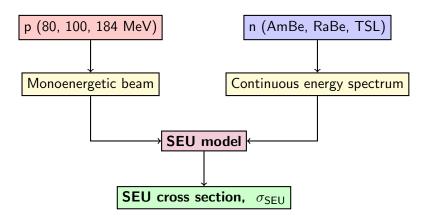

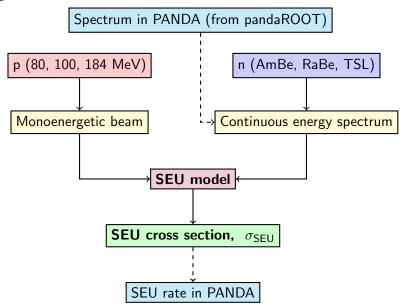

From neutron and proton irradiations  $\sigma_{\rm SEU}$  determined at specific energies.

#### **Conditions during PANDA operation**

Continuous energy spectrum of particles at front-end board location.

SEU rate = ?

#### What does this mean for PANDA?

### What does this mean for PANDA?

From neutron and proton irradiations  $\sigma_{\rm SEU}$  determined at specific energies.

#### Solution: Monte Carlo simulations

- 1) Geant4-based model of energy deposits in microelectronics  $\Rightarrow \sigma_{\mathsf{SEU}}(E)$

- 2) pandaROOT simulation  $\Rightarrow \Phi(E)$

#### **Conditions during PANDA operation**

Continuous energy spectrum of particles at front-end board location.

SEU rate = ?

### Developing the SEU model

- Model of energy deposition by protons and neutrons in a memory cell.

- Principle based on standard SEU-modelling tools constructed to match Kintex-7 feature size.

- In the model, an SEU occurs if the energy deposition in the sensitive volume is larger than a critical energy.

### Developing the SEU model

- Model of energy deposition by protons and neutrons in a memory cell.

- Principle based on standard SEU-modelling tools constructed to match Kintex-7 feature size.

- In the model, an SEU occurs if the energy deposition in the sensitive volume is larger than a critical energy.

- ► The values of the model parameters were determined by fitting the model to our experimental data:

- Simulate proton and neutron beams matching experiments.

- Fit to all our data using a full likelihood fit.

- When this was done, the model was verified by comparing the resulting cross sections with the experimental data.

### SEU model verification

### SEU model verification

Model works for both protons and neutrons.

### Using the SEU model

### Using the SEU model

- ▶ Simulations performed at antiproton momenta of 1.5, 5.2 and 8.9 GeV/c (to cover the entire phase-1 range) → neutron flux at **forward endcap** digitisers.

- ▶ All three resulting spectra used as input to the SEU model  $\rightarrow$  SEU rates (assuming  $\mathcal{L}=1\cdot 10^{31}~\text{cm}^{-2}~\text{s}^{-1}$ ).

- ▶ Simulations performed at antiproton momenta of 1.5, 5.2 and 8.9 GeV/c (to cover the entire phase-1 range) → neutron flux at **forward endcap** digitisers.

- ▶ All three resulting spectra used as input to the SEU model  $\rightarrow$  SEU rates (assuming  $\mathcal{L}=1\cdot 10^{31}~\text{cm}^{-2}~\text{s}^{-1}$ ).

- ▶ Error rate highest at  $p_{\rm pbar} = 8.9~{\rm GeV}/c \rightarrow {\rm use}$  as worst-case scenario.

- ▶ Simulations performed at antiproton momenta of 1.5, 5.2 and 8.9 GeV/c (to cover the entire phase-1 range) → neutron flux at **forward endcap** digitisers.

- ▶ All three resulting spectra used as input to the SEU model  $\rightarrow$  SEU rates (assuming  $\mathcal{L}=1\cdot 10^{31}~\text{cm}^{-2}~\text{s}^{-1}$ ).

- ▶ Error rate highest at  $p_{\rm pbar} = 8.9~{\rm GeV}/c \rightarrow {\rm use}$  as worst-case scenario.

- ho  $p_{

m pbar} = 8.9 \ {

m GeV}/c$ ,  $\mathcal{L} = 1 \cdot 10^{31} \ {

m cm}^{-2} \ {

m s}^{-1} \Rightarrow$

- $\phi_n$  at position of digitisers is  $\sim 300 \text{ cm}^{-2} \text{ s}^{-1}$ .

- MTBU due to neutrons (per FPGA):

- Any type of SEU: 18 hours.

- ▶ SEUs not correctable by SEM: 180 hours ( $\sim$  10% of all errors).

- ▶ Simulations performed at antiproton momenta of 1.5, 5.2 and 8.9 GeV/c (to cover the entire phase-1 range) → neutron flux at **forward endcap** digitisers.

- ▶ All three resulting spectra used as input to the SEU model  $\rightarrow$  SEU rates (assuming  $\mathcal{L}=1\cdot 10^{31}~\text{cm}^{-2}~\text{s}^{-1}$ ).

- ▶ Error rate highest at  $p_{\rm pbar} = 8.9~{\rm GeV}/c \rightarrow {\rm use}$  as worst-case scenario.

- ho  $p_{

m pbar}=8.9~{

m GeV}/c$ ,  ${\cal L}=1\cdot 10^{31}~{

m cm}^{-2}~{

m s}^{-1}$

- $\phi_n$  at position of digitisers is  $\sim 300 \text{ cm}^{-2} \text{ s}^{-1}$ .

- MTBU due to neutrons (per FPGA):

- Any type of SEU: 18 hours.

- $\blacktriangleright$  SEUs not correctable by SEM: 180 hours ( $\sim$  10% of all errors).

- ► These values include a safety factor of 10 relative to the results predicted by the model.

### Outlook: Error-mitigation?

- At PANDA startup, triple modular redundancy is probably not necessary when it comes to the FPGA configuration.

- ▶ Xilinx SEM protects the configuration (by scrubbing), and can be used in *enhanced* mode repairs some multi-bit upsets as well  $\rightarrow$  decreases uncorrectable-error rate from  $\sim \! \! 10\% \rightarrow \! \! \! \sim \! \! 2\%$  (takes up more resources). Full protection: store copy of bitstream which can replace damaged one.

### Outlook: Error-mitigation?

- At PANDA startup, triple modular redundancy is probably not necessary when it comes to the FPGA configuration.

- ▶ Xilinx SEM protects the configuration (by scrubbing), and can be used in *enhanced* mode repairs some multi-bit upsets as well  $\rightarrow$  decreases uncorrectable-error rate from  $\sim \! \! 10\% \rightarrow \! \! \! \sim \! \! 2\%$  (takes up more resources). Full protection: store copy of bitstream which can replace damaged one.

- Protection for other parts of the FPGA (like Block Memory) has to be incorporated in design.

### Outlook: Error-mitigation?

- At PANDA startup, triple modular redundancy is probably not necessary when it comes to the FPGA configuration.

- ▶ Xilinx SEM protects the configuration (by scrubbing), and can be used in *enhanced* mode repairs some multi-bit upsets as well  $\rightarrow$  decreases uncorrectable-error rate from  $\sim \! \! 10\% \rightarrow \! \! \! \sim \! \! 2\%$  (takes up more resources). Full protection: store copy of bitstream which can replace damaged one.

- Protection for other parts of the FPGA (like Block Memory) has to be incorporated in design.

- ▶ At higher luminosities, TMR might be needed.

- In any case, watch-dog mechanisms have to be included in FPGA design.

- ▶ All this should be taken into account when designing the final firmware (mitigation approach depends on which resources are used). ⇒ Topic for further discussion.

Thank you!

### Extra slide: $\sigma_{SEU}$ energy dependence