# Status of HitDetection Measurements and Next Developement Steps

Holger Flemming

May 2018

- Motivation / Concept

- Motivation

- Analogue Block

- Development History

- HitDetection Prototype V1.00

- HitDetection Prototype V2.00

- 3 HitDetection 2.00 Test and Characterisation

- ADC Characterisation

- Analogue Input Stage

- Problems

- 4 Next Steps

- Resubmission of HitDetection 2.00

- Design of Full Size Prototype

- Motivation / Concept

- Motivation

- Analogue Block

- Development History

- 3 HitDetection 2.00 Test and Characterisation

- 4 Next Steps

Courtesy of Markus Moritz, Uni Giessen

#### Required cables

|                  | ext. ADC | HitDet. |

|------------------|----------|---------|

| Analogue Signals | 16 pairs |         |

| SerialAdapter    | 4 pairs  |         |

| Serial clock     |          | 1 pair  |

| Upstream data    |          | 1 pair  |

| Downstream data  |          | 1 pair  |

|                  | 20 pairs | 3 pairs |

In additions: global clock and sync signal has to be distributed to each board

HitDetection ASIC as an integrated digitiser placed close to the front end on the back plane boards inside the barrel slice

- Less cable cross section

- Digitiser close to front end ⇒ less pick up

- Less components

- ⇒ Cheaper

- ⇒ More reliable

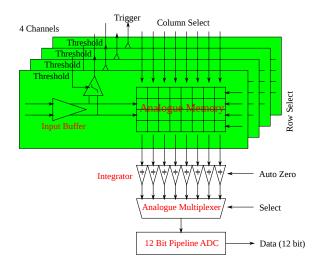

- Concept: Self triggered analogue transient recorder

- Shared ADC for many channels ⇒ high power efficiency

- 2 Development History

- HitDetection Prototype V1.00

- HitDetection Prototype V2.00

- HitDetection prototype 1.00 works

- Transients of APFEL pulses shown

- But: ADC has strong non linearities

- Real measurements are not possible

- Redesign of the 12 bit pipeline ADC  $\Rightarrow$  digital calibration

- Tape out of HitDetection prototype V 2.00

- Prototype with four analogue channels, manufactured in UMC 180 nm CMOS

- Tests and characterisation with strong support from HIM / University of Mainz

- MitDetection 2.00 Test and Characterisation

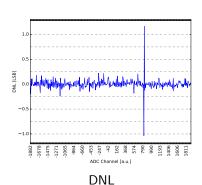

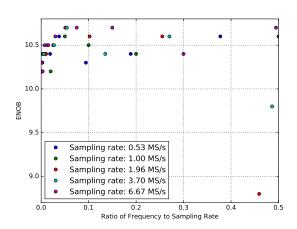

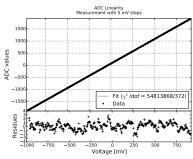

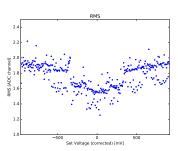

- ADC Characterisation

- Analogue Input Stage

- Problems

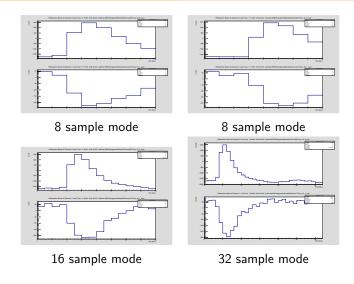

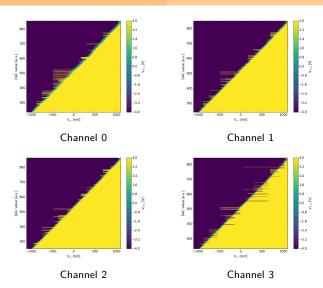

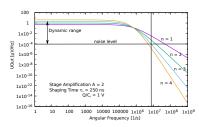

Dynamic range of ADC vs. sampling rate and input frequency

ADC DC scan

noise vs. input voltage

- Corrupted ADC Data observed in self triggered event mode

- Outcome of investigation: During chip synthesis timing model of old ADC was used

- ⇒ Unfortunately HitDetection 2 is not able to digitise and transmit recorded transients

- ⇒ No further measurements with APFEL pulses, detector tests are feasible.

- Measurement for characterisation of analogue memory by analogue test outputs is done, data not yet analysed.

- 4 Next Steps

- Resubmission of HitDetection 2.00

- Design of Full Size Prototype

- Simulations for corrected timing model completed

- Building a new Chip with existing synthesis scripts

- Next tape out deadline: July 2018

- Corrected ASIC will be available in autumn 2018.

- Full Analogue memory characterisation

- Detector tests with detector and APFEL front end

- HIM evaluates usage of HitDetection prototype for phase 0 experiment in Mainz

#### Integration Level

- Two options for placement

- Warm end of flex PCB

- Baseboard

Base board placement seems to be favoured

Base board placed HitDetection has to cope with 16 analogue channels

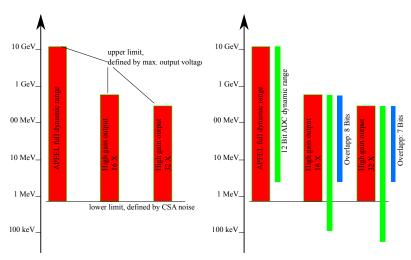

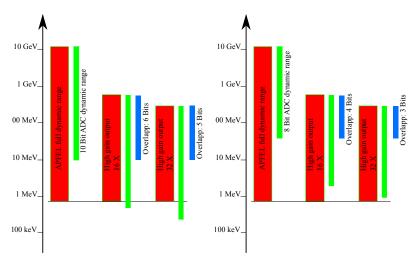

### Dynamic Range

### Dynamic Range

#### Dynamic Range

|              | gain X16 |          | gain X32 |          |

|--------------|----------|----------|----------|----------|

| ADC dynamics | Covrg.   | Overlapp | Covrg.   | Overlapp |

| 8 Bit        | 12 Bit   | 4 Bit    | 13 Bit   | 3 Bit    |

| 10 Bit       | 14 Bit   | 6 Bit    | 15 Bit   | 5 Bit    |

| 10.5 Bit     | 14.5 Bit | 6.5 Bit  | 15.5 Bit | 5.5 Bit  |

| 12 Bit       | 16 Bit   | 8 Bit    | 17 Bit   | 7 Bit    |

Required dynamic range: 13.3 Bits

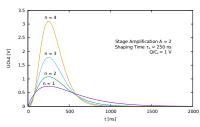

PASA output signal

PASA output spectrum

- 99.9 % of signal in the spectrum below 3.17 MHz

- $\Rightarrow$  Minimum sampling frequency:  $\approx 7 \text{ MS/s}$

- $\Rightarrow$  7 samples to cover full pulse

- $\Rightarrow$  8 sample mode would cover full pulse, but no sufficient base line coverage!

#### Required Number of ADCs per Chip

- ADC sampling rate: 33 MS/s

- Number of channels:  $n_{ch} = 16$

- Estimated mean hit rate:  $f_{hit} = 300 \text{ kHz} / \text{channel}$

- $n_S = 8$  Sample mode

- $\Rightarrow$  Required sampling rate:  $f_{Samp} = n_{ch} \cdot n_S \cdot f_{hit} = 38.4 \text{ MS/s}$

- $\Rightarrow$  2 ADCs / chip

- $n_S = 16$  Sample mode

- $\Rightarrow$  Required sampling rate:  $f_{Samp} = n_{ch} \cdot n_S \cdot f_{hit} = 76.8 \text{ MS/s}$

- $\Rightarrow$  3 / 4 ADCs / chip

#### Data rate Estimation

• Bits per Event for raw data:

| information | 8 Sam  | pl. mode | 16 Samp       | ol. mode |

|-------------|--------|----------|---------------|----------|

| channel     |        | 4        |               | 4        |

| time stamp  |        | 12       |               | 12       |

| samples     | 8 · 12 | 96       | $16 \cdot 12$ | 192      |

|             |        | 112      | -             | 208      |

- For 300 kHz event rate and 16 channels:

- $\Rightarrow$  Data rate:  $\approx$  540 MBit/s resp. 1 GBit/s

- With on-chip feature extraction: data reduction to  $\approx 180 \; \mathrm{MBit/s}$

#### I would like to thank

- Luigi Capozza

- Oliver Noll

- Phillip Grasemann

from Helmholtz institute Mainz / University of Mainz for their strong support during testing and characterisation of HitDetection V2.00

## Thank you