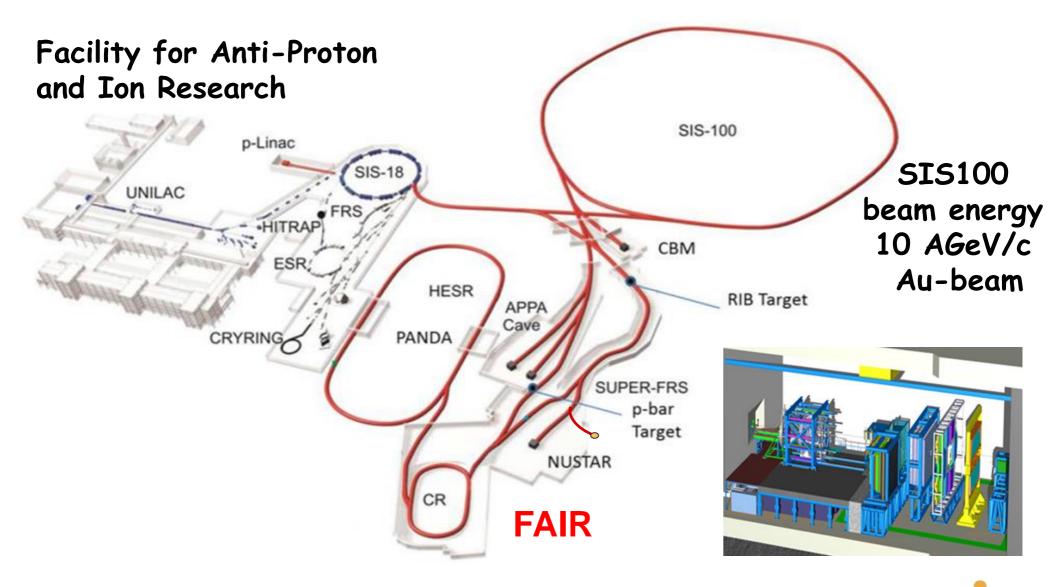

# Data preprocessing of the DAQ system for TOF detector in CBM experiment

Wenxiong Zhou, Pierre Loizeau, Jochen Frühauf, Junfeng Yang, David Emschermann, Walter F.J. Müller for the CBM collaboration

GSI Darmstadt <zhouwenxiong@cqu.edu.cn>

### Outline

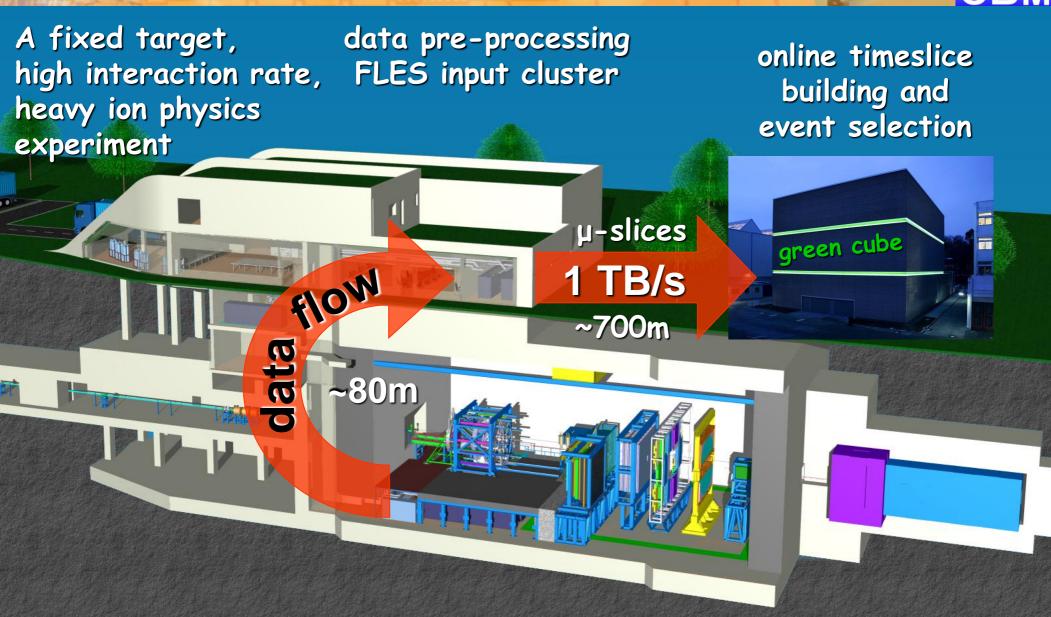

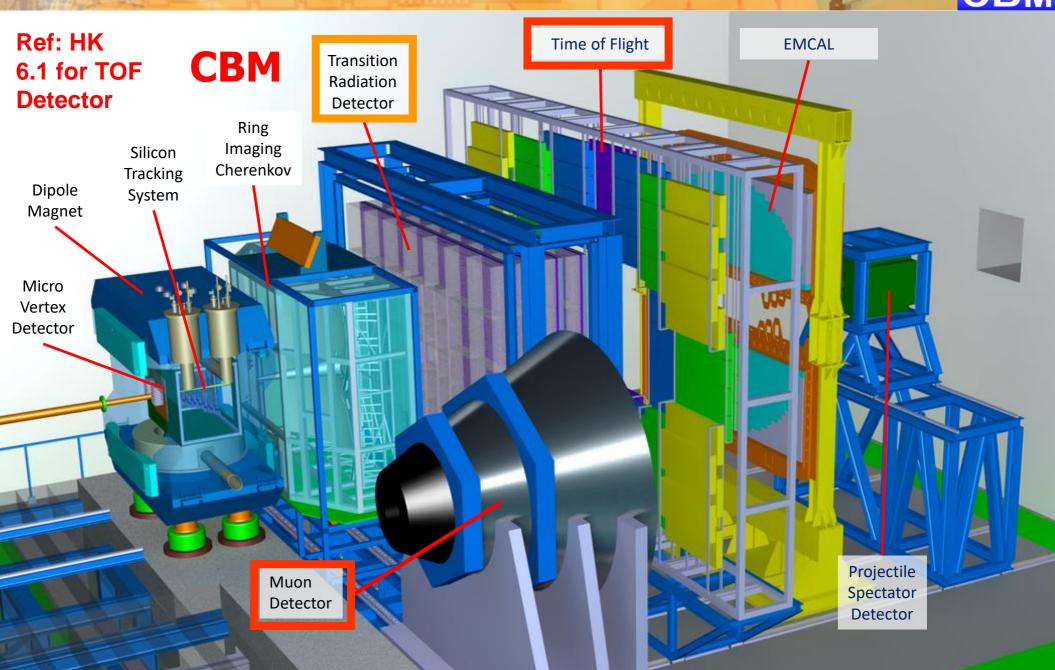

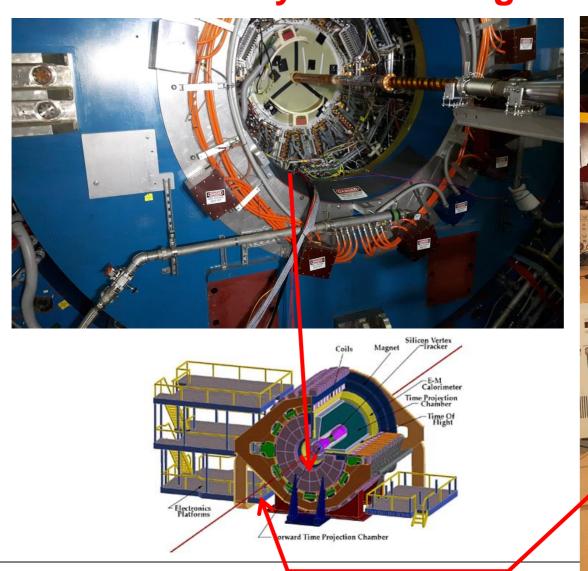

- Introduction of CBM experiment

- Structure of DAQ for TOF subsystem

- Data preprocessing strategy

- Outlook

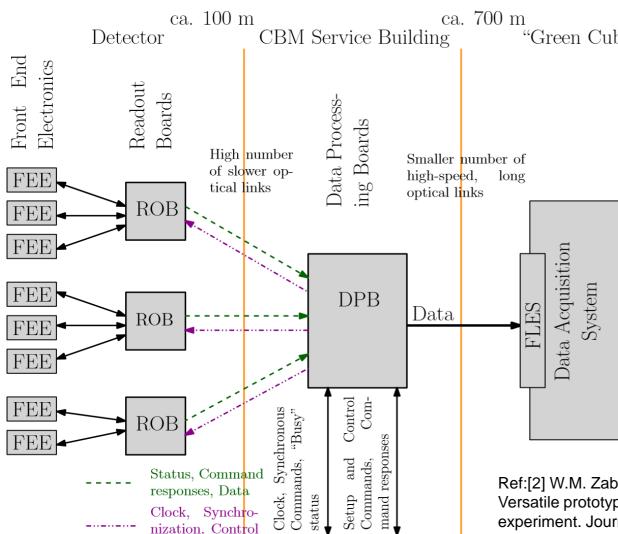

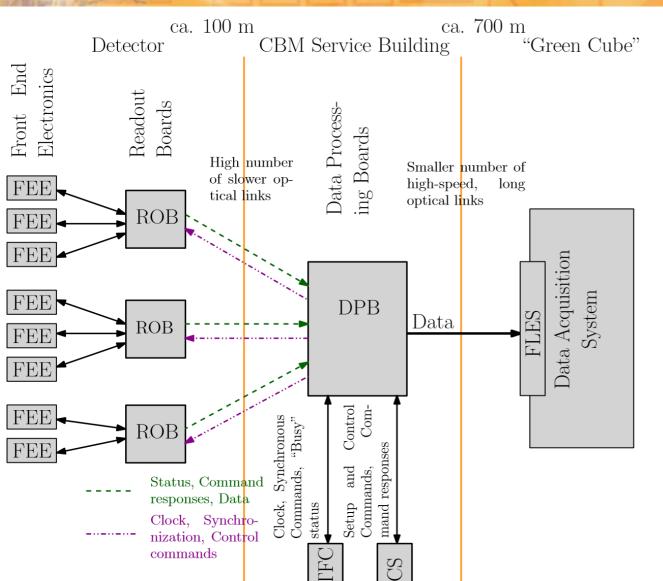

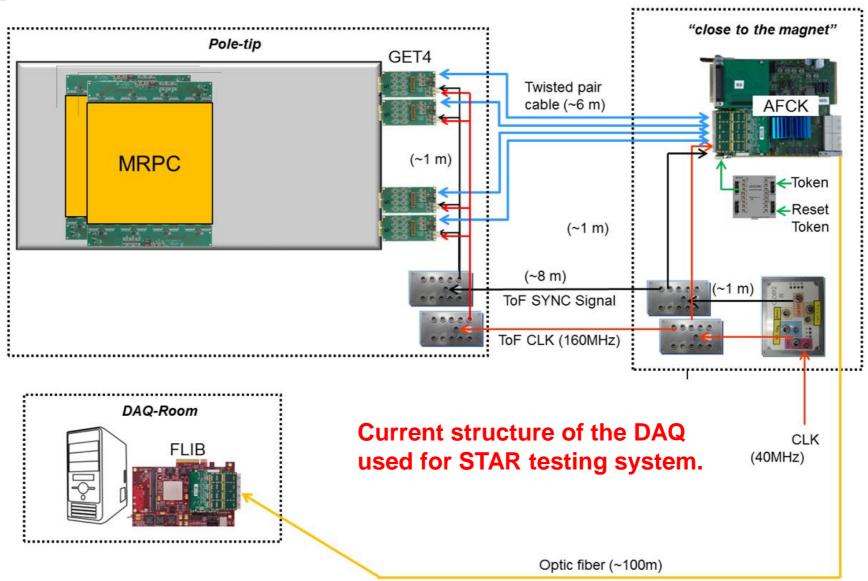

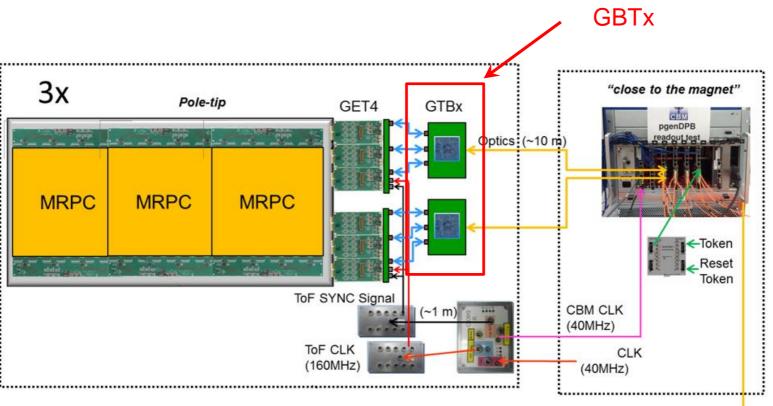

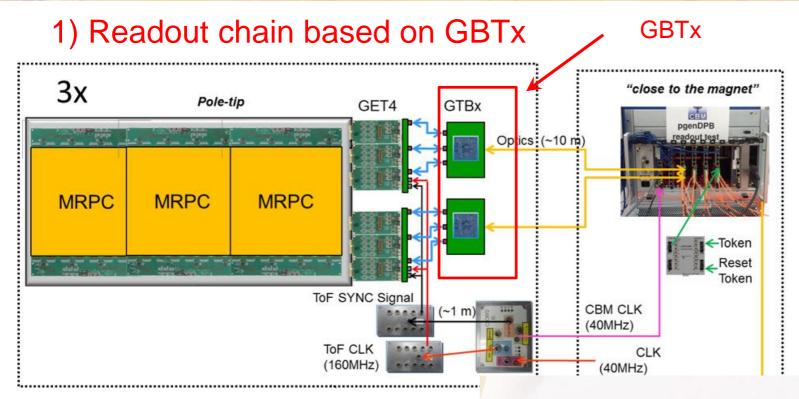

2. Structure of DAQ for TOF subsystem

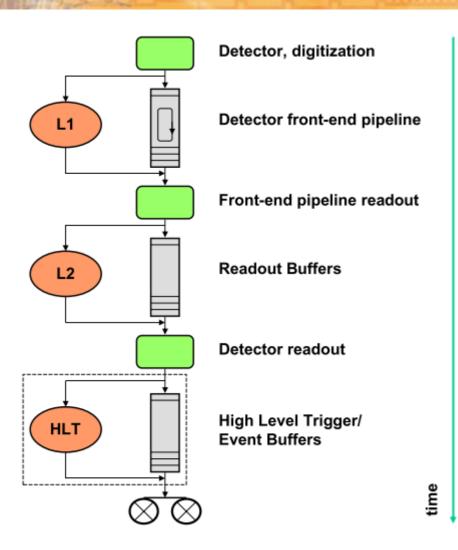

#### Conventional DAQ system:

- Multi-Level trigger system.

(several microseconds are need for level 1 triger)

- 2. Pipeline readout.

Ref:[1] V. Lindenstruth, I. Kisel, Overview of trigger systems. Nuclear Instruments and Methods in Physics Research, Section A: Accelerators, Spectrometers, Detectors and Associated Equipment. 2004, 535: 48–56.

commands

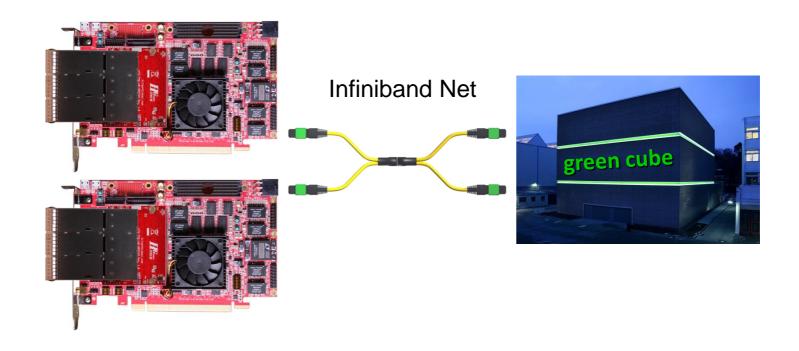

#### "Green Cube" CBM requirement:

Complex algorithms are needed for trigger.

#### Features:

- Data must have timestamp to allow event selection in computer farm.

- 2. High transfer speed is needed to acquire all the data.

Ref:[2] W.M. Zabolotny, G. Kasprowicz, A.P. Byszuk, D. Emschermann, et al., Versatile prototyping platform for Data Processing Boards for CBM experiment. Journal of Instrumentation. 2016, 11: C02031.

Ref: [3] W.F.J. Müller, The CBM experiment @ FAIR-new challenges for front-end electronics, data acquisition and trigger systems. Journal of Physics: Conference Series. 2006, 50: 371–376.

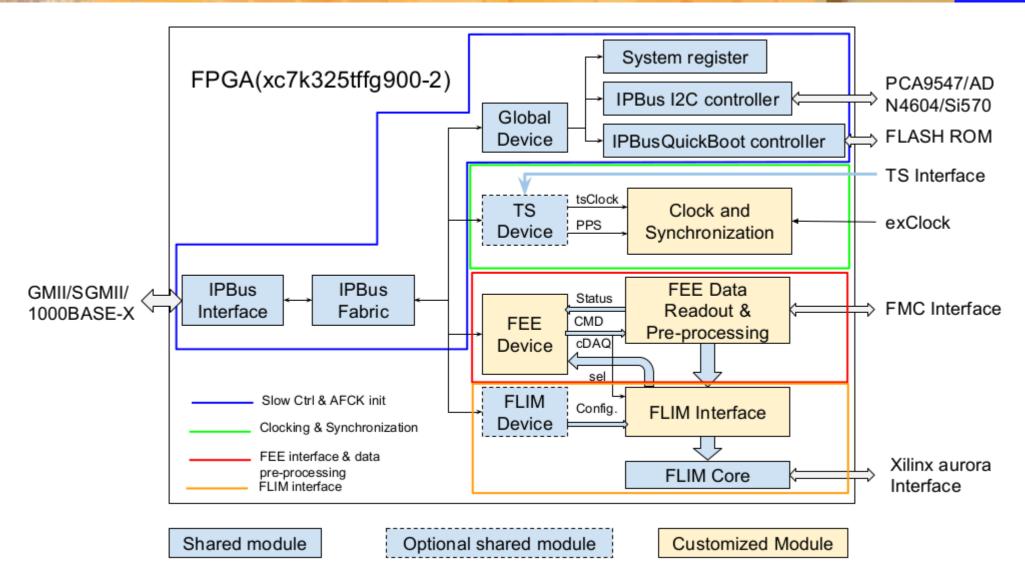

**DPB**: Data Preprocessing Board.

FLES: First Level Event Selection.

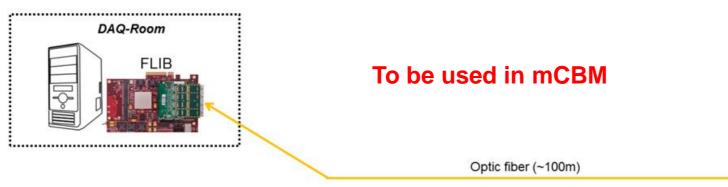

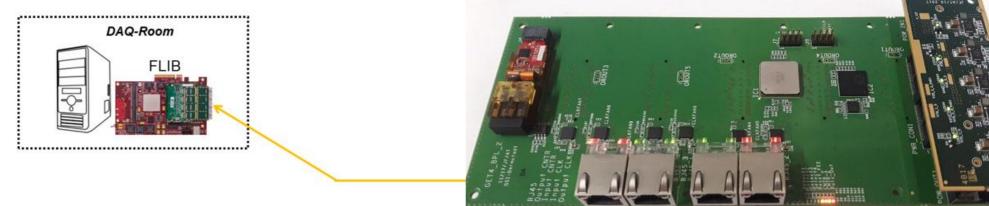

FLIB: FLES Interface Board.

**GET4:** FEE for TOF detector. There are 4 channels for one chip.

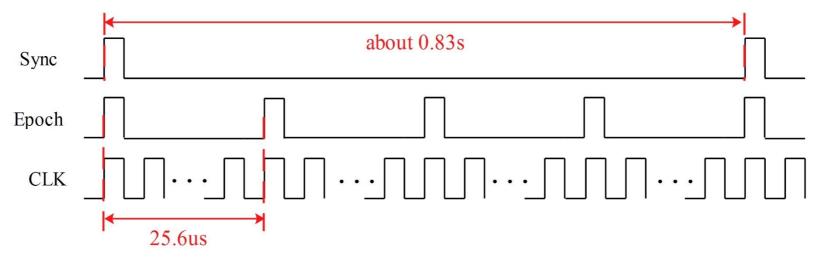

**Epoch Message**: timestamp from GET4.

Hit Message: data information from detector sent out by GET4.

MicroSlice(MS): data frame used in DPB board.

**TimeSlice**: data frame used in computer farm.

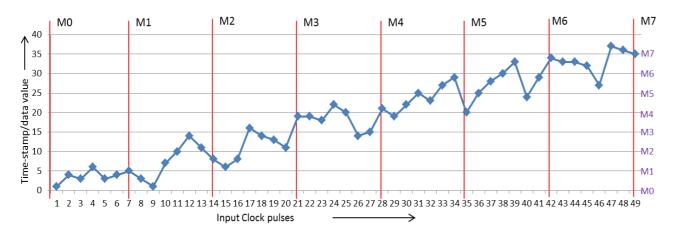

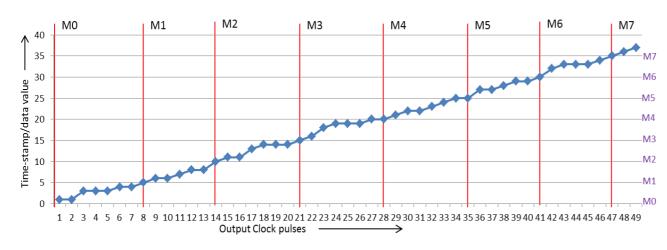

Logic of the clock, epoch and sync

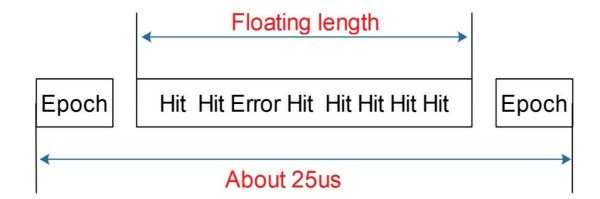

Structure of MicroSlice

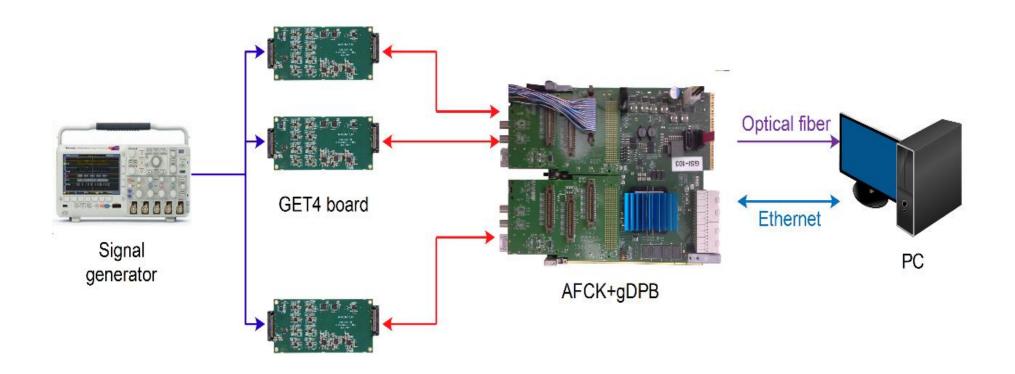

GET4 Board (8 GET4 chips/board)

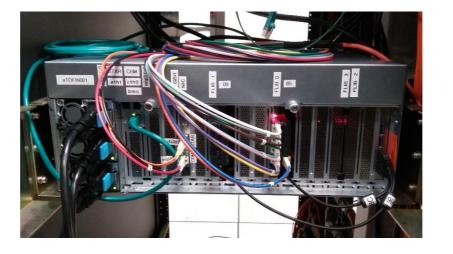

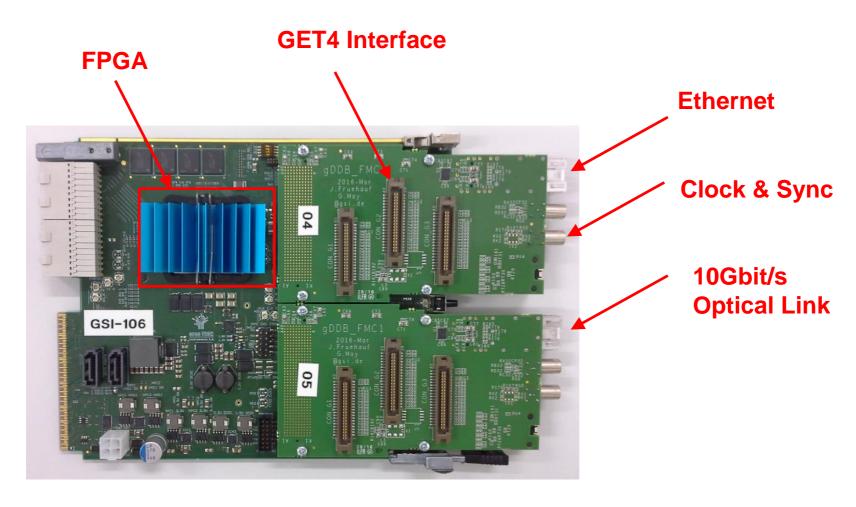

AFCK DPB Board

DAQ PC FLIB

Ref: HK 20.5 for GBTx

**FLIM**: FLES Interface Module

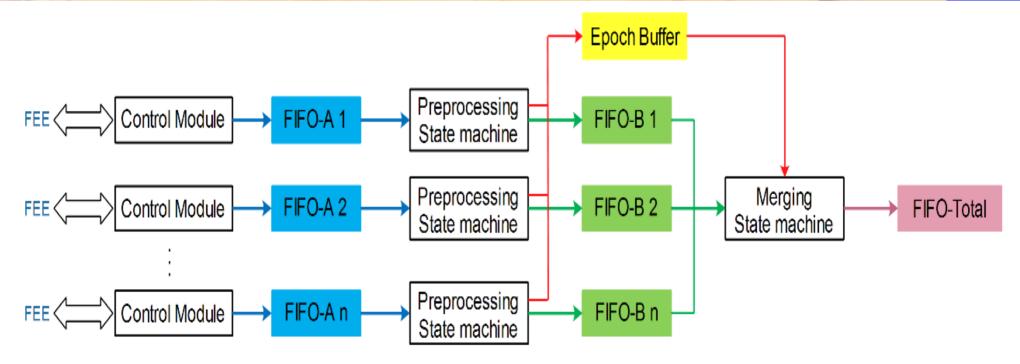

- RealMicroSlice (RealMS) basic requirements

- 1. All GET4 share one same epoch.

- 2. Hit message must be sorted at first(to be implemented).

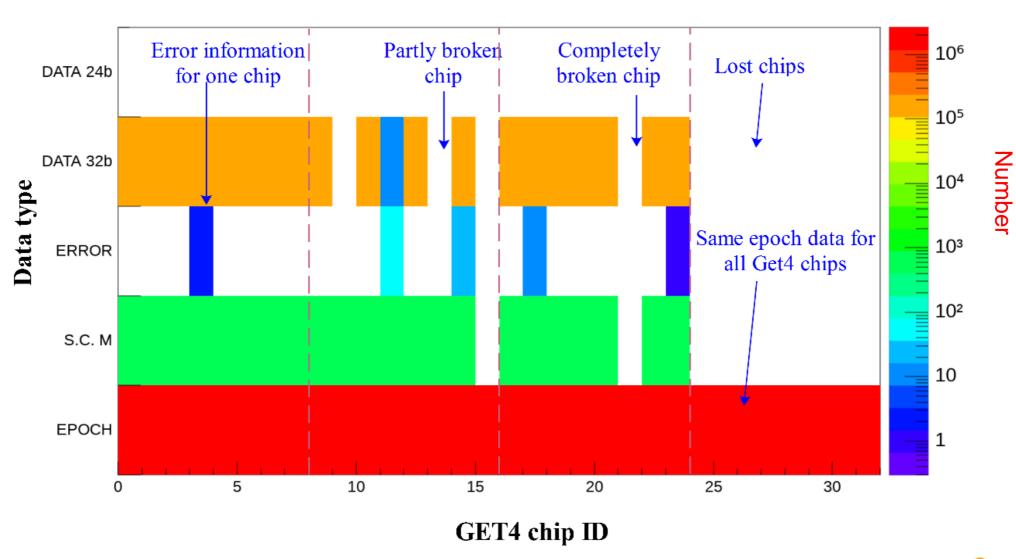

#### Requirements

- 1. Data acquisition has to detect and remove all different kinds of error:

- Epoch loss: caused by GET4 errors.

- GET4 stop sending data: because of GET4 broken.

- Corrupted data: due to interference.

- 2. Broken GET4 should be recovered if it is possible.

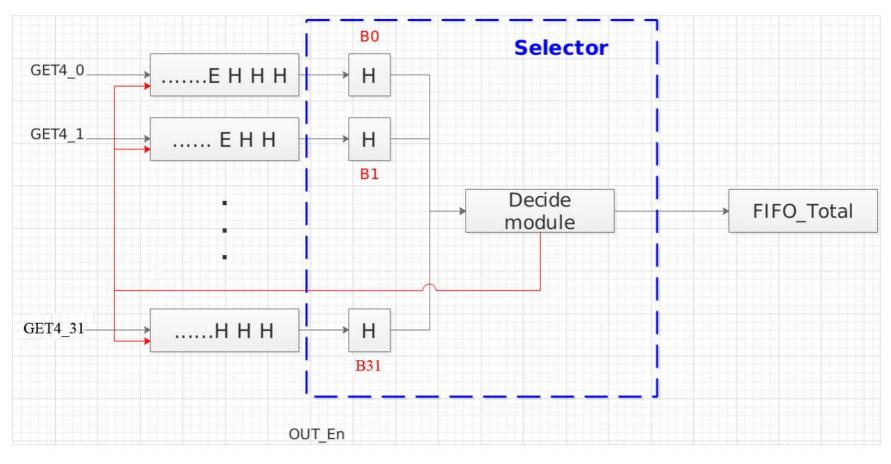

#### One possible strategy

| Input speed | Channel | Read speed      | Read clock |

|-------------|---------|-----------------|------------|

| 80Mbit/s    | <=32    | 2-3 cycle/ data | > 160MHz   |

#### Improved Data Merging strategy(It is used now)

| Input speed | Read speed   | Merging speed | Channel |

|-------------|--------------|---------------|---------|

| 80Mbit/s    | 2 cycle/data | 1 cycle /data | 64      |

#### Error detecting and removing strategy

#### **Error detection:**

- 1. There are no epoch message in one GET4 for 30µs: epoch interval time is 25.6 µs, and there may be not epoch sent out from GET4 due to chip broken.

- 2. There are mismatch for epoch: the received epoch counter number is different from the counter number got from local FPGA.

- 3. Same epochs are received from one GET4: a broken GET4 may send same epoch for several times.

- 4. Epochs are lost: the received epoch counter number is not continued.

#### **Error processing:**

- 1. Synchronization command are sent out for Error GET4 chips every **2s(lt is** also a method used to recover GET4 chips).

- 2. Remove the same epoch.

- Repair the lost epoch.

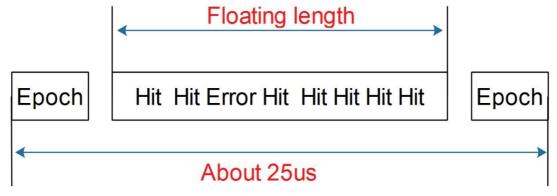

#### Real MS

- 1. All epochs are aggregated into one epoch with a special ID.

- 2. Data length is not fixed.

- 3. The interval time between two epoch marks is about 25us.

Test setup for the preprocessing firmware

S.C.M: Slow Control Message

#### **DAQ** system testing in STAR

Ref: HK 20.5 for GBTx

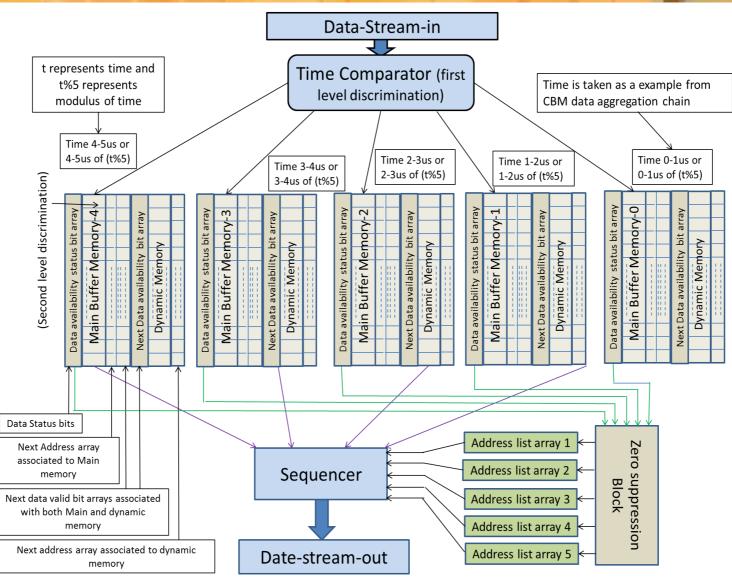

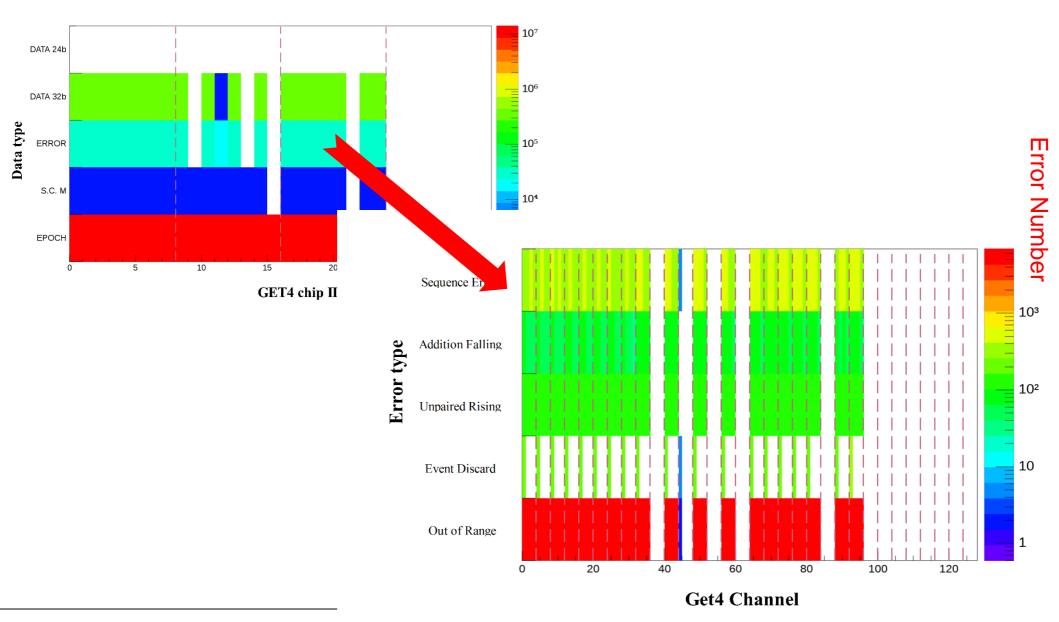

#### 2) Real-time data sorting

#### Input data

#### Reason to sort:

- Epoch message are sorted by GET4

- 2. The sequence of Hit message is disrupted when the state machine of GET4 read data from different channels.

#### 3) DAQ based on CRI

CRI = AFCK + FLIB

Ref: HK 20.5 for CRI

## Thank you!

### Backup

- SimplifiedMS

- 1. Each GET4 has their own epoch event.

- 2. Epoch event from GET4 are used directly.

- RealMS

- 1. All GET4 share one same epoch.

- 2. Hit message must be sorted at first.

### Time Slices

- Time is the only way to organize data at DAQ level

- Events ('one interaction') are defined during reconstruction

- > Time slice building instead of 'event building'

- Requirements for time slice building

- · collect all data of a time slice in one compute node

- adjacent time slices must have some small overlap {otherwise interactions at the slice boundary can not be reconstructed}

- Efficient solution

- · define a micro slice, length few usec

- macro slice is build from micro slices {e.g. 100 mirco slices with 1 micro slice overlap}

### Backup