# Back-end and interface implementation of the STS-XYTER2 prototype ASIC for the CBM experiment at FAIR

Each front-end readout ASIC for the Physics experiments requires robust and effective hit data streaming and control mechanism. A new STS/MUCH-XYTER2 fullsize prototype chip for the Silicon Tracking System and

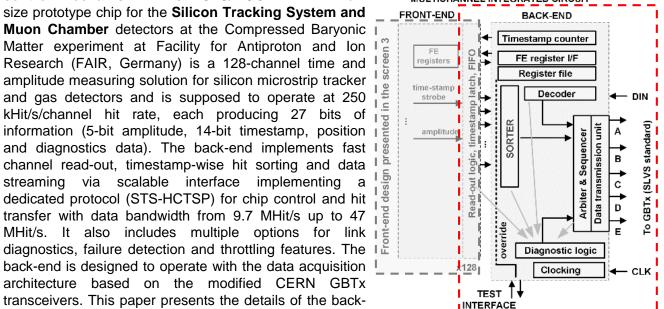

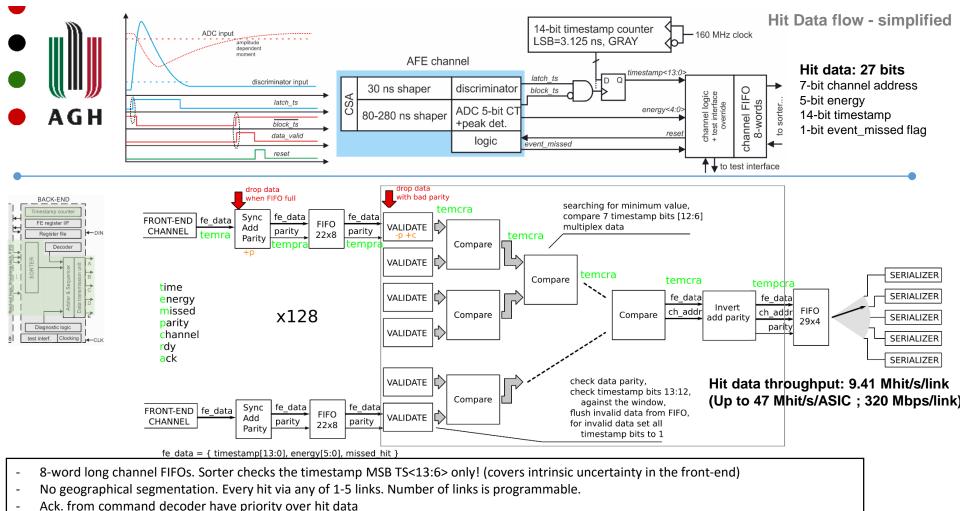

Muon Chamber detectors at the Compressed Baryonic Matter experiment at Facility for Antiproton and Ion 12 Research (FAIR, Germany) is a 128-channel time and amplitude measuring solution for silicon microstrip tracker and gas detectors and is supposed to operate at 250 kHit/s/channel hit rate, each producing 27 bits of information (5-bit amplitude, 14-bit timestamp, position 1 and diagnostics data). The back-end implements fast channel read-out, timestamp-wise hit sorting and data streaming via scalable interface implementing a dedicated protocol (STS-HCTSP) for chip control and hit transfer with data bandwidth from 9.7 MHit/s up to 47 MHit/s. It also includes multiple options for link to diagnostics, failure detection and throttling features. The

end and interface implementation in the UMC 180 nm

<sup>1</sup>AGH University of Science and Technology, Cracow, Poland

<sup>2</sup>Warsaw University of Technology, Poland

#### MULTICHANNEL INTEGRATED CIRCUIT

STS-XYTER2 CHIP (2016)

STS-HCTSP Protocol, data & control flow, diagnostic tools, throttling features...

CMOS process.

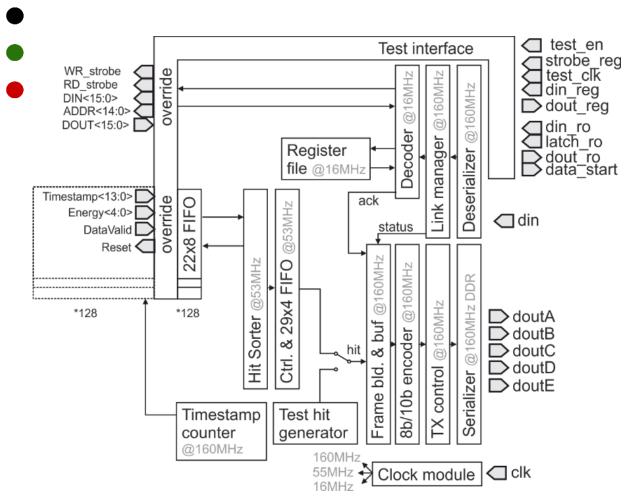

### STS-XYTER2 Back-end

Data path

Control path

Test interface

Diagnostic features

Logic triplication on control path & register file

The GBTx-based readout helps keeping the ASIC simple (e.g. no prog. delays)

K. Kasinski, R. Szczygiel, W. Zabolotny, 18th International Workshop on Radiation Imaging Detectors, Barcelona, 3-7 July 2016

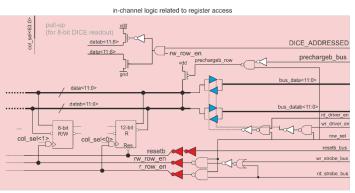

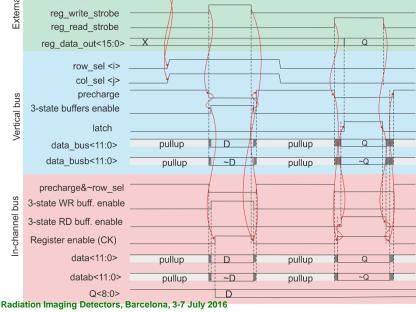

# **AFE Register access**

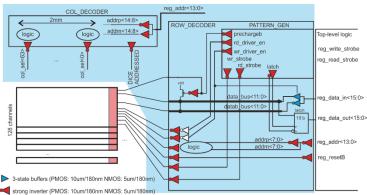

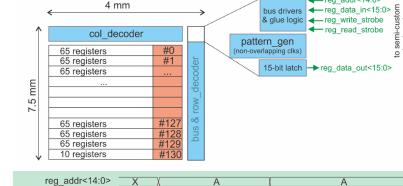

- 25 MHz clock, full-custom logic interfaced to the semi-custom back-end

- Local (in-channel) bus & global (vertical) bidir bus

- Non-overlapping clock generation & delay control

- Access to 8-bit DICE cells & 12-bit counters

- enclosed layout NMOS & guard rings

n

reg data in<15:0>

reg addr<14:0>

strong inverter (PMOS: 10um/180nm NMOS: 5um/180nm)

internal, bidirectional, complementary bus, drives the DICE SRAM cells & reads the counters (precharge & pull-up)

3-state buffers (PMOS: 10um/180nm NMOS: 5um/180nm)

K. Kasinski, R. Szczygiel, W. Zabolotny, 18th International Workshop on Radiation Imaging Detectors, Barcelona, 3-7 July 2016

# **Diagnostic features**

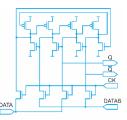

#### Test Interface:

- simple, SPI-like protocol, 20 Mbps

- overrides AFE control of the full back-end

- access to all AFE registers

- read-out of 1, selected channel

#### Aim:

- estimate digital-related noise (small number of resources are clocked, only 20 MHz clock, no 160 MHz)

- simplify initial tests

#### MUX test interface: register access WR\_strobe — RD\_strobe — DIN<15:0> — ADDR<14:0>-WR strobe RD strobe DOUT<15:0> DIN<15:0> ☐ strobe ADDR<14:0> < Clk DOUT<15:0> dout din latch dout data\_start MUX shift register Timestamp<13:0> Energy<4:0> WR\_strobe RD\_strobe DIN<15:0> ADDR<14:0> DataValid \_\_\_ top-level logic ... Reset < DOUT<15:0> 128\*Timestamp<13:0> 128\*Energy<4:0> doutC 128\*DataValid doutD doutE

## Diagnostic features:

- built-in hit generator (2 modes: via front-end, only-digital), programmable rate (1.6 – 52 Mhit/s/chip)

- test data can be random or deterministic

- test trigger for each individual channel

- multi-level software reset (forensics possible after any failure)

- SEU counter (in synthesized registers)

- Control Parity (in selected DICE Front-end registers)

- General purpose ADC for monitoring external potential (e.g. power supply)

- Link diagnostics (CRC problem, synchronization problems)

- e-fuse based chip identification (traceability database)

# Throttling features:

- Aim: cure for intensity fluctuations (controllable data drop scheme)

Method:

- decision made by master system (not the ASIC!)

- Actions possible: Flush FIFO, DAQ stop, channel mask

- ASIC provides metrics & signaling of incoming problem (alert status)

- Programmable thresholds on FIFO full, FIFO almost-full, eventmissed

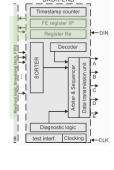

BACK-END

Timestamp counter

Diagnostic logic

Clocking

Decoder

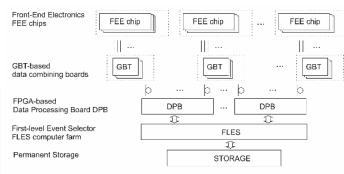

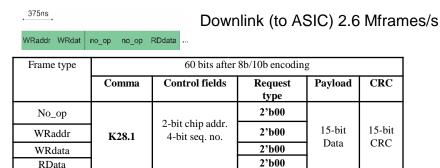

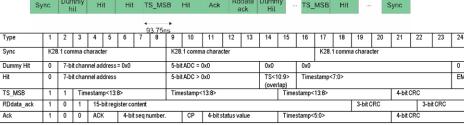

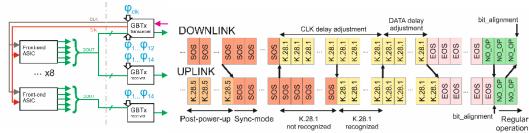

# An STS Hit & Control Transfer Synchronous Protocol (STS-HCTSP)

## Physical Interface:

- LVDS drivers, receivers

- Can operate with LVDS/SLVS signaling

- AC-coupling via high-voltage >1nF capacitors (data bandwidth)

- built-in biasing resistors > 50 kohm set biasing to 1.2V

- hardware addressing via wire-bonds

- GBTx based DAQ; 8 chips/PCB, AC-coupled links

- shared downlink (2.6 Mframes/s) & clock (160 MHz)

- Frames: 60 bits uplink / 30 bits downlink

- individual uplinks (9.4 47 Mhit/s/chip)

- simple design on the ASIC side

- novel link synchronization method

- optimization for Hit-data bandwidth (no CRC on hits, huffmann encoding, data compression)

- chip addressing via wire-bonding (HW addr)

approx, 50 us

K. Kasinski et al. A Protocol for Hit & Control Synchronous Transfer for the Front-End Electronics at the CBM Experiment, NIM-A (soon)

SOS & EOS are easily detectible even when link is not synchronized.

Uplink (from ASIC) 9.41 Mhit/s/link