## R. Kłeczek, K. Kasiński, R. Szczygieł, P. Otfinowski

{ rafal.kleczek ; krzysztof.kasinski ; robert.szczygieł ; piotr.otfinowski } @agh.edu.pl

Department of Measurement and Electronics

AGH University of Science and Technology, Av. Mickiewicza 30, 30-059 Cracow, Poland

DETECTOR

We present a complete design of the analog front-end of the STS/MUCH-XYTER2 ASIC, a full-size prototype chip for the Silicon Tracking System (based on double-sided silicon strip sensors) and Muon Chamber (gas sensors) detectors at the Compressed Baryonic Matter experiment at FAIR, Germany. The charge processing channel includes a charge sensitive amplifier. shaper amplifiers forming two signal paths for timing measurement via a fast discriminator and low-noise amplitude measurement by a 5-bit continuous-time ADC with digital peak detector. Harsh environment, different operating conditions and constraints posed by two target detector applications required flexibility and careful design to meet extended system-wise requirements. The presented circuit implements switchable shaper peaking time, gain switching and trimming, pulsed reset of the amplifier for increased input charge rate and faster recovery from overload, fail-safe measures and diagnostic modes for wafer-level and in-system testing and calibration. The power consumption is scalable (for STS and MUCH modes) but limited to 12 mW/channel.

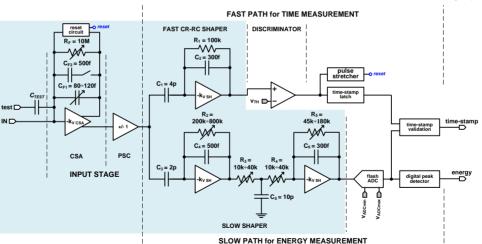

Fig. 1. The simplified architecture of the 128-channel STS/MUCH-XYTER2 ASIC.

FRONT-END

MULTICHANNEL INTEGRATED CIRCUIT

time-stamp

BACK-END

amplitude

LOGIC

ADC

LOGIC

BACK-END

Timestamp counter

FE register I/F

Register file

Decoder

This poster is focused on the front-end electronics.

Back-end part is presented in the screen 2.

### Main application requirements:

- multichannel self-triggerred architecture (50 µm pitch),

- · deposited charge time and energy measurements,

- average rate of input pulses 250 kHz/channel.

- input charge in the range (electrons and holes):

- 0.5 fC 15 fC for the STS mode,

- 1 fC 100 fC for the MUCH mode.

- itch). detector capacitance at the order of tens pF.

- low noise ENC < 1000 e- rms at C<sub>DFT</sub> = 30 pF,

- limited power consumption < 10 mW/channel</li>

- good uniformity of analog parameters between channel.

- · radiation-hardness property.

#### Readout front-end architecture:

- input stage: Charge Sensitive Amplifier + Polarity Selection Circuit,

- · fast path:

- optimized to determine the input charge arrival time with the resolution of the order of few ns,

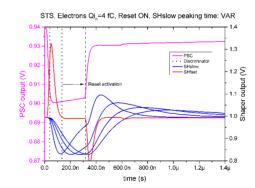

- $\bullet$  built of: CR-RC shaper with tp = 40 ns, discriminator, time-stamp latch, pulse stretcher,

#### · slow path:

- optimized for accurate energy measurement:

- built of: CR-(RC)<sup>2</sup> based shaper with switchable tp = 80, 15, 220, 280 ns, 5-bit flash ADC, digital peak detector.

Fig. 2. The simplified architecture of the single readout channel implemented in the STS/MUCH-XYTER2 ASIC.

18th International Workshop on Radiation Imaging Detectors, Barcelona, 3-7 July 2016

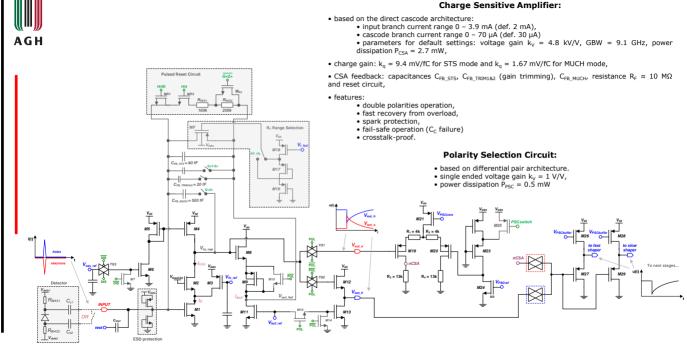

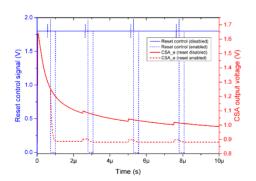

Fig. 3. The input stage architecture details: Charge Sensitive Amplifier (CSA) + Polarity Selection Circuit (PSC).

18th International Workshop on Radiation Imaging Detectors, Barcelona, 3-7 July 2016

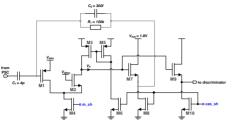

Fig. 4. Shapers' core voltage amplifier architecture.

### Shapers' core voltage amplifier:

- · based on folded cascode architecture.

- voltage gain k<sub>V</sub> = 2.5 kV/V,

- GBW = 1.3 GHz,

- power dissipation  $P_{SHcore} = 0.4 \text{ mW}.$

### Fast shaper\*:

- peaking time  $t_p$  = 30 ns, peaking time  $t_p$  = 80 ns,

- charge gain k<sub>a</sub> = 84 mV,

- charge gain k<sub>a</sub> = 40 mV,

Slow shaper\*:

- FNC = 778 e- rms. FNC = 510 e- rms.

- \* schematic level simulation, pure detector capacitance model Cour = 30 pF.

18th International Workshop on Radiation Imaging Detectors, Barcelona, 3-7 July 2016