# Data synchronisation for HEP experiments

#### Adrian Byszuk

#### Warsaw University of Technology Institute of Electronic Systems

# **Definition of synchronisation**

Types of synchronisation:

- clock/phase synchronisation (timing system)

- synchronous data transmission

- data packet synchronisation

- time synchronisation (NTP, PTP)

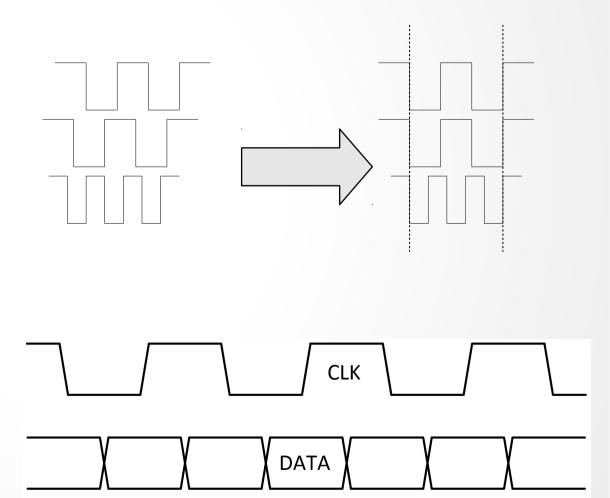

# **Clock synchronisation**

- Frequency synchronisation (syntonization)

- Phase synchronisation

- Often achieved through clock recovery circuits

- Two independent clock sources of the same frequency are not synchronised!

IEEE-SPIE Symposium Wilga 2017

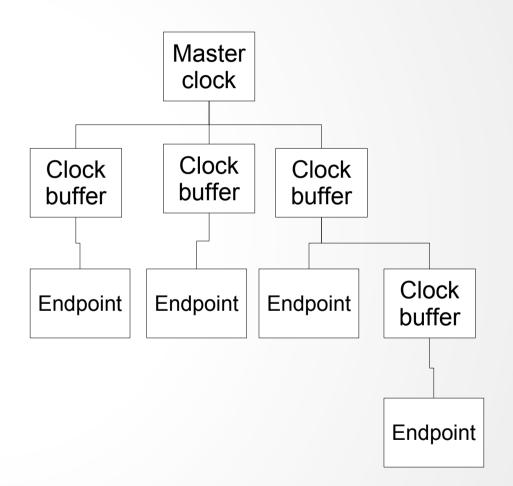

# **Clock distribution network**

- Distributing synchronous clock for the whole experiment is a challenge on its own

- Complex clock distribution networks

- Challenges: clock jitter, phase control

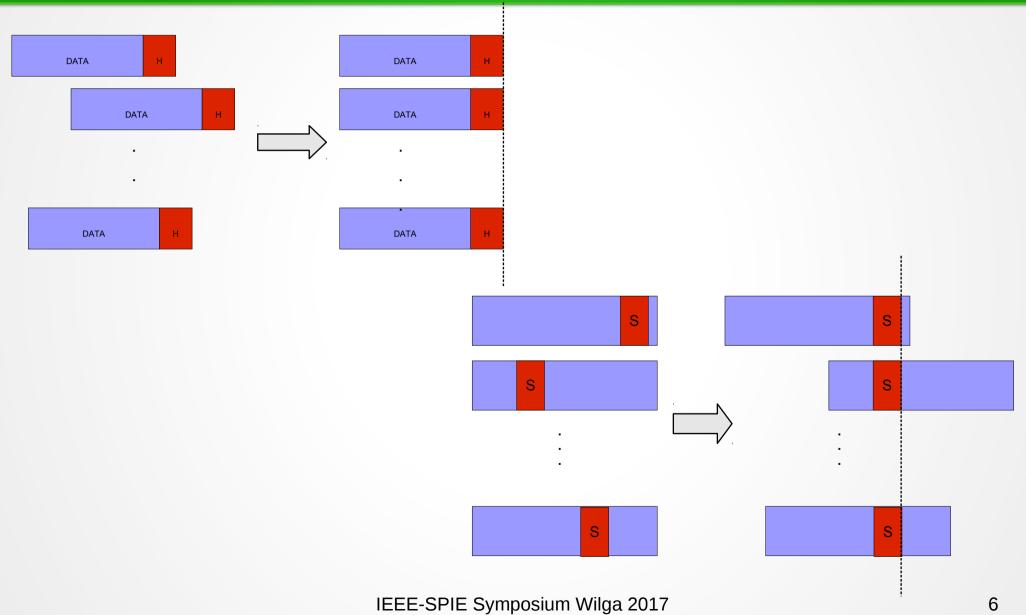

# Data packet synchronisation

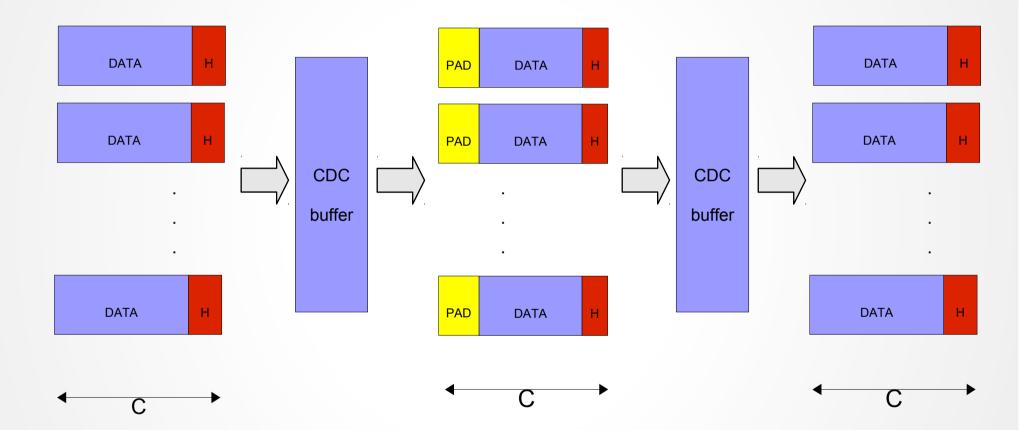

- Transmitted data is usually organized into packets of fixed length

- In multi-channel systems there is usually a need to align packet frames in time

- variable fiber length

- different source types

- inherent silicon characteristics

- Packets may contain headers, or other bitfields of superflous data which may be used as synchronisation marks

### **Data synchronisation**

# **Asynchronous links**

It is possible to send synchronous data over asynchronous link:

- data throughput of asynchronous link must be higher than that of a corespoding serial link

- async clock period must be within strict relationship with sync clock period

- data packet must contain a synchronisation marker

### **Asynchronous links**

# **Asynchronous links**

Disadvantages:

- additional circuitry needed

- higher risk of synchronisation loss

Example:

MP7 protocol (CMS) – 9.6 Gbps synchronous data stream over 10 Gbps link

# Source-synchronous links

Clock signal can be transmitted with data:

- separate clock line

- embedded in data stream

Advances in modern electronics allow for easy implementation of Clock Data Recovery (CDR) circuits. This trend becomes visible also in HEP.

Example:

GBTx ASIC from CERN (together with GBT-FPGA IP)

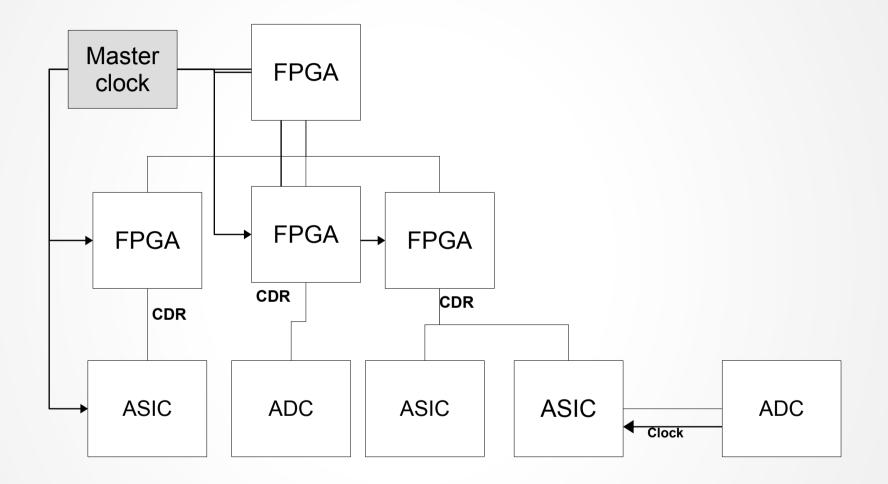

## **Mixed-mode systems**

- In practice most systems are a mix of different synchronisation techniques

- Higher-level layers are usually system synchronous or asynchronous

- Frontend components are more likely to be source-synchronous

- There is general trend towards source synchronous systems (GBT, White Rabbit)

#### **Mixed-mode systems**