# Development of FPGA based Error Resilient Self-Triggered Readout Chain for Muon Chamber (MUCH) Detector of CBM Experiment

By

Swagata Mandal

ENGG04201304002

**Variable Energy Cyclotron Center**

A thesis submitted to the

Board of Studies in Engineering Sciences

In partial fulfillment of requirements for the Degree of

**DOCTOR OF PHILOSOPHY**

of

HOMI BHABHA NATIONAL INSTITUTE

October, 2017

## STATEMENT BY AUTHOR

This dissertation has been submitted in partial fulfillment of requirements for an advanced degree at Homi Bhabha National Institute (HBNI) and is deposited in the Library to be made available to borrowers under rules of the HBNI.

Brief quotations from this dissertation are allowable without special permission, provided that accurate acknowledgement of source is made. Requests for permission for extended quotation from or reproduction of this manuscript in whole or in part may be granted by the Competent Authority of HBNI when in his or her judgment the proposed use of the material is in the interests of scholarship. In all other instances, however, permission must be obtained from the author.

Swagata Mandal

### **DECLARATION**

I, hereby declare that the investigation presented in the thesis has been carried out by me. The work is original and has not been submitted earlier as a whole or in part for a degree / diploma at this or any other Institution / University.

Swagata Mandal

### List of Publications arising from the thesis

#### Journal

- 1. **Swagata Mandal**, Rourab Paul, Suman Sau, Amlan Chakrabarti, Subhasis Chattopadhyay "A novel method for soft error mitigation in FPGA using Modified Matrix code" IEEE Embedded system letter, vol:8, pp: 65-68, issue: 8, August 2016 (DOI:10.1109/LES.2016.2603918)

- 2. **Swagata Mandal**, RourabPaul, SumanSau, AmlanChakrabarti, SubhasisChattopadhyay "Efficient dynamic priority based soft error mitigation techniques for configuration memory of FPGA hardware" Microprocessor and Microsystem, vol: 51, 2016. (https://doi.org/10.1016/j.micpro.2016.12.003)

- 3. **Swagata Mandal**, Jogender Saini, Wojciech M. Zabołotny, Suman Sau, Amlan Chakrabarti, Subhasis Chattopadhyay" An FPGA-Based High-Speed Error Resilient Data Aggregation and Control for High Energy Physics Experiment", IEEE Transaction on Nuclear Science, Vol: 64, Issue:3, 2017, DOI: 10.1109/TNS.2017.2656464.

- 4. Jogender saini, **Swagata Mandal**, Amlan Chakrabarti and Subhasis Chattopadhyay, "A real time sorting algorithm to time sort any deterministic time disordered data streams", Journal of Instrumentation (JINST), IOP Science, Vol:12, 2017

#### **Conferences**

- 1. **Swagata Mandal**, Suman Sau, Amlan Chakrabarti, Jogendra Saini, Sushanta Kumar Pal, Subhasish Chattopadhyay "FPGA based Novel High Speed DAQ System Design with Error Correction", In Proceedings of IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 2015, Montpellier, France.

- Swagata Mandal, Suman Sau, Amlan Chakrabarti, Susanta Kumar Pal, Subhasish Chattopadhyay," FPGA Implementation of High Speed Latency Optimized Optilal Communication System Based on Orthogonal Concatenated Code", In Proceedings of 24th Asian Test Symposium (ATS), 2015, IIT Bombay, India.

- 3. **Swagata Mandal**, Jogender Saini, Suman Sau, Amlan Chakrabarti, Wojciech Zabolotny, Subhasis Chattopadhyay, W. F. J. Muller," Integration of GBTx Emulator with XYTER and Data Procissing

- Board (DPB) for CBM Experiment", In proceedings of IEEE Nuclear Science Symposium, 2016, Strasbourgh, France.

- 4. **Swagata Mandal**, Wojciech Zabolotny, Suman Sau, Amlan Chakrabarti, Jogender Saini, Subhasis Chattopadhyay, Sushanta Kumar Pal, "Internal monitoring of GBTx emulator using IPbus for CBM Experiment", In Proceedings of XXXVI-th IEEE- SPIE Joint Symposium Wilga2015, Poland.

- 5. Suman Sau, **Swagata Mandal**, Jogender Saini, Amlan Chakrabarti, Subhasis Chattopadhyay," High Speed Fault Tolerant Secure Communication for MUCH using FPGA based GBTx Emulator", In Proceedings of 21<sup>st</sup> International Conference on Computing in High Energy and Nuclear Physics (CHEP 2015)' April 13-17,2015.

- 6. Swagata Mandal et.al," FPGA Emulator of GBTx for Muon Chamber (MUCH) in CBM Experiment", In Proceedings of DAE Symposium on Nuclear Physics (snp2014), December 08-12, 2014. Vanarasi. Benaras Hindu University'

- 7. Swagata Mandal et.al," Electronic Data Aggregation Architecture for High Energy Physics Big data taking Experiments", In Proceedings of DAE- BRNS Symposium on Nuclear Physics (snp2016)

Swagata Mandal

# **DEDICATIONS**

I would like to dedicate this thesis to my loving parents, colleagues and friends ...

#### **ACKNOWLEDGEMENTS**

I have been dedicated during the course of my research work and tried to give an honest effort. However, it would not have been possible without the kind support and help of many individuals and organizations. I would like to extend my sincere thanks to all of them. I am highly indebted to my supervisors Prof. Subhasis Chattopadhyay, Prof. Amlan Chakrabarti, Prof. Tapan Kumar Nayak and Shri. Singaraju Ramanarayan for their guidance and continuous support as well as for providing necessary information regarding the project \& also for their imperial hand holding in completing the project. I would like to express my gratitude towards my mother Smt. Mita Mandal, my father Shri Swapan Mandal. Their cooperation and encouragement help me to complete this project successfully. I would like to express my special gratitude and thanks to all the faculty members of VECC and my lab colleagues S/Shri Jubin Mitra, Jogender Saini, Partha Bhaskar, Shuaib Ahmad Khan and Vinod Singh Negi for giving me such attention and time.

### **Abstract**

The Compressed Baryonic Matter (CBM) experiment is one of the most important experiments at the future Facility for Antiproton and Ion Research (FAIR) in Darmstadt, Germany which is designed to detect rare particles generated during high energy and high density nucleus-nucleus collisions. Gas electron multiplier (GEM) detectors based Muon Chambers (MUCH) are used to detect muons generated during the collisions in the CBM experiment. This thesis mainly focuses on the development of Field programmable Gate Array (FPGA) based self-triggered error resilient readout chain to capture MUCH detector output that will be used during the data analysis and online computing. FPGA is used as the target device due to some of its advantages like on field programmability, inherent parallelism, runtime partial reconfigurability and easy time to market compared to application specific integrated circuits (ASICs). Front end electronics board (FEBs) in readout chain capture data directly from the detector and send it to the computing nodes using Gigabit Transceiver (GBTx) board, data processing boards (DPB) and First level interface board (FLIB) though different high speed interconnects like optical fibre and peripheral component interconnect express (PCIe). As a part of the readout chain we have developed an FPGA prototype of a high speed error resilient communication proto col termed as GBTx Protocol, which is used to transfer data from harsh radiation zone to moderate radiation zone. Though, the ASIC version of the GBTx hardware has already been developed at CERN, our work is a first of its kind FPGA implementation of the same. Proper steps have been taken to make the high speed communication robust in the radiation with stabilized latency using orthogonal concatenated code and delay and phase alignment circuit. As the FEBs work in the self-triggered mode and there i s no trigger information in the data stream we have developed an online memory management algorithm to remove the deterministic time disorder in the online data stream that helps further data analysis in the computing no des. In the first phase of our research we have developed an FPGA prototype of the readout chain comprising of FEBs, GBTx emulator, DPB and the related integration. FPGA devices are vulnerable to charge particles and they may cause soft errors in the configuration memory. In order to mitigate single and multi-bit upsets due to soft errors in the configuration memory of FPGA a novel parity based error correcting code (ECC) named as modified matrix code (MMC) and an erasure code known as EVENODD code have been used. Using frame interleaving and selective bit placement along with Hamming pro duct co de (HPC) a multi-bit adjacent ECC is proposed that enhances error correcting capability of HPC without increasing redundancy. At the same time we have proposed dynamic partial re configuration (DPR) along with a simple hardware scheduling algorithm based download manager that helps to perform the error correction in the configuration memory without suspending the operations of other hardware blocks. In general, flash memory is used to store data bits for future usage and now a day to cope up with the huge data volume designers have started to use multi-level memory cells where one memory cell can store multiple data bits instead of single bit. With the increase of memory density probability of adjacent bits being affected by radiation increases and it leads to the formation of clustered error. As traditional multi-bit ECCs are inefficient against clustered error we have proposed a novel clustered ECC using shortened product codes with simple linear block code as component codes. In a nutshell, this dissertation contributes to the state of the art research in the domain of soft error mitigation of embedded systems under radiation environment through the various new methodologies and their system level implementations that have been achieved in the due course of this research.

# Contents

| $\mathbf{C}$ | ontei                | $_{ m nts}$  |                                            | i   |

|--------------|----------------------|--------------|--------------------------------------------|-----|

| S            | ynop                 | sis          |                                            | iii |

| Li           | ist of               | Figur        | es                                         | iv  |

| Li           | ist of               | <b>Table</b> | ${f s}$                                    | x   |

| 1            | Inti                 | coduct       | ion                                        | 1   |

|              | 1.1                  | Comp         | ressed Baryonic Matter Experiment          | 2   |

|              |                      | 1.1.1        | Muon Chamber (MUCH) Detector               | 4   |

|              | 1.2                  | Archit       | tecture of Data Acquisition System         | 6   |

|              |                      | 1.2.1        | Errors in DAQ system and its mitigation    | 7   |

|              |                      | 1.2.2        | Microprocessor and Micro-controller        | 9   |

|              |                      | 1.2.3        | Application Specific Integrated Circuits   | 10  |

|              |                      | 1.2.4        | Field Programmable Gate Array (FPGAs)      | 10  |

|              |                      | 1.2.5        | FPGA Design Flow                           | 13  |

|              | 1.3                  | Resea        | rch Motivation                             | 15  |

|              | 1.4                  |              | rch Objective                              | 16  |

|              | 1.5                  | Organ        | nization of the Thesis                     | 17  |

| 2            | $\operatorname{Rel}$ | ated R       | Research Work                              | 18  |

| 3            | Inte                 | egratio      | on of MUCH-XYTER with DPB using FPGA based | ł   |

|              | GB                   | Tx Em        | nulator                                    | 32  |

|              | 3 1                  | Introd       | luction                                    | 33  |

|   |                        | CONTE                                                               | NTS   |

|---|------------------------|---------------------------------------------------------------------|-------|

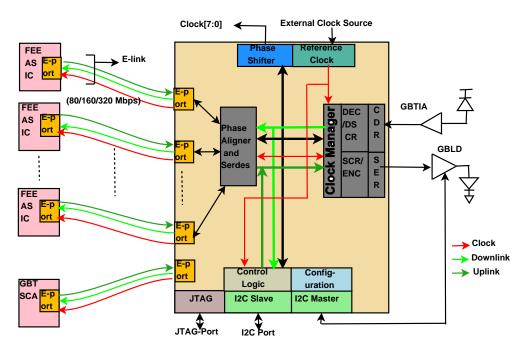

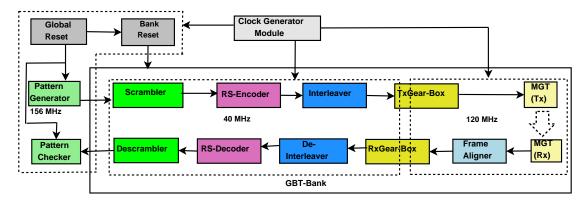

|   | 3.2                    | FPGA based GBTx Emulator                                            | . 35  |

|   | 3.3                    | Muon Chamber X-Y Time Energy Readout ASIC                           | . 47  |

|   | 3.4                    | Data Processing Board                                               | . 53  |

|   |                        | 3.4.1 Communication with time and fast control                      | . 57  |

|   |                        | 3.4.2 Communication through slow control interface                  | . 58  |

|   | 3.5                    | Integration of DPB with MUCH-XYTER using GBTx Emulator              | . 65  |

|   | 3.6                    | Results and Performance Analysis                                    | . 69  |

|   | 3.7                    | Conclusion                                                          | . 76  |

| 4 | $\mathbf{A}\mathbf{n}$ | FPGA based High Speed Error resilient Data Aggregation              | n     |

|   | and                    | Control System for Radiation Environment                            | 77    |

|   | 4.1                    | Introduction                                                        | . 78  |

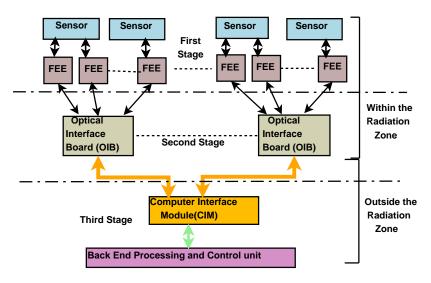

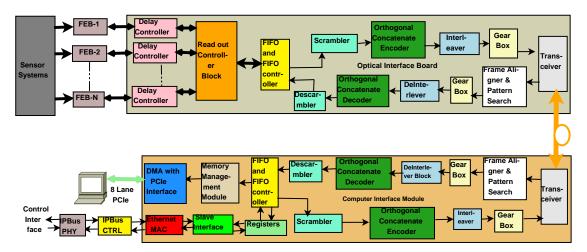

|   | 4.2                    | System Design for High Speed DAQ                                    | . 80  |

|   |                        | 4.2.1 Optical Interface Board (OIB)                                 | . 82  |

|   |                        | 4.2.1.1 Frame Aligner and Pattern Search Block                      | . 88  |

|   |                        | 4.2.2 Computer Interface Module(CIM)                                | . 89  |

|   |                        | 4.2.3 Overview of the data flow                                     | . 100 |

|   | 4.3                    | Latency Optimization                                                | . 102 |

|   | 4.4                    | Error Mitigation in FPGA devices                                    | . 105 |

|   | 4.5                    | Results and Performance Analysis                                    | . 106 |

|   | 4.6                    | Conclusion                                                          | . 113 |

| 5 | Lat                    | ency optimized clustered error correction for mult-level men        | n-    |

|   | $\mathbf{ory}$         | chips using LSBCPC                                                  | 114   |

|   | 5.1                    | Introduction                                                        | . 115 |

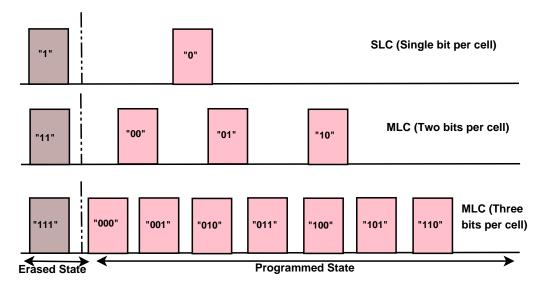

|   | 5.2                    | MLC NAND FLASH Memory Background                                    | . 117 |

|   |                        | 5.2.1 Error distribution in MLC Flash                               | . 121 |

|   | 5.3                    | Linear Shortened Block code based Product code                      | . 122 |

|   | 5.4                    | ${\tt Encoding/Decoding}$ using LSBCPC and its hardware implementa- |       |

|   |                        | tion                                                                | . 131 |

|   | 5.5                    | Results and Performance Analysis                                    | . 136 |

|   |                        | 5.5.1 Cost Analysis                                                 | . 142 |

|   | 5.6                    | Conclusion                                                          | . 145 |

### CONTENTS

| 6                | Soft error mitigation in Configuration memory of FPGA using |                                                               |            |  |

|------------------|-------------------------------------------------------------|---------------------------------------------------------------|------------|--|

|                  | HP                                                          | C with selective bit placement and Frame Interleaving 14      | 16         |  |

|                  | 6.1                                                         | Introduction                                                  | 47         |  |

|                  | 6.2                                                         | Proposed Hamming Product code with frame interleaving and se- |            |  |

|                  |                                                             | lective bit placement                                         | 48         |  |

|                  |                                                             | 6.2.1 Selective bit placement strategy                        | 50         |  |

|                  | 6.3                                                         | Hardware implementation of HPCFISBP                           | 60         |  |

|                  | 6.4                                                         | Result and Performance Analysis                               | 63         |  |

|                  | 6.5                                                         | Conclusion                                                    | 68         |  |

| 7                | Effi                                                        | cient Dynamic Priority Based Soft Error Mitigation Tech-      |            |  |

|                  | niq                                                         | ues For Configuration Memory of FPGA Hardware                 | 39         |  |

|                  | 7.1                                                         | Introduction                                                  | 70         |  |

|                  | 7.2                                                         | Proposed Modified Matrix Code Algorithm                       | <b>7</b> 3 |  |

|                  | 7.3                                                         | Error Detection using Interleaved MMC                         | 80         |  |

|                  | 7.4                                                         | Error Detection and correction using EVENODD coding 18        | 83         |  |

|                  |                                                             | 7.4.1 Overview of EVENODD coding                              | 83         |  |

|                  |                                                             | 7.4.2 Recovery based on EVENODD code                          | 85         |  |

|                  | 7.5                                                         | Dynamic Priority Based Algorithm for download manager 19      | 92         |  |

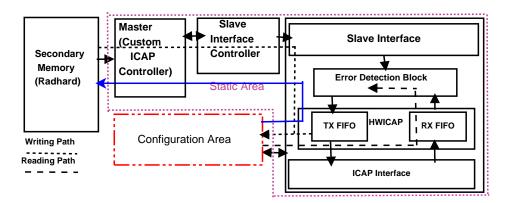

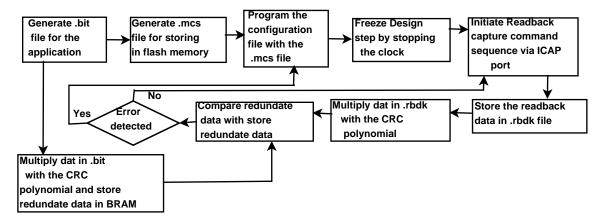

|                  | 7.6                                                         | Hardware Implementation and its workflow                      | 95         |  |

|                  | 7.7                                                         | Result and Performance Analysis                               | 97         |  |

|                  |                                                             | 7.7.1 Comparison With existing Error correcting models 19     | 98         |  |

|                  |                                                             | 7.7.2 System Recovery Time                                    | 04         |  |

|                  | 7.8                                                         | Conclusion                                                    | 06         |  |

| 8                | Cor                                                         | aclusion and Future Scope 20                                  | )7         |  |

| $\mathbf{R}_{i}$ | efere                                                       | ences 21                                                      | 10         |  |

# List of Figures

| 1.1 | Fixed Target Experiment vs Collider Experiment                       | 3  |

|-----|----------------------------------------------------------------------|----|

| 1.2 | Detector system in CBM experiment [12]                               | 4  |

| 1.3 | Schematic view of MUCH detector with segmented absorber $[13]$ .     | 5  |

| 1.4 | Basic structure of single layer GEM detector                         | 5  |

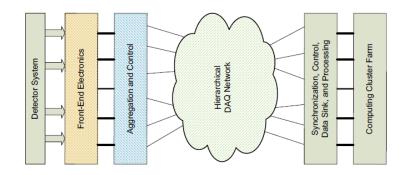

| 1.5 | Traditional DAQ network architecture [18]                            | 6  |

| 1.6 | Planned Building and Cave Infrastructure for CBM Experiment [12]     | 7  |

| 1.7 | Performance-flexibility graph among ASIC, FPGA and general           |    |

|     | purpose processor                                                    | 11 |

| 1.8 | A Generic FPGA internal Architecture                                 | 11 |

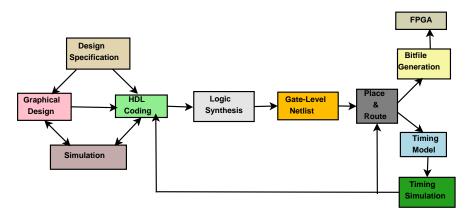

| 1.9 | HDL based design flow for FPGA based system design                   | 14 |

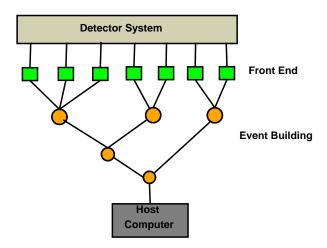

| 2.1 | Tree like distributed DAQ architecture                               | 19 |

| 2.2 | Schematic overview of Atlas experiment in $CERN$ [37]                | 21 |

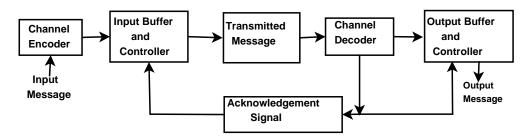

| 2.3 | Basic architecture of ARQ based communication system                 | 25 |

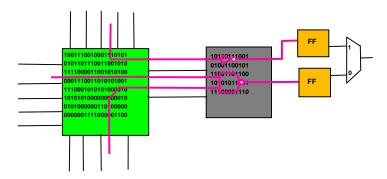

| 2.4 | Implementation of NAND and NOT logic in an FPGA $\dots$              | 28 |

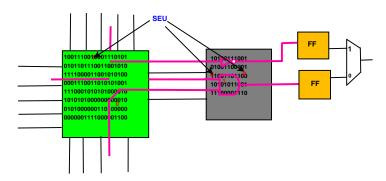

| 2.5 | SEU causes error in routing logic and NAND gate in an FPGA           | 28 |

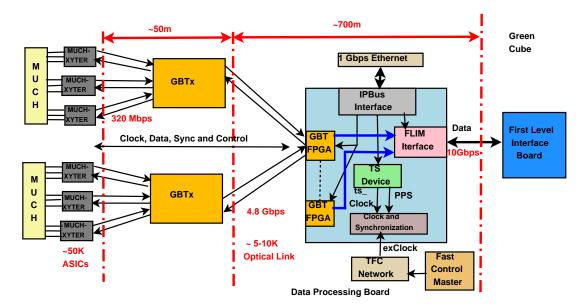

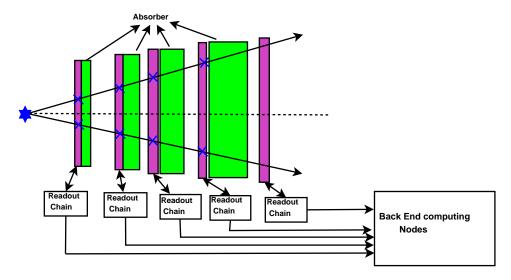

| 3.1 | Schematic diagram of the read out chain for MUCH detector            | 35 |

| 3.2 | GBTx ASIC internal architecture and interfaces [104]                 | 36 |

| 3.3 | Internal modules of a GBT-Bank in GBTx Emulator                      | 38 |

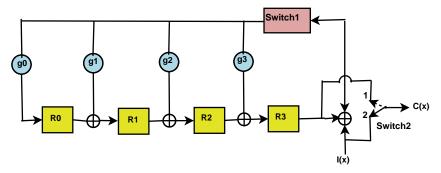

| 3.4 | Architecture for a systematic RS(15,11) encoder                      | 40 |

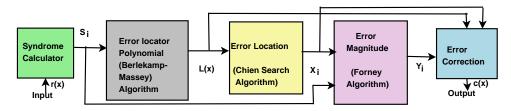

| 3.5 | Different steps of RS decoding algorithm                             | 41 |

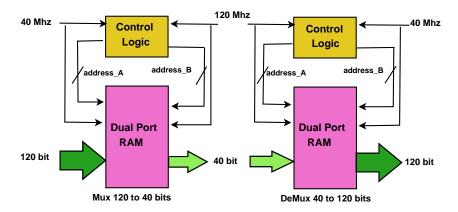

| 3.6 | Functionalities of Gearbox                                           | 42 |

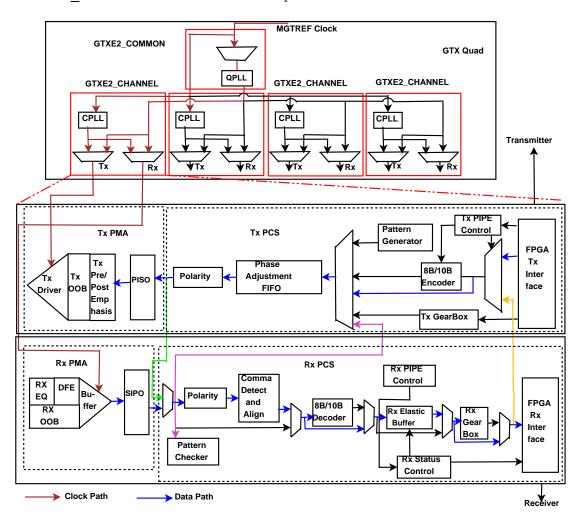

| 3.7 | Architecture of transceiver of GBTx Emulator                         | 43 |

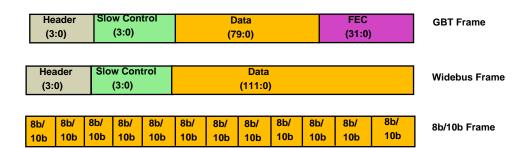

| 3.8 | Different frame format for data transmission over optical link [104] | 45 |

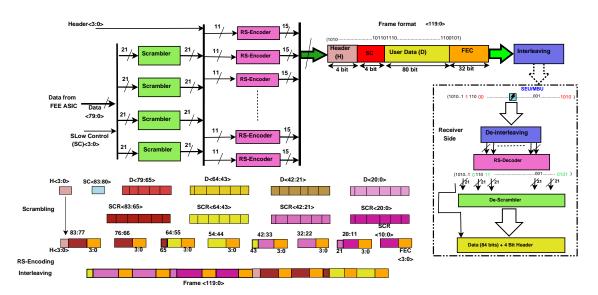

| 3.9  | Steps of generation of GBT Frame during data transmission                          | 46 |

|------|------------------------------------------------------------------------------------|----|

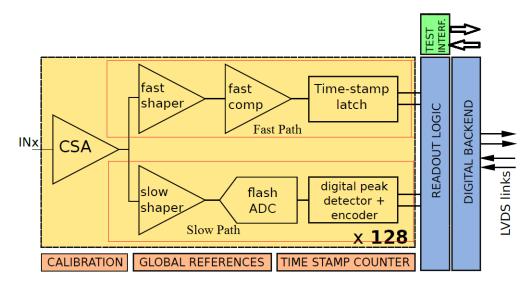

| 3.10 | Internal architecture of each channel of MUCH-XYTER                                | 48 |

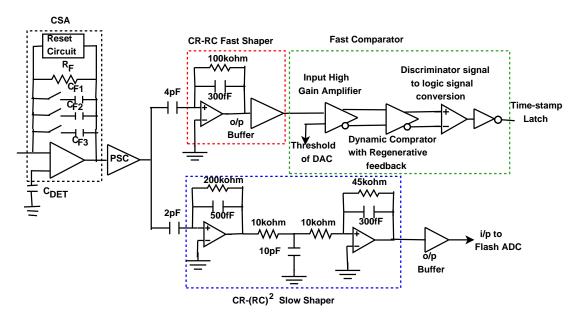

| 3.11 | Details architecture of analog front end of MUCH-XYTER $$                          | 49 |

| 3.12 | $\operatorname{MUCH}$ with segregated absorber and multiple GEM detector           | 50 |

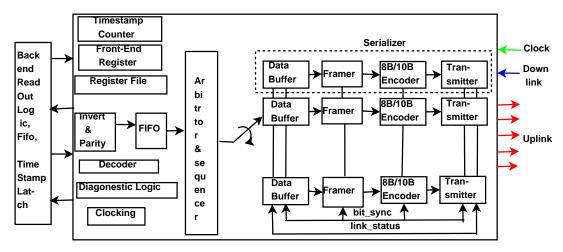

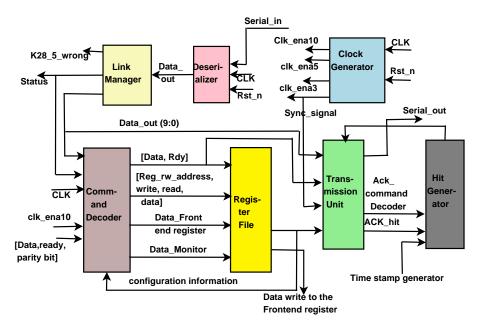

| 3.13 | Digital back-end of MUCH-XYTER ASIC [108]                                          | 51 |

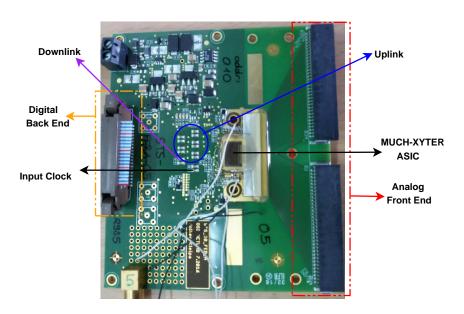

| 3.14 | Top view of FEB containing MUCH-XYTER ASIC                                         | 51 |

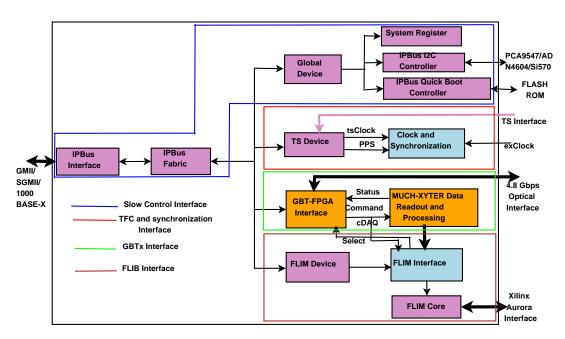

| 3.15 | DPB Firmware structure                                                             | 55 |

| 3.16 | Top view of AFCK board                                                             | 56 |

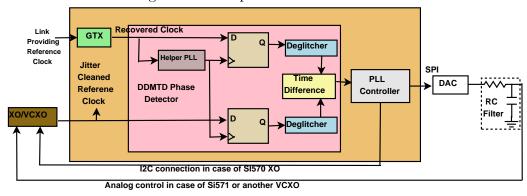

| 3.17 | Clock Recovery and jitter cleaning circuit of AFCK                                 | 56 |

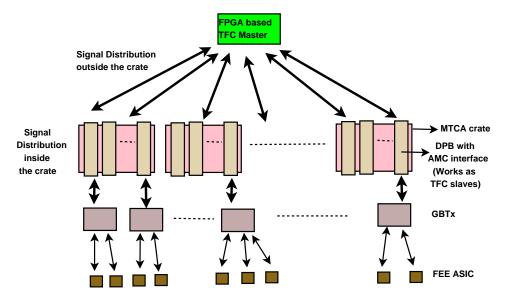

| 3.18 | TFC system topology                                                                | 58 |

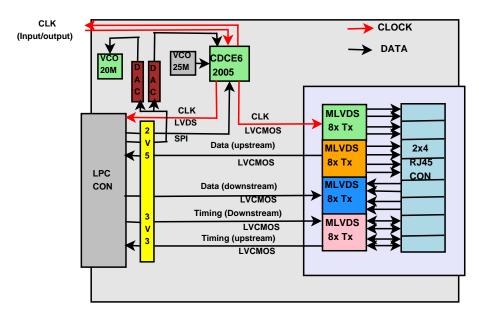

| 3.19 | Internal architecture of TFC master prototype [116]                                | 59 |

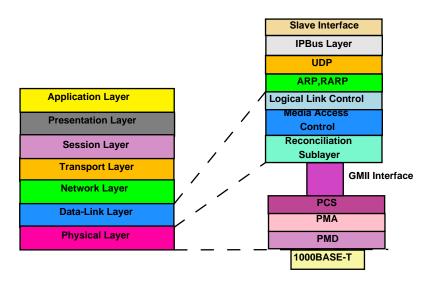

| 3.20 | Implementation of IPBus protocol using standard OSI model                          | 60 |

| 3.21 | Standard Ethernet Frame Format                                                     | 60 |

| 3.22 | Architecture of IPBus controller and its interfacing with registers                | 62 |

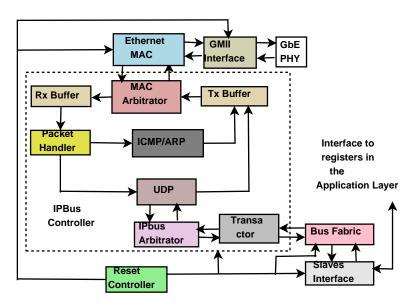

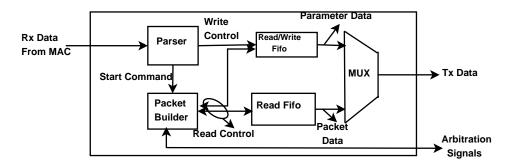

| 3.23 | Architecture of FPGA based UDP/IP stack                                            | 63 |

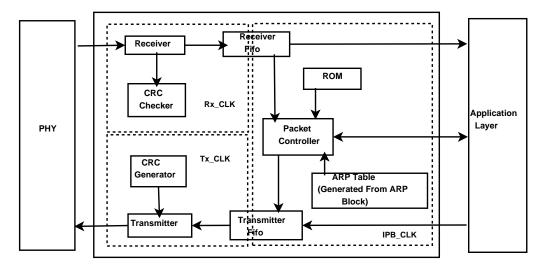

| 3.24 | Internal Architecture of ARP block                                                 | 64 |

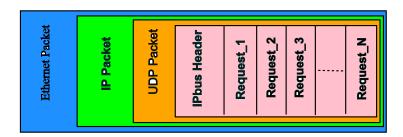

| 3.25 | Packet format generated using IPbus protocol                                       | 64 |

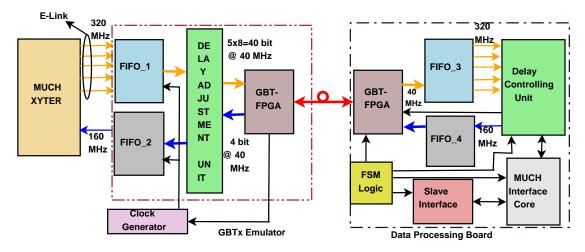

| 3.26 | Interfacing of MUCH-XYTER with DPB using GBTx Emulator $% \left( 1,,N\right) =0$ . | 65 |

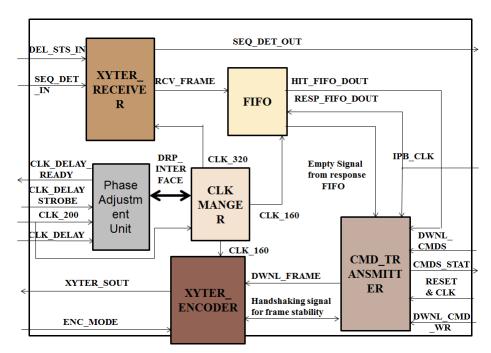

| 3.27 | Internal Architecture of MUCH Interface core                                       | 66 |

| 3.28 | Uplink frame format after $8B/10B$ encoding                                        | 68 |

| 3.29 | Downlink frame format after $8B/10B$ encoding [108]                                | 68 |

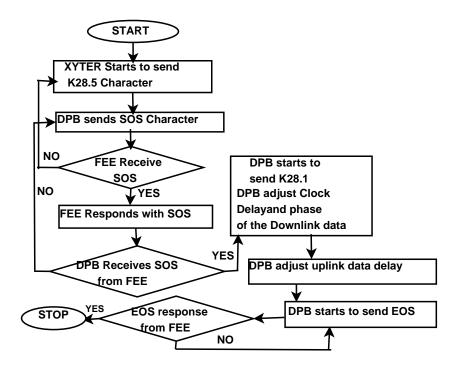

| 3.30 | Flowchart for synchronous communication over E-Link                                | 69 |

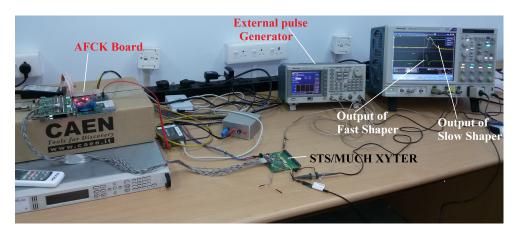

| 3.31 | Setup for testing MUCH-XYTER using DPB                                             | 70 |

| 3.32 | (a) Fast shaper output with positive pulse (b) negative pulse                      | 71 |

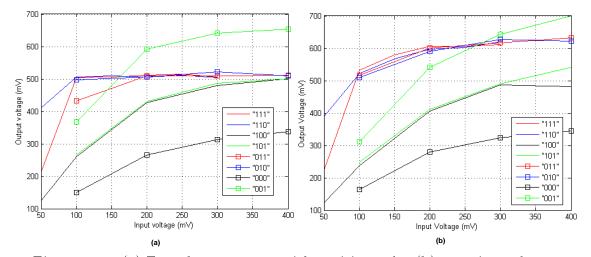

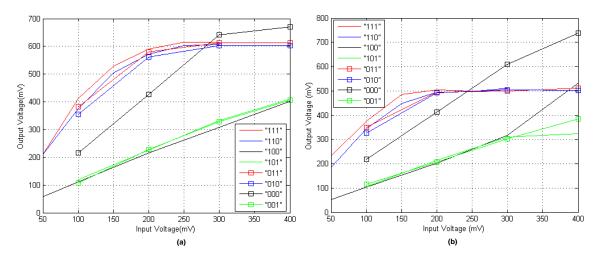

| 3.33 | (a) Slow shaper output with positive pulse (b) negative pulse                      | 72 |

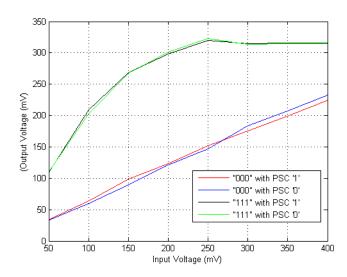

| 3.34 | Variation of output voltage of slow shaper with polarity switch and                |    |

|      | feedback capacitance of CSA                                                        | 73 |

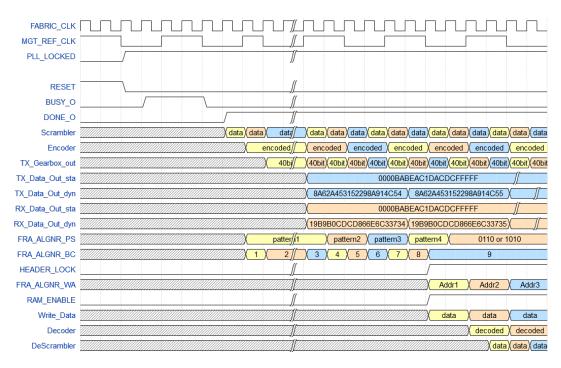

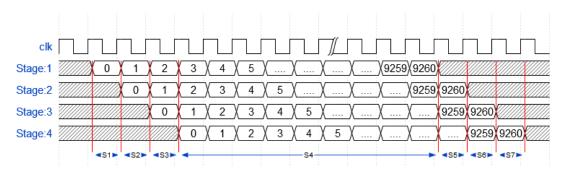

| 3.35 | Timing diagram of the transmitter and receiver signals                             | 74 |

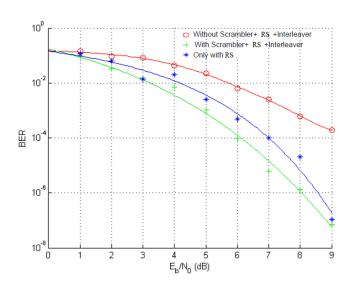

| 3.36 | Study of of BER of GBT link using MATLAB simulation                                | 76 |

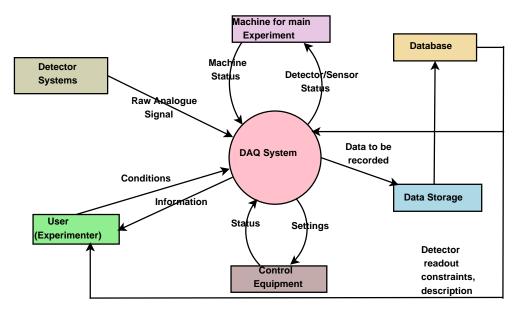

| 4.1  | General DAQ system and its surroundings                                            | 79 |

| 4.2  | Simplified read out chain for multistage data acquisition system .                 | 81 |

| 4.3  | FPGA based readout chain prototype having single OIB and CIM                       | 82 |

| 4.4  | Internal architecture of FPGA based FEB emulator                       | 83               |

|------|------------------------------------------------------------------------|------------------|

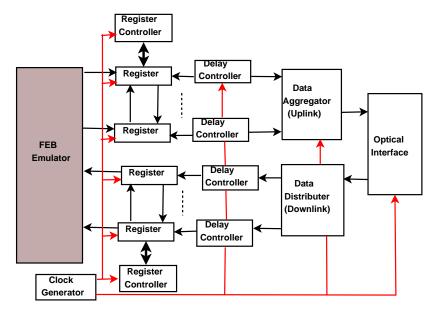

| 4.5  | Interfacing of FEB emulator with optical module in OIB                 | 84               |

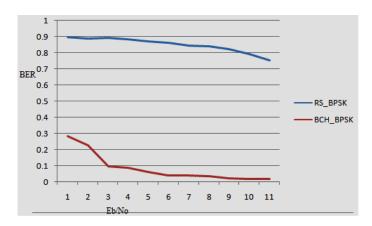

| 4.6  | BER performance of BCH and RS code against random error using          | 01               |

| 1.0  | BPSK modulation [124]                                                  | 86               |

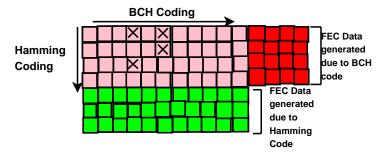

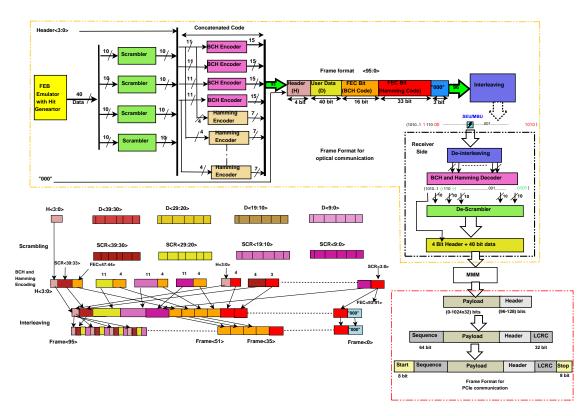

| 4.7  | Concatenate code using Hamming and BCH code                            | 86               |

| 4.8  | Helical Interleaving Process                                           | 87               |

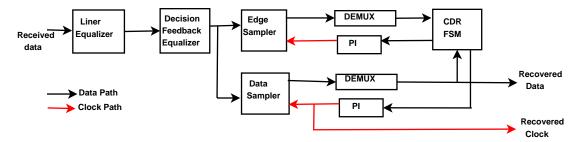

| 4.9  | Internal architecture of CDR circuit in the Xilinx Transceiver         | 88               |

| 4.10 | (a) Algorithm for Frame Aligner and Pattern Search (b) Data flow       | 00               |

| 1.10 | diagrams of the Frame Aligner and Pattern Search block                 | 89               |

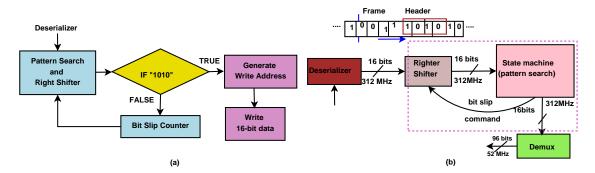

| 4.11 |                                                                        | 00               |

| 7.11 | pletion TLP (c) Structure of TLP packet after passing through          |                  |

|      | physical layer                                                         | 91               |

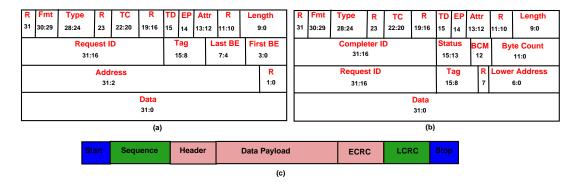

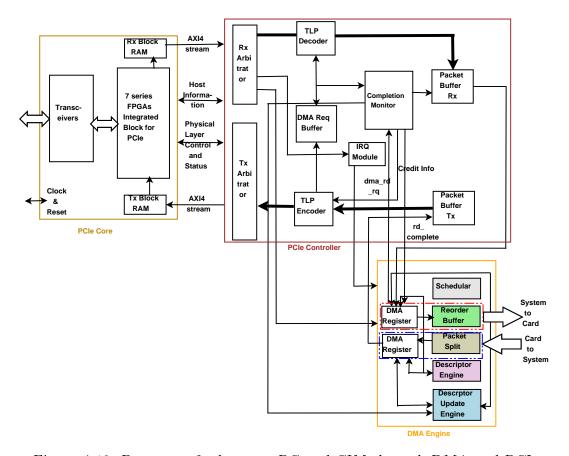

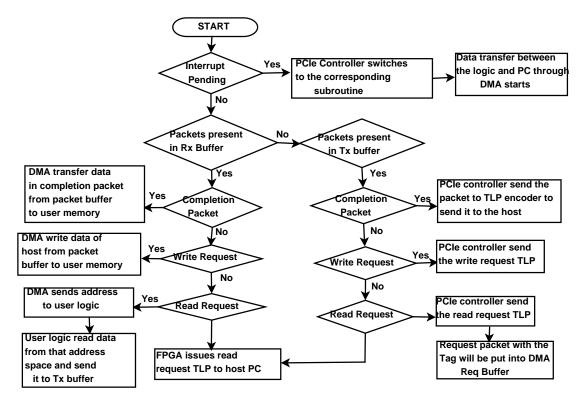

| 4 19 | Data transfer between PC and CIM through DMA and PCIe                  | 92               |

|      | Flow chart for data transfer between host PC and CIM through           | J                |

| 4.10 | PCIe and DMA                                                           | 93               |

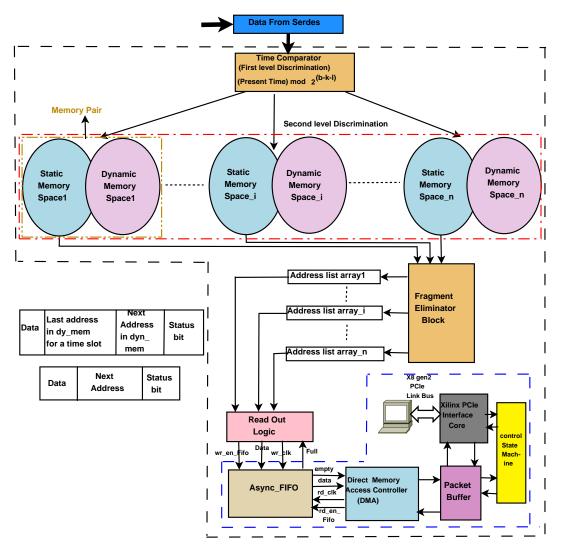

| 1 11 | Implementation of memory management module with PCIe interface         |                  |

|      | <del>-</del>                                                           | $\frac{30}{101}$ |

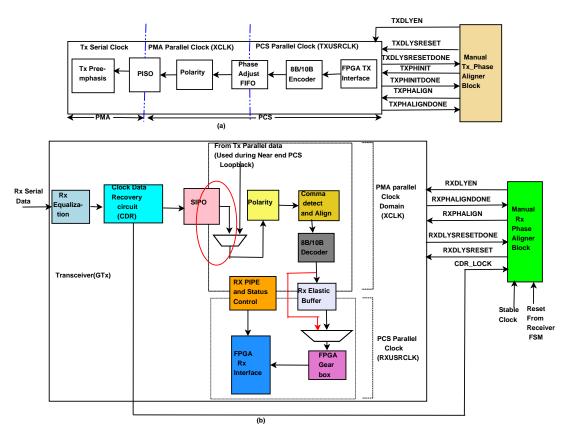

|      | (a) Different clock domains in the transmitter (b) Different clock     | 101              |

| 4.10 |                                                                        | 103              |

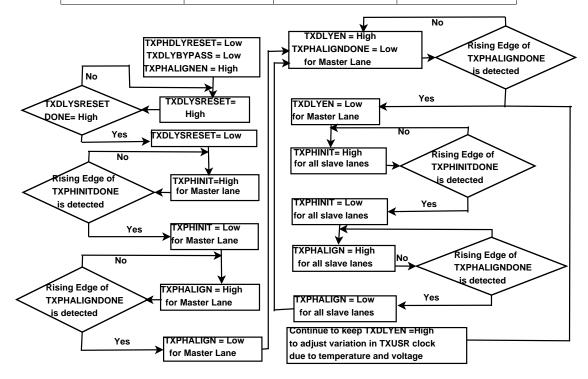

| 1 17 | Flow diagram for manual phase alignment in the transmitter after       | 100              |

| 4.17 |                                                                        | 104              |

| 1 10 |                                                                        | 104 $106$        |

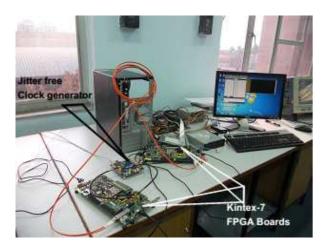

|      |                                                                        | $100 \\ 106$     |

|      |                                                                        | 100              |

| 4.20 | System for testing the proposed DAQ system using KC705 and             | 107              |

| 4 01 |                                                                        | 107              |

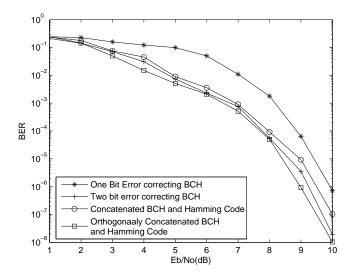

| 4.21 | Comparison of BER performance of different coding schemes with         | 105              |

| 4.00 |                                                                        | 107              |

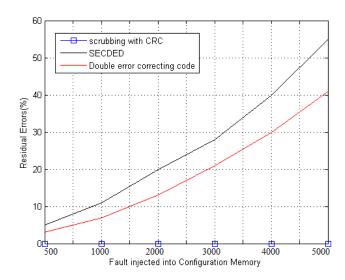

|      | ·                                                                      | 108              |

| 4.23 | Presence of residual error after error correction with different error |                  |

|      |                                                                        | 109              |

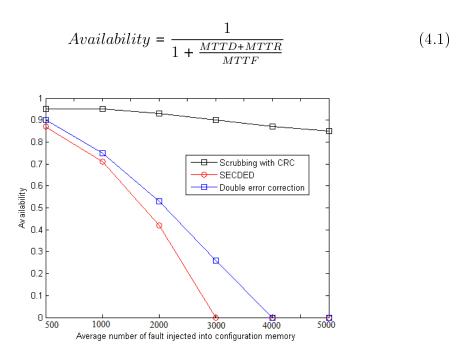

| 4.24 | Comparison of availability of FPGA devices after error correction      |                  |

|      | using different error correcting schemes and Scrubbing with CRC        | 110              |

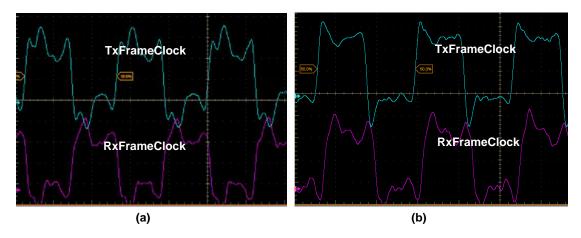

| 4.25 | (a) TxFRameClock and RxFrameClock before latency optimiza-          |     |

|------|---------------------------------------------------------------------|-----|

|      | tion (b) TxFRameClock and RxFrameClock after latency opti-          |     |

|      | mization                                                            | 111 |

| 4.26 | Simulation result for memory management module                      | 112 |

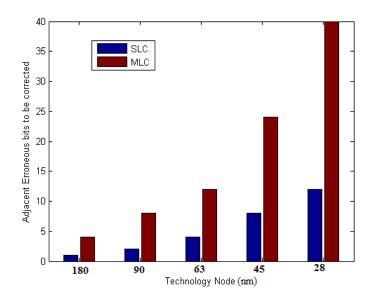

| 5.1  | Number of adjacent erroneous bits for MLC and SLC with different $$ |     |

|      | technology node [138]                                               | 116 |

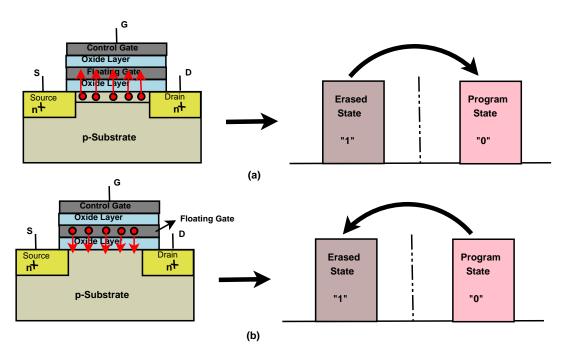

| 5.2  | Programming and Erasing a Floating Gate Transistor                  | 118 |

| 5.3  | Threshold voltage distribution of SLC, MLC with two and three       |     |

|      | bits per cell                                                       | 119 |

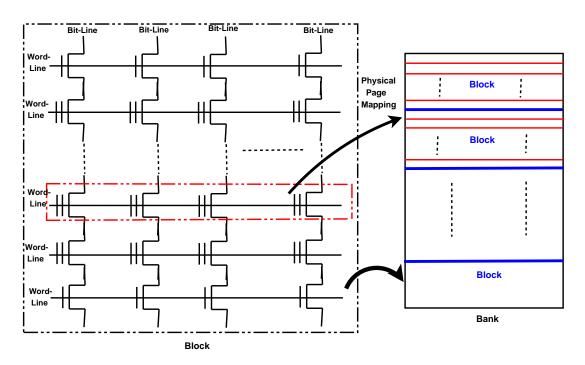

| 5.4  | Organization of Bank, Block and pages in the MLC flash memory       | 120 |

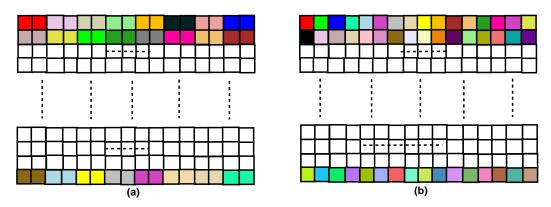

| 5.5  | (a) Single page programming based MLC (b) Multi-page program-       |     |

|      | ming based MLC                                                      | 121 |

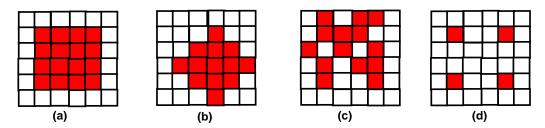

| 5.6  | Different cluster and almost cluster patterns                       | 122 |

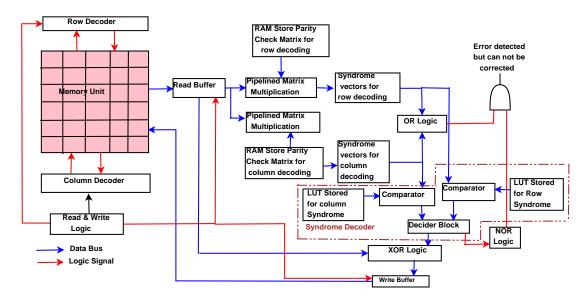

| 5.7  | Hardware Implementation of proposed LSBCPC                          | 132 |

| 5.8  | Timing Diagram for pipelined architecture of matrix multiplication  |     |

|      | during syndrome generation                                          | 136 |

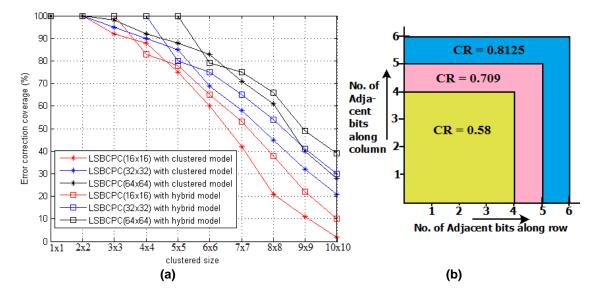

| 5.9  | Error correction coverage of LSBCPC of different sizes (a) for both |     |

|      | adjacent as well as nonadjacent MBUs (b) only for adjacent MBU      | 137 |

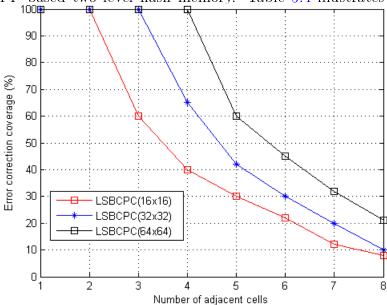

| 5.10 | Adjacent cell correction coverage for single page programming based |     |

|      | two level flash memory using LSBCPC having different sizes          | 138 |

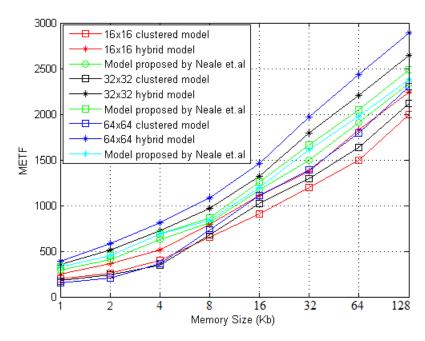

| 5.11 | Variation of METF with different memory sizes                       | 141 |

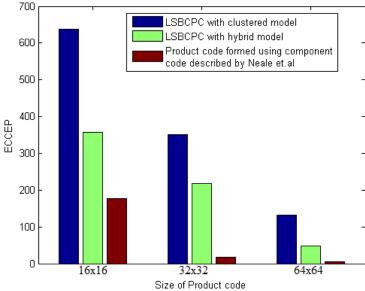

| 5.12 | Variation of ECCEP for different size of LSBCPC and product         |     |

|      | code formed using component code described in [148]                 | 143 |

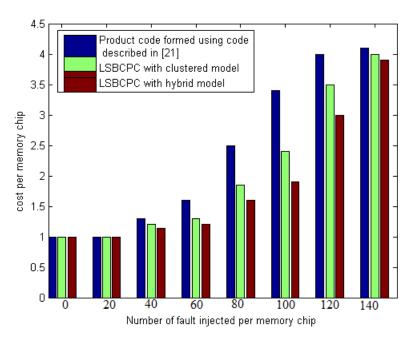

| 5.13 | Variation of Cost per chip with different number of errors injected |     |

|      | per memory chip for LSBCPC and product code developed using         |     |

|      | block code described in [148] having size $32\times32$              | 144 |

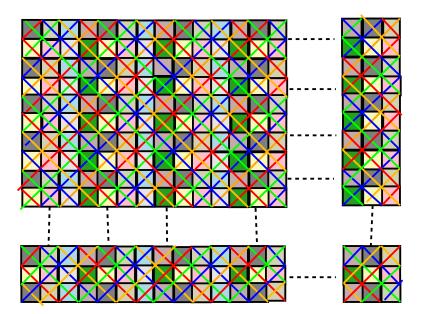

| 6.1  | Frame Interleaving in the configuration memory of FPGA              | 149 |

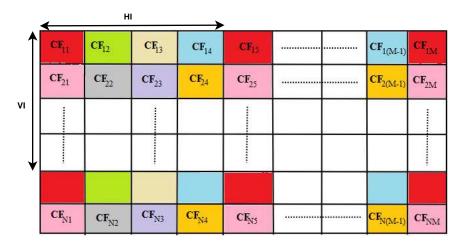

| 6.2  | Configuration Frames of an interleaving group arranged into mul-    |     |

|      | tiple horizontal and vertical groups                                | 150 |

| 6.3  | Arrangement of data and parity bit for (12,8) Hamming coded data    | 152 |

| 6.4  | Arrangement of data and parity bits in a data matrix of size 12×12  |     |

|      | before selective bit placement                                      | 154 |

| 6.5  | Arrangement of data and parity bits in a data matrix of size $12 \times 12$ |

|------|-----------------------------------------------------------------------------|

|      | after selective bit placement                                               |

| 6.6  | Arrangement of data and parity bits in a data matrix of size 13×13          |

|      | after selective bit placement                                               |

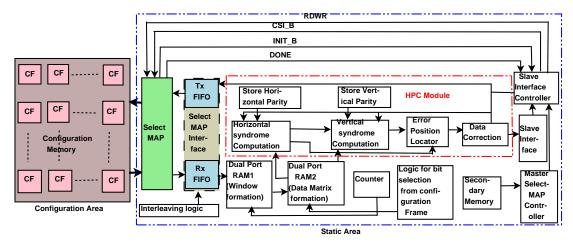

| 6.7  | Hardware implementation of HPCFISBP                                         |

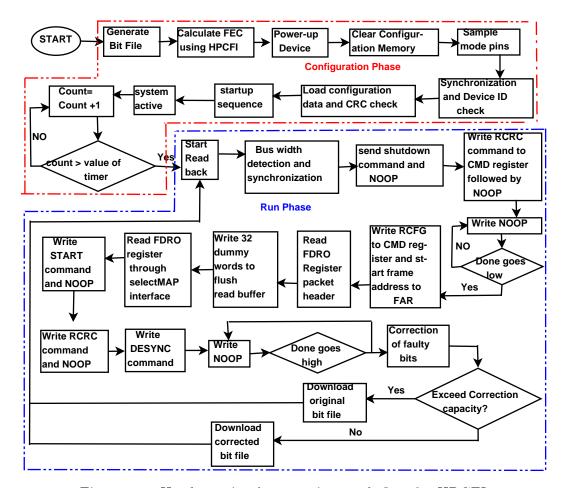

| 6.8  | Hardware implementation work-flow for HPCFI                                 |

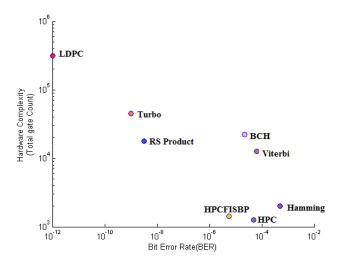

| 6.9  | Hardware Complexity vs BER for different ECC                                |

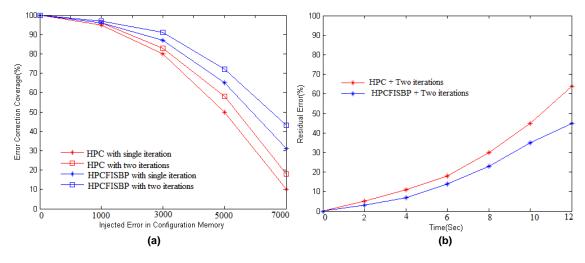

| 6.10 | (a) Comparison of error correction coverage of HPCFISBP with                |

|      | HPC proposed by authors in [89] (b) Residual errors in configu-             |

|      | ration memory at different time instance after error correction by          |

|      | HPC and HPCFISBP                                                            |

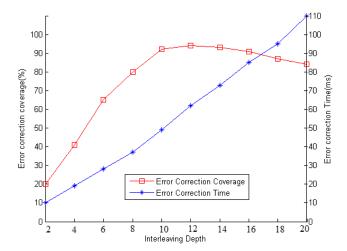

| 6.11 | Variation of error correction coverage and error correction time            |

|      | with different interleaving depth                                           |

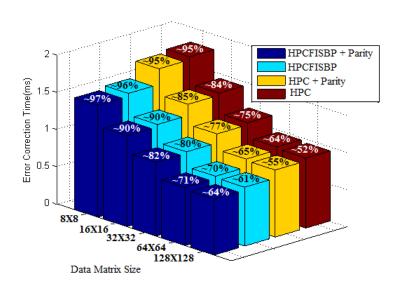

| 6.12 | Variation of error correction time and error correction capability          |

|      | with size of data matrix                                                    |

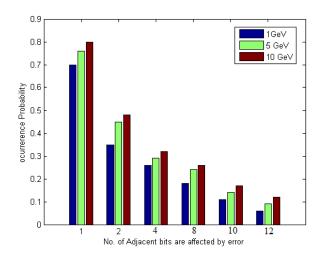

| 7.1  | Occurrence probability of different MBU and SBU (indicated by               |

|      | '1' along x-axis) patterns for different Neutron energy 171                 |

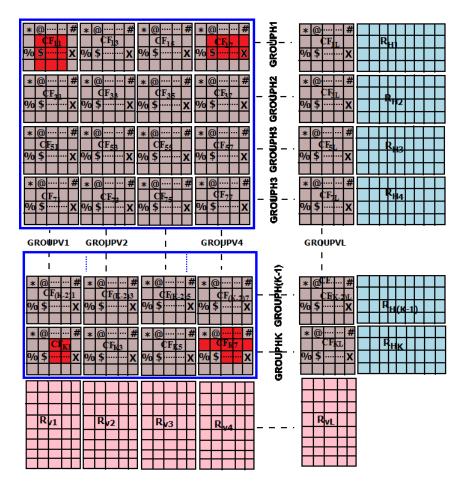

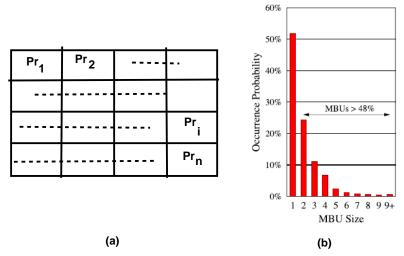

| 7.2  | (a) Partitioned of configuration memory into n number of regions            |

|      | (b) MBU distribution in 45 nm SRAM based FPGA (Taken from [97]172           |

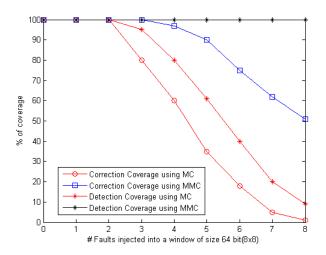

| 7.3  | Detection and correction coverage of MMC and MC over $64$ bit data $174$    |

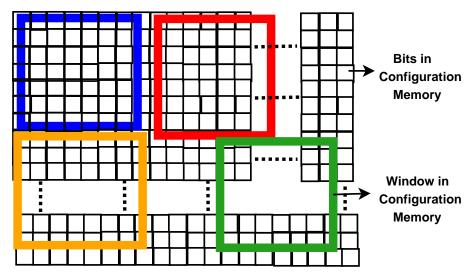

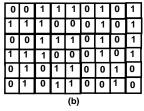

| 7.4  | Window formation within a configuration frame                               |

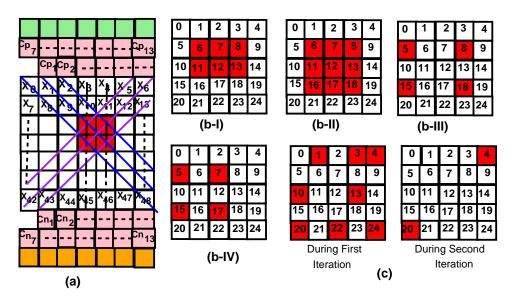

| 7.5  | (a)Encoding/Decoding using 7×7 window (b)Different error pat-               |

|      | terns (c) Error Correction using Multiple Iterations                        |

| 7.6  | Working Methodology of the proposed MMC code                                |

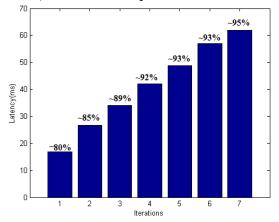

| 7.7  | Variation of correction coverage of MMC and latency with iteration $177$    |

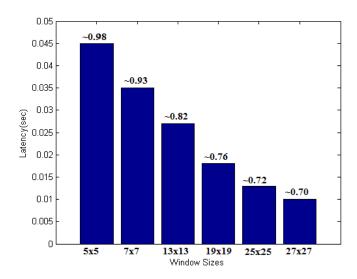

| 7.8  | Variation of error correcting capability of MMC and latency with            |

|      | $ different \ window \ sizes \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $        |

| 7.9  | Detection using Interleaved MMC                                             |

| 7.10 | Example of EVENODD encoding taking $R = 7 \dots 184$                        |

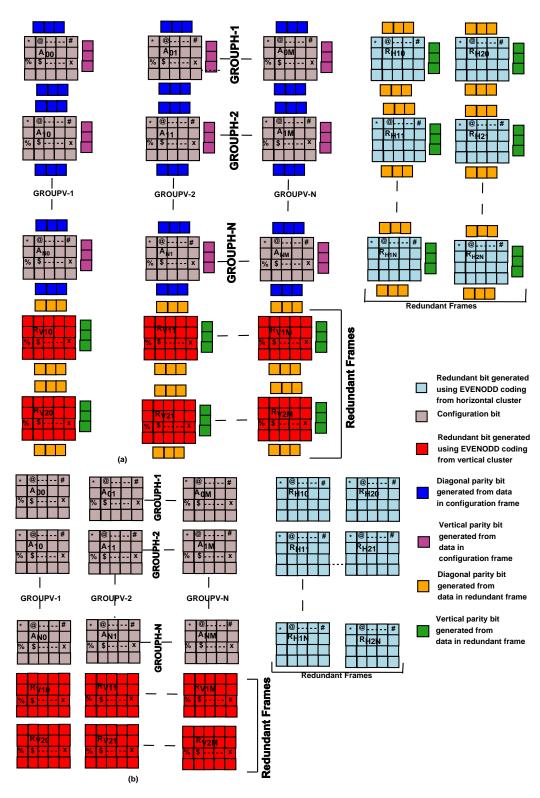

| 7.11 | Grouping of configuration frames for decoding using EVENODD                 |

|      | code: (a) when EDAC is done separately(b) when EDAC is done                 |

|      | simultaneously                                                              |

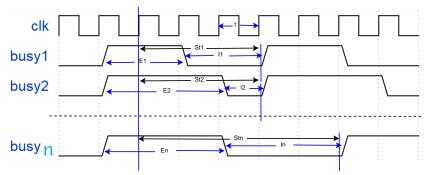

| 7.12 | Timing diagram of $St_i$                                             | 195 |

|------|----------------------------------------------------------------------|-----|

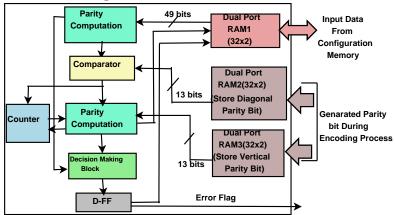

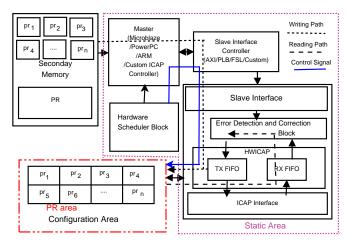

| 7.13 | Hardware implementation of the proposed Models                       | 196 |

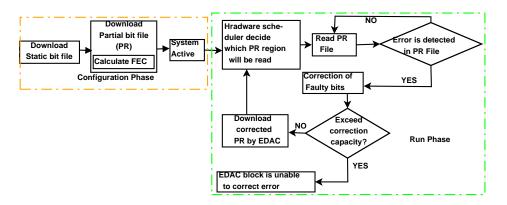

| 7.14 | Workflow of the proposed error correcting models                     | 197 |

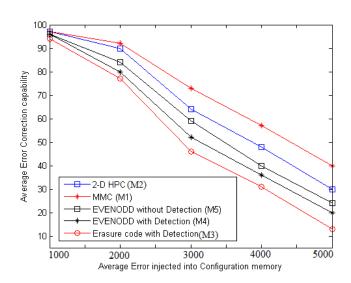

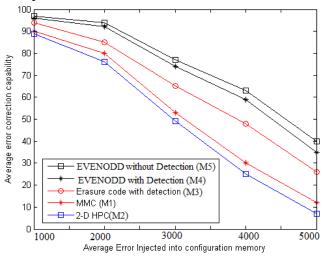

| 7.15 | Average error correction capability of different error correcting    |     |

|      | models when single or small number of adjacent bits are affected     |     |

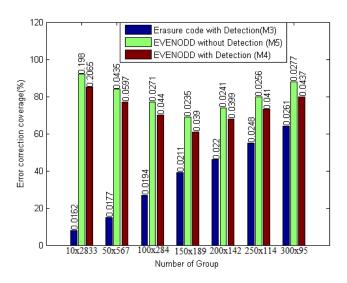

|      | by random error                                                      | 198 |

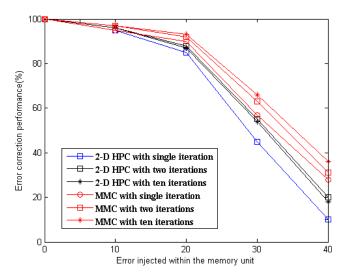

| 7.16 | Comparison of error correction capability between MMC and HPC        | 200 |

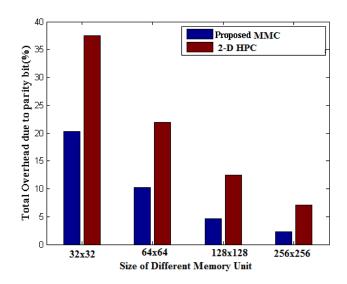

| 7.17 | Comparison between HPC and MMC due to redundant bits $\dots$ .       | 201 |

| 7.18 | Average error correction capability of different error correcting    |     |

|      | models for clustered error                                           | 201 |

| 7.19 | Comparison between our proposed EVENODD model and model              |     |

|      | proposed in [97] for different size of group                         | 203 |

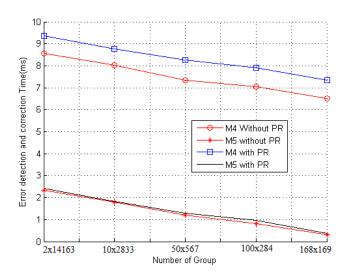

| 7.20 | Comparison of fault recovery time with different group sizes for er- |     |

|      | ror detection with EVENODD and single error correcting EVEN-         |     |

|      | ODD                                                                  | 206 |

# List of Tables

| 1.1 | Function of detectors used in CBM Experiment [12]                       |

|-----|-------------------------------------------------------------------------|

| 3.1 | MUCH-XYTER Analog Front-end Register Description                        |

| 3.2 | MUCH-XYTER Digital Back-end Register Description for $192^{th}$ row 54  |

| 3.3 | Gain of slow and fast shaper for different feedback capacitance of      |

|     | CSA                                                                     |

| 3.4 | Resource Utilization for different module of IPBus on FPGA 73           |

| 3.5 | Description of the signals used in timing diagram                       |

| 3.6 | Resource Utilization and Power consumption by integrated design 76      |

| 4.1 | Function of different fields in data packet used for PCIe communi-      |

|     | cation                                                                  |

| 4.2 | Parameters of the MGT to be set during latency optimization $$ . $$ 104 |

| 4.3 | Details of the signals used during latency optimization 104             |

| 4.4 | Resource Utilization                                                    |

| 4.5 | Summery of different features of our proposed DAQ system and            |

|     | different state of the art solutions                                    |

| 5.1 | Generated syndromes for different adjacent erroneous bits 128           |

| 5.2 | Generated syndromes for different error patterns                        |

| 5.3 | Generated syndromes for different error patterns                        |

| 5.4 | Comparison of the proposed codes with other codes                       |

| 5.5 | MTTF in Days for different memory sizes                                 |

| 6.1 | Bit placement strategy in an one dimensional memory array 152           |

| 6.2 | Variation of error correction coverage with interleaving depth $166$    |

### LIST OF TABLES

| 6.3 | Comparison between Proposed ECC with the other existing ECC            | 167 |

|-----|------------------------------------------------------------------------|-----|

| 7.1 | Summary of error detecting and correcting codes used in this paper     | 192 |

| 7.2 | Detection capability of IMMC with different interleaving depth . $\ .$ | 202 |

| 7.3 | Power Consumption by different models                                  | 203 |

| 7.4 | Fault recovery time for different models                               | 204 |

# Chapter 1

# Introduction

To solve the long standing puzzles of the universe that haunt the mankind for thousand of years, scientists have been trying to widen their knowledge specifically in two extreme directions: macroscopic and microscopic. For the macroscopic physics, scientists have developed huge telescopes like hubble telescope, ARIES Telescope to take the image of the universe, supernova and galaxies. They have also prepared spacecrafts like Juno [1] (developed by NASA) to gather information about jupiter, Mangalyaan [2] (developed by Indian Space Research Organization) to study the atmosphere of the Mars. At the same time, to study the matter at the subatomic level, scientists have developed high energy accelerators like Large Hadron Collider (LHC [3]), Standford Linear Collider (SLC [4]), Universal Linear Accelerator (UNILAC) [5]. One of the major objectives of the ongoing accelerator based experiments is to create initial state of the Bing-Bang or a matter limited to the inner region of the dense neutron star in the laboratory. Apart from the study of matter at the subatomic level, accelerators are now a days being used in other domains like structural biology, radio therapy etc. Though the microscopic and the macroscopic approaches are totally different, they are interrelated and influence each other. Giant machines, robust high speed data transmission networks and complex signal processing algorithms are integral parts in both of the approaches. Different modern electronics devices like FPGA, ASICs, Microcontrollers are used to develop such giant machines that help to implement complex data processing algorithms. This thesis work has been mainly carried out in the context of development of the readout system of one such experiment, the Compressed Baryonic Matter experiment at the FAIR [6] complex in GSI, Germany.

### 1.1 Compressed Baryonic Matter Experiment

FAIR in GSI provides unique research opportunities in the fields of nuclear, hadron, atomic, plasma physics and computational biology etc. There are mainly four researches are going on in the FAIR complex [6]: Atomic, Plasma Physics and Applications (APPA), Compressed Baryonic Matter (CBM), Nuclear Structure, Astrophysics and Reactions (NUSTAR) and Anti-proton Annihilation at Darmstadt (PANDA). The CBM experiment [7] which is under development at the FAIR complex is one of the major fixed target experiments, and the objective of this experiment is the exploration of quantum chromodynamics (QCD), the theory of strongly interacting matter at moderate temperatures and high baryon (Baryon is a subatomic particle made up of three quarks) density [8]. Phase diagram depicts the existence of different states of the matter (like solid, liquid and gas) at different external thermodynamic conditions like temperature and pressure. From the particle physics we know that quark is the fundamental particle that form neutron and proton within the atom. Gluon helps to bind the quarks within the neutron and proton. At a normal temperature and pressure these quarks and gluons can not be separated. At extreme external conditions (like at high temperature or at high net baryon density) these quarks and gluons can be separated and they exist in a plasma like state which is known as quark gluon plasma (QGP) [9]. This state was said to be present at the time of Bing-Bang [10] or at the initial stage of the universe. In order to create high baryon density and high temperature in the laboratory, heavy ions with high ionizing energy are collided in an accelerator that provide different subatomic particles. Different detector systems are placed around the point of collision to detect the generated subatomic particles that helps in the study of the QCD phase diagram.

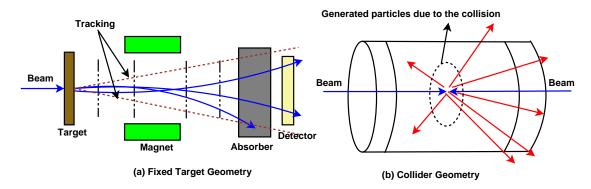

Based on the arrangement of the collision within the accelerator there are two types of experiments: fixed target experiment and collider experiment. In the fixed target experiment, heavy ion beam within the accelerator hits a stationary target as shown in Figure 1.1(a). Such stationary target may be a chunk of

metal or liquid hydrogen in a large container. Number of collisions in the fixed target experiment can be increased by increasing the thickness of the target. Placement of detector system is quite easier in such experiment. On the other hand in collider type experiment two beams are directed to each other and made to collide within the accelerator like in LHC [11] at CERN. As the beams are very narrow they need very precise control and steering mechanism to guarantee that two beams rotating in opposite directions will collide with each other as shown in Figure 1.1(b). Though placement of detector around the point of collision is complicated in collider type experiment it provides high energy at the point of collision. As CBM studies the QCD phase diagram at high baryon density at low temperature it uses fixed target experiment where a range of target and beam are used in the range of proton to uranium. CBM experiment aims to find the phase

Figure 1.1: Fixed Target Experiment vs Collider Experiment

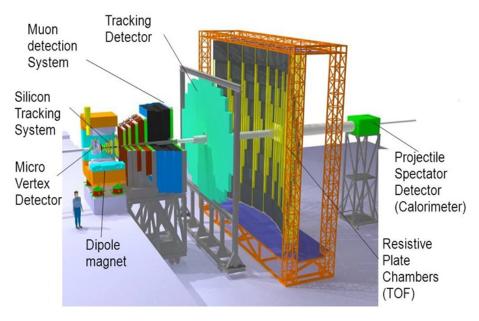

transition in QCD experimentally where QGP exists. The main challenges of the CBM experiment is to measure these particles with high precision and statistics. Hence, different detector subsystems are required to identify the particles (like muon, mesons, electrons and photon etc.) generated in the CBM experiment. Arrangement of different detector systems that will be used in CBM experiment are shown in Figure 1.2 and functionalities of each detector subsystem is described in Table 1.1. The detectors will send the readout informations to the computer cluster. Hence, a robust readout system is very much necessary for each detector system. In this thesis, we have mainly focused on the development of readout chain of MUCH detector.

Figure 1.2: Detector system in CBM experiment [12]

Table 1.1: Function of detectors used in CBM Experiment [12]

| Name of the Detector | Functionalities                                 |

|----------------------|-------------------------------------------------|

| Silicon Tracking     | Used for track reconstruction and determination |

| System(STS)          | of momentum of charged particles                |

| Ring Imaging Chere-  | Identification and suppression of pions         |

| nkov Detector (RICH) | with the momentum below 10 ${ m GeV}/c$         |

| Muon Chamber         | Detect muons generated from $J/\Psi$ particle   |

| System (MUCH)        | and light vector mesons                         |

| Transition Radiation | Used to identify electrons and pions            |

| Detector (TRD)       |                                                 |

| Time of Flight       | Used to identify hadron through time of         |

| (TOF)                | flight measurement                              |

| Calorimeter          | Measure photon and neutral mesons               |

### 1.1.1 Muon Chamber (MUCH) Detector

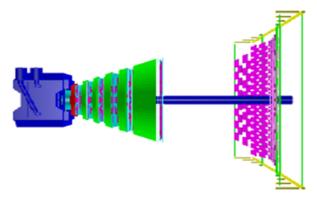

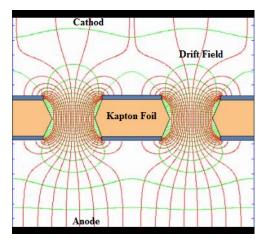

MUCH in CBM experiment is mainly used to detect dimuons generated from charmonia (bound state of charms and anti-charms quarks) and light vector mesons [13] which are very rare particles generated during the collision. MUCH consists of segmented absorber layer (indicated by green color in Figure 1.3) made of iron or carbon and gas electron multiplier (GEM [14]) based detectors are placed in between two segments as shown in Figure 1.3. Each GEM detector consists of 50  $\mu$ m thin copper claded kapton foil having 50-70  $\mu$ m hole diameters

Figure 1.3: Schematic view of MUCH detector with segmented absorber [13]

at a pitch of 140  $\mu$ m and two copper plates that act like cathode and anode. During the operation, 300-400 volt is applied across the surface of the foils that creates a high electric field inside the holes. The detector volume is filled with mixture of Argon and Carbon-di-oxide and when particles pass through the high field region inside the holes it ionizes the gas molecules and generates primary electrons. These primary electrons are accelerated through drift field and create more electrons through avalanche multiplications. In this way generated electron cloud is collected on the anode plane and produce the output signal. The gain of the GEM detector can be increased by adding multiple foils in between cathode and anode which is known as multi-layer GEM. Figure 1.4 shows architecture of single layer GEM detector. MUCH detectors will be placed in the downstream

Figure 1.4: Basic structure of single layer GEM detector

of silicon tracking system (STS) [15] detector that measure momentum of the particles.

### 1.2 Architecture of Data Acquisition System

In order to obtain reasonable statistics for rare particles like  $J/\psi$  over a reasonable running period the interaction rate of colliding ions should be very high and for CBM experiment it will reach up to  $10^7$  events/second [16]. For handling such high reaction rate, CBM in general and MUCH detector in particulars uses a novel approach of data acquisition. MUCH detector in CBM experiment capture data using free running and self-triggered [17] (discussed later) FEBs. On the other hand in traditional accelerator based high energy physics (HEP) experiment, DAQ organizes the data read-out based on hierarchical trigger decisions. Different features [18] of the DAQ system used for MUCH detector are:

- Precise time synchronization.

- Fault resiliency.

- Ability to support high data rate and efficient data aggregation schemes.

- Self-triggered high-speed front-end electronics (FEEs) and compact hardware due to limited space.

- Ability to implement complex data processing algorithm.

In general, DAQ system (shown in Figure 1.5) consists of FEEs, data aggregation and control unit (DACU), a hierarchical DAQ networks and back-end computing cluster nodes. FEEs are responsible for acquisition of analog signal from detector

Figure 1.5: Traditional DAQ network architecture [18]

system and conversion of received analog signal to digital signal. DACU helps

Figure 1.6: Planned Building and Cave Infrastructure for CBM Experiment [12]

in control and data synchronization. Hierarchical DAQ network connects the FEEs to the backend computing nodes where different reconstruction and decision making algorithms are used to analyze the received data by the detector system. In case of DAQ system for MUCH detector FEE, DACU and hierarchical DAQ network are under harsh radiation (*i.e* within the detector cave), and remaining portion of the DAQ chain is in the moderate radiation zone as shown in Figure 1.6.

### 1.2.1 Errors in DAQ system and its mitigation

Electronic devices used in the design of hardware systems for the data transmission network and data processing algorithm for such HEP experiment are often affected by radiation and channel noises, that may lead to errors in the system's outcome. Errors may occur in (i) communication link (ii) internal processing blocks and (iii) memory unit. Here, we have considered the errors occur in all three places. Most of the modern embedded electronic devices are developed using silicon wafers which are vulnerable to radiation. Faults occurred due to radiation in such solid state devices can be categorized into two broad domains: Temporary fault and permanent fault. Temporary faults lead to temporary malfunctions that occur in solid state devices and their effect is termed as soft errors.

Soft errors occur due to ionization of charged particles and may create latch-up and transient fault. X-ray radiation, photocurrent caused by ultraviolet and other low energy gamma ray are responsible for soft errors. Soft errors are not reproducible and sometimes lead to single bit upsets (SBU) and multiple bit upsets (MBU) in different embedded devices. Effect of soft errors into any logic will be transferred to the output of flip-flop or memory if its period of occurrence is higher than the period of the clock which drives the circuit. Permanent faults in solid state devices occur due to lattice dislocation by protons,  $\alpha$  particles, heavy ions and high energy gamma rays. This permanently change the arrangement of atoms within the crystal lattice and leads to single event induced burnout and rupturing of gate of the MOSFET. Sometimes higher ionization dose for short time may partially anneal the damage due to lattice dislocation that may reduce the degree of damage. The permanent faults are of two types: one is permanent recoverable fault and other one is permanent nonrecoverable fault [19]. When incident charge particles permanently damage the logic blocks within the embedded devices, nonrecoverable faults occur and it can only be sorted out by replacing the defective logic blocks physically. Permanent recoverable can be mitigated either using built in error detection and correction (EDAC) code or by rewriting the memory of embedded devices and power on reset.

Methods to protect solid state devices from the effect of radiation can be broadly classified into categories: Physical and logical. Physical methods include:

- Use of different insulating substrate instead of traditional silicon wafer. Generally, silicon on insulator (SOI) or sapphire are used in these cases.

- Use Bipolar junction transistor or emitter couple logic based transistor instead of CMOS based transistor.

- Proper radio active shielding can be used to protect solid state devices from the effect of radiation.

- Magnetoresistive RAM (MRAM) and capacitor based DRAM are more robust compared to static RAM in the radiation zone.

- Use of wide band gap material like silicon carbide or gallium nitride as substrate make the device more robust in radiation environment.

On the other hand logical method includes majority voting, parity based error correcting methods, redundant logic, use of watchdog timer etc. Here we have mainly focused on logical methods using multi-bit ECCs to mitigate the error in the solid state devices occurred due to radiation because other logical methods either consume large memory or have higher latency. This issues justify the need of different low complexity EDAC algorithms to be incorporated within the electronics devices to minimize the errors causing due to SBUs and MBUs in the system. Designing of efficient error correction schemes in the hardware without hampering normal system operation should also consider the trade off between correction coverage and resource utilization. Attaining higher code coverage with low resource requirement is one of the key research issues in error correction mechanism.

As a choice of target platform, the embedded designers have three choices namely, (i) standard micro-controller or microprocessor platform (ii) custom hardware platform based ASICs and (iii) custom as well as re-configurable hardware platform based on FPGAs.

### 1.2.2 Microprocessor and Micro-controller

Micro-controller is mostly used for embedded system designer due to its flexibility, cost effectiveness and availability. Micro-controllers are single chip microcomputers, that includes processing unit, memory and I/O elements in the same chip. Though micro-controller based system provides easy solution they are normally used for specific application as they have limited resources and are driven by software instructions. Their performance is limited by the fact that they only provide generic processing core, which cannot satisfy the need of higher performance as compared to custom application specific cores. Some of the well known micro-controller platforms for embedded applications are 8051, Atmega etc. In CBM experiment, micro-controllers are used for detector control system, low voltage power distribution etc.

### 1.2.3 Application Specific Integrated Circuits

ASICs are mainly designed for particular application instead of general purpose usage. Designs implemented on ASICs cannot be changed once the chip is fabricated or manufactured. In the modern embedded application continuous upgradation is needed to cope up with the advancement of technology. In such case ASIC is not good solution. Moreover, with the inclusion of partial programming capabilities in modern programmable logic devices, the downtime of the system is further reduced as the hardware upgradation in the partially reconfigured region can work concurrently while, the other regions are on execution. Though the circuit implementation can be highly optimized in terms of speed, area and power consumption, inability to adapt design changes after manufacturing is a serious disadvantage for ASICs. Modern ASIC fabrication processes are also costly, time consuming and hence, they are used only for some critical applications like high speed signal processing in satellite, mobile devices, televisions etc.

### 1.2.4 Field Programmable Gate Array (FPGAs)

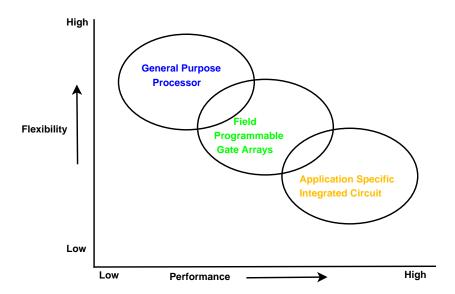

Hardware design is flexible using general purpose processors that means user can modify the design as per need by using high level programming languages without modifying the underlying processor architecture. General purpose processor does not bother about structure of the algorithm instead their focus is to support the processing need of a large variety of algorithms. Hence, in general, execution time and power consumption for a algorithm is high on general purpose processor. On the other hand ASICs provide less processing time and power consumption for an algorithm but flexibility is less. Reconfigurable devices like programmable logic array (PLA), programmable array logic (PAL), complex programmable logic devices (CPLD) and FPGA fills this gap and in an ideal case, combines the best of both; namely, the speed of ASICs to the flexibility of general purpose processors. Figure 1.7 provides trade-off between performance and flexibility for general purpose processor, ASICs and FPGA. Though there are different reconfigurable devices available in the market we are mainly focused on FPGA in this thesis. Xilinx, Altera, Actel are the leading vendors that manufacture FPGA. Main units inside the FPGA are reconfigurable functional units, programmable

Figure 1.7: Performance-flexibility graph among ASIC, FPGA and general purpose processor

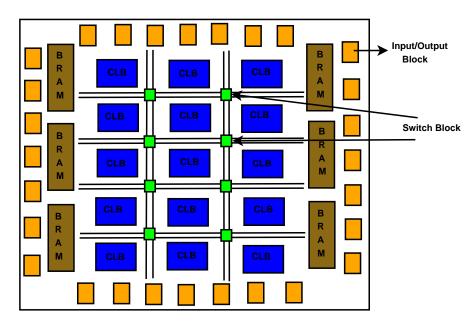

Figure 1.8: A Generic FPGA internal Architecture

switch matrix and I/O interfaces as shown in Figure 1.8.

During implementation of any logic in the FPGA, reconfigurable functional units or fabrics are used and hardware blocks are interconnected by the programmable switch matrices. Performance of the implemented logic on FPGA depends on the flexibility and efficiency of the reconfigurable fabrics. On the

other hand reconfigurability of FPGA devices are fully depends on size of the reconfigurable functional units or granularity. Based on the size of granularity FPGA devices can be classified into two broad categories [20]: fine-grained and coarse-grained. Look up tables (LUTs) are basic functional unit of fine-grained architecture and it is typically used to implement single function on small number of bits. On the other hand Arithmetic logic unit (ALU) is the basic unit of coarse grained architecture and hence, complex and large function can be implemented using this architecture. In general, modern FPGA like seven series FPGA of Xilinx, Arria and Stratix series FPGA of Altera follows fine grained architecture where reconfigurable functional units consist of 6-to-1-bit LUTs which are arranged in clusters. A collection of LUTs, storage element and multiplexers form configuration logic block (CLB). CLB of Xilinx Kintex-7 FPGA consists of two slices [21]: SLICEL and SLICEM. SLICEL is only used for logic operation. Along with logic operation SLICEM is also responsible for storing data using distributed RAM and shifting data with 32-bit registers. Each slice consists of four six input LUTs, eight flip-flops, multiplexers and arithmetic carry logic. The number of LUTs and flip-flops within the CLB varies depending on the different FPGA vendors. Modern FPGAs are integrated with hard processor core like PowerPC in Virtex, ARM in Zyng etc and soft core like Microblaze, NIOS which can be used for any processor based complex embedded design using FPGAs. Configuration data also known as bit file programmed CLB and programmable switching blocks in the configuration memory during reconfiguration of the FPGA devices. Based on the nature of configuration memory FPGAs can be classified into three categories. If configuration data is stored in SRAM within FPGA then it is known as SRAM-based FPGA and if configuration data is stored in Flash memory then FPGA devices are known as Flash-based FPGA. Antifuse-based FPGAs are slightly different from the other two in the sense that they can be programmed only once. Antifuse element does not conduct initially but during programming the antifuse switches are burned out that cannot be returned into the initial state. Maximum modern FPGAs are either flash based or SRAM based.

Now a days FPGAs are widely used in different embedded applications due to their multiple advantages briefed as follows:

- FPGA can be used as co-processor of the CPU in the modern computer or as an accelerator using high speed bus, like PCIe.

- FPGAs are interconnected with high speed peripherals like USB, optical transceiver, Ethernet, PCIe for data transfer with external devices.

- FPGA supports partial reconfiguration that helps to replace a module of the design without hampering the functionalities of other modules.

- Memory access time inside FPGA devices are very less.

- FPGA also supports remote reconfiguration.

FPGAs are commonly used to achieve high performance computation as they offer spatial parallelism involving the configurable blocks.

#### 1.2.5 FPGA Design Flow

The design flow starts with the design specifications given by the user and finishes into a working design in an FPGA. The design flow for a FPGA based system is shown in Figure 1.9. Initial stage involves problem decomposition, project requirement and functional simulation. In the next stage for design entry there are different techniques like hardware description language (HDL), schematic and combination of both. During the logic synthesis HDL codes are mapped into gate level net-list and the net-list is stored as Native Generic Circuit (NGC) file. The implementation process involves three steps: Translation, mapping, placement and routing (PAR). In the translation, all the input net-lists combine with the constraints to form a logic design file and the static data into Native Generic Database (NGD) file. Mapping process divides the whole design into multiple sub-blocks and try to fit into the target FPGA devices to generate the Native Circuit Description (NCD) file. PAR maps the sub-blocks into logical blocks according to the constraints provided by the user and creates the interconnection of the logical blocks utilizing the FPGA fabric. Static timing analysis after MAP or PAR helps to find the path delay and timing violation for the design derived from the design logic. Automatic mapping can also be done by some tools like automatic HDL generators [22]. Lastly, using the programming file (bit file or

Figure 1.9: HDL based design flow for FPGA based system design

configuration data) the FPGA is configured or programmed. Design softwares offered by the FPGA vendors support the complete design flow.

Embedded systems based on FPGA devices are vulnerable to external noise (specifically created by radiation) since physical access to these devices can be done at an ease. In many of the cases the faults are caused unintentionally due to the natural effects e.g radiation, cosmic ray. Detecting the errors occurring due to these faults and also correcting them in the hardware will make the system more trustworthy. In CBM experiment, radiation level is so high within the cave that the commercial-of-the-self (COTS) FPGAs cannot be used. One of the common solution to prevent FPGA devices from the effect of radiation is to use radiation hardened (Radhard) FPGAs like space-grade FPGAs provided by Xilinx [23], Altera or Microsemi [24] but they are more costly compared to the COTS FPGAs [25] and are also few generation behind than COTS FPGAs. Hence, usage of SRAM-based COTS FPGA is only possible in such radiation environment with appropriate error mitigation techniques. Though ASICs are not very flexible and require more developmental effort, it is much less susceptible to ionizing radiation than COTS FPGA [26]. In some areas within the CBM cave (like near the detector system) use of ASICs are better option compared to FPGAs as ASICs are more radiation tolerant compared to FPGAs. There are some other areas with (comparably) modest radiation levels like in CBMBunker [7] as shown in Figure 1.6 where FPGAs might be the better option to use. Radiationinduced charge particles like alpha, beta can either corrupt user data in the communication link which connects different electronics devices in the readout chain or can directly damage the FPGA devices itself. Radiation corrupts either single bit or multiple bit in user data stored in the RAM or configuration data in configuration memory of FPGA devices. In this thesis error mitigation techniques have been developed for safe guarding the configuration data of FPGA devices in configuration memory as well as user data in communication links.

### 1.3 Research Motivation

- Design and development of high speed DAQ system is very much needed that can work without human interference in the accelerator under harsh radiation environment. Hence, there should some methods for monitoring the status of the DAQ system.

- Radiated charge particles may corrupt the data packets during the transmission through high speed interconnect within the DAQ system. Hence, multi-bit error correcting codes are needed to correct the corrupted data in high speed interconnection like optical fiber. Apart from the error in the data stream indeterministic latency added by different memory elements is a critical issue for any high speed data communication. It is very much needed to fix the latency in the high speed communication by bypassing internal memory elements for clock domain crossing and phase alignment.

- Solid state devices like FPGA used for implementation of data processing algorithm may also be affected by radiated charge particles generated during different experiment or cosmic ray during space exploration. In order to mitigate the soft errors arise due to SBUs and MBUs from radiated charge particles efficient error correcting codes with less overhead and simple decoding circuits are needed.

- With the increase of density of CMOS transistors in memory element like flash memory probability of corruption in stored data also increases. When the MBUs are adjacent to each other they form an error cluster and sometimes traditional multi-bit error correcting codes are not efficient against

- clustered error. Hence, simple clustered error correction methods with small error correction time is very much needed for high density memory elements.

- To maintain the uninterrupted operation of a real time system there should some provisions for repairing a functional module without hampering functionalities of other modules.

## 1.4 Research Objective

The main research objectives of this thesis are:

- Testing and characterization of front-end ASICs that will be used to readout the data from MUCH detector and integration of front-end ASICs with the remaining portion of readout chain.

- FPGA implementation of IPBus protocol over one Gigabit Ethernet for remote monitoring of different registers of the DAQ system.

- Development of high speed DAQ systems having error resilient latency optimized communication link and direct memory access controller with PCIe interface. An efficient memory management algorithm is also proposed for data aggregation before data transmission through PCIe.

- Hardware implementation of clustered error or error arises due to adjacent MBUs correction techniques for high density memory element like MLC flash memories are discussed. The proposed methods have less error correction time, low decoding complexity and low overhead compared to the state of the art solutions.

- Development of different SBUs and MBUs mitigation techniques for the configuration memory of FPGAs and their efficient hardware implementation.

- Dynamic partial reconfiguration with proper hardware scheduling algorithm is developed for error correction in a module within a FPGA devices with minimal interface to the normal system operations.

### 1.5 Organization of the Thesis

In this thesis, our contributions target some specific design and implementation issues to overcome some of the challenges existing in the present state-of-the-art embedded system under radiation environment. Related research work and motivations of the thesis is described in Chapter 2. Chapter 3 deals with testing and characterization of front end ASICs and its integration with FPGA based GBTx emulator and data processing board using differential electrical line and optical fiber. Development of FPGA based data aggregation and control system for radiation environment is proposed in chapter 4. In this chapter we have also proposed an efficient memory management module that helps data aggregation removing path delay of the data packets before processing by back-end computing nodes. Chapter-5 deals with a latency optimized clustered error correction technique in MLC flash memory chips using shortened product code. A novel algorithm using Hamming product code with selective bit placement and frame interleaving for soft error mitigation in the configuration memory of FPGA devices and its hardware implementation is described in chapter-6. Single bit and multi bit upset mitigation techniques using simple parity based coding and erasure code along priority based hardware scheduling algorithm is discussed in chapter-7. Finally chapter-8 gives brief conclusion and future scope of the thesis.

# Chapter 2

### Related Research Work

In the late sixties and seventies before different high performance electronic devices like FPGA, ASICs came into the market, FEEs in different HEP experiments were read-out by simple minicomputers in the DAQ system that could handle only a few hundred of data channels [27]. Due to lack of parallelism, standard bus architecture and interconnection it could support data rate only upto a few kilobytes per second. In 1964, Atomic Energy Commission of USA defined standards for connector, front end module, power and signal level of Nuclear Instrumentation Module (NIM) used in different HEP experiments but it did not provide any specification for the back-end bus architecture of the DAQ system [28]. In 1969, European studies on Norms for Electronics (ESONE) introduced a computer controlled modular bus architecture known as Computer Automated Measurement and Control (CAMAC) [29] but it was also lacked of parallelism and limited to low data rate applications only. Authors in [29] proposed a PC-CAMAC based DAQ system for the measurement of correlation between the positron annihilation life time and momentum of positron-electron pair using multiple detectors. In 1970, a NIM based DAQ system was developed where FEE modules were readout by a minicomputer using CAMAC as centralized readout bus architecture [30]. With the increase of detector resolution and number of readout channels, event rate of the detector increases which in turn increases data transfer bandwidth. In order to support the huge data transfer rate and data storage requirement, NIM and ESONE jointly developed a new kind of bus architecture known as Fastbus architecture. Fastbus architecture has multi-segment and multi-host architecture

Figure 2.1: Tree like distributed DAQ architecture

and supports wide bandwidth [31]. Use of microcontroller like Motorola 68000 in development of DAQ system had started in late eighties and it led to the development of another new bus architecture known as VERSA Module Europe (VME) bus [32]. Even with the presence of wide bandwidth bus architecture like Fast bus,VME or CAMAC, high speed front end module like NIM, existing DAQ systems were unable to support huge data rate required in different experiments like ALEPH experiment in CERN [33]. Typical tree like structure of DAQ system shown in Figure 2.1 consisting of FEEs in the fast level and event builders in higher level help to handle data rate of several megabytes per second. The tree like structure can handle huge data by filtering out the non interesting events using the so called multi-level triggering [34]. These DAQ structures require more complex data format for synchronization and event time stamping. Though the triggering increases complexity of DAQ system it is very useful to remove unnecessary data before storing the data and reduces overload in the high speed interconnection.

Triggering in Experimental Physics Triggering is a mechanism for deciding the events in the particle detector that need to be recorded for future data analysis in the back-end computing nodes. Triggering is very important in the experimental physics due to the limitation of computing power, data handling capability and storage capacity of the memory devices. Selectivity of a trigger is defined as the ratio of the trigger rate to the event rate [35]. In general, two types

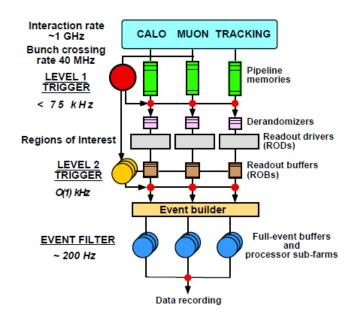

of triggers are available in experimental physics: Trivial triggers and non-trivial triggers [36]. In trivial triggers, data is recorded in a periodic interval or in a way that is independent of the properties of events being recorded. On the other hand, in non-trivial trigger events are recorded based on the properties of the events. Two parameters namely the frequency at which events occur and the complexity of each event decide the type of trigger that is needed in the experiment. In both of the cases there is one central trigger unit in the back-end that decides which events are to be recorded and based on that, it sends signal to the FEEs. This makes the FEEs more complex and there is a delay or latency for transmission of trigger from the central trigger unit to the FEEs. Trigger generally uses parallelized design that exploit the symmetry of the detector systems i.e the same kind of operations are performed on different parts of the detector systems at the same time. In global sense, the triggers are serial in nature and divided into different levels. In level triggered systems, each level decides the input of the following level that has more time and information to take a better decision. As for example, ATLAS experiment located in CERN uses three different levels of trigger [37] as shown in Figure 2.2. The first level is based on the electronics placed near the detector system and reduces event rate from 40 MHz to 75 kHz. Level-2 trigger is a part of the high level trigger (HLT) and is implemented using optimized software algorithm. Level-3 uses event filter (EF) that is also part of HLT and implemented using software algorithm [37]. With the increase in the level of trigger, data rate and global trigger rate reduces so that the first level trigger is always the fastest one compared to higher level triggers.

Though trigger based system reduces the back-end data processing complexity it may create a problem when the objective of the experiment is to record rare events. In order to record the rare events, event rate should be very high. In these cases data will be recorded initially using FEEs and then there will be an online data event selection mechanism that removes unnecessary background events before storing the data for future analysis. This process is known as self-triggered mechanism. Apart from the reduction of chance of misdetection of rare events, advantages of such self-triggered mechanism are:

• Complex event selection algorithm can be easily implemented in software compared to hardware trigger.

Figure 2.2: Schematic overview of Atlas experiment in CERN [37]

- Software based event selection algorithms can easily adapt new criteria compared to hardware based trigger algorithm.

- In self-triggered system, detector dead time due to buffer read out can be reduced.

Disadvantages of self-triggered systems are handling of huge data, global time distribution and time synchronization of the full read out chain.

Use of high speed interconnection like Ethernet, Myrinet [38], optical fiber, switch based event builders, PCIe based back plane interface helped the modern DAQ system to handle data rate and trigger signal in the order of Gigabit per second (Gbps). Apart from high speed data transfer, modern DAQ systems use complex data processing algorithm for different purposes like feature extraction, clustering and data aggregation among others. In order to implement such complex algorithms sometimes arithmetic logic units (ALU) present in general purpose processor may not be sufficient. With the increase of the channel number, more data samples enter into the DAQ in parallel and general purpose processor serialize them before processing. The efficiency of the DAQ system increases many folds if the DAQ can process the data samples in parallel. In the present era

of embedded system only FPGAs and ASICs are suitable to sort out the above mentioned problem due to presence of huge number of digital signal processing (DSP) slices (equivalent to ALU for general purpose processors) [39]. As for example, the number of DSP slices in virtex-6 series FPGA of xilinx varies from 288 to 2016 [40]. These huge number of DSP slices help to implement different complex algorithms and process data in parallel. The on field programmability, modularity makes the FPGA more suitable for modern DAQ system. High gate count in FPGA devices help modern DAQ system in different ways:

- Acceleration of complex data processing algorithm.

- Integrated system on chip based approach helps in implementing various complex functions on FPGA fabrics.

- Reconfigurability for design upgradation.

Use of FPGA like devices and PCIe like back-end interface give freedom to the designer for either on-board data processing or PCIe based backplane data processing. On-board data processing scheme processes data in different level of hierarchical DAQ network and only useful data will be sent to the computing nodes. This reduces the data processing load in the computing nodes and helps to distribute the data processing loads throughout the DAQ network. At the same time it increases the complexity of the DAQ network. In the data processing across the PCIe backplane data will be processed only in back-end computing nodes and devices in different levels of hierarchical DAQ network will act as data aggregator. Here computer in the backend should have multi-core CPU, and provide power and mechanical support to multiple PCIe cards.

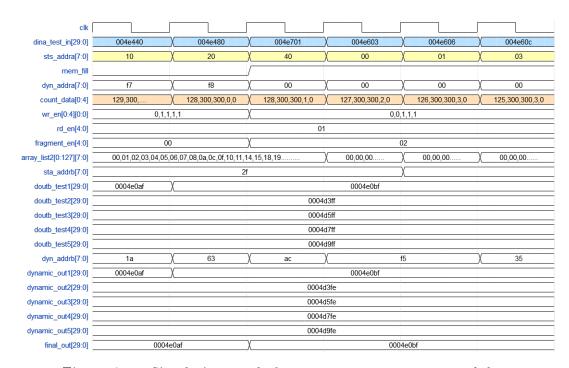

In the modern digital world, single core or even dual core 32-bit or 64-bit processors are not sufficient for implementation of complex data processing algorithm or analyze huge data. In order to support big data analysis, different companies have developed multi-core processor like Xeon by intel and Ryzen by AMD [41]. Multi-core technologies are also taking lead roles in embedded computing domain to handle huge data like Xilinx Zynq UltraScale MPSoC [42] has Quad-core ARM® Cortex™-A53 and Dual-core ARM Cortex-R5. Along with