kvi - center for advanced radiation technology

### STT Readout Status

Peter Wintz (FZ Jülich) for the STT group

61. PANDA CM, June-7th, 2017

#### **Outline STT Readout Status**

- Readout Overview

- ASIC/TRB System

- ADC-based System

- Summary

#### **STT Readout Overview**

- STT with drift time and charge readout for PID by dE/dx

- Two readout concepts for charge information

- pulse width by time-over-threshold:

- PASTTREC-ASIC with LE/TE-discriminator on front-end board, LVDS output

- TRB readout system, ASIC control by central FPGA

- pulse area by waveform sampling:

- no front-end electronics, direct straw cabling (coax,  $\emptyset$ =1.1mm)

- op-amp & sampling ADC at back-end, waveform readout & processing by FPGA

- Readout decision by Q2/Q3-2018

- Decision based on pre-series system setups and in-beam tests

- Decision process started, control panel installed, currently: definition of criteria

& deliverables

- Pre-series system set up ongoing, HW available or in production

## glied der Helmholtz-Gemeinscl

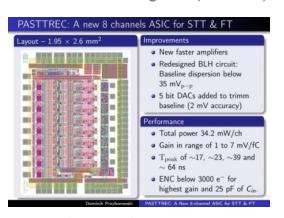

#### **Status ASIC/TRB Readout**

- ToT separation power for PID demonstrated by 2016 in-beam tests

- Large signal dynamical range covered, dE/dx: ~ 5 50 keV/cm

- PASTTRECv1 ASIC design verified, no design iteration necessary

- DAQ stable operation since ~ 1 year, 144ch test system, low NL, low thresh.

- ASIC/TRB3 readout system in phase-0 at HADES

- Two PANDA straw tracking stations with ~1800ch

- Set up during 2018, ready for beam 2018/19

1st full STS1 module (2x16 straws) with FEE adapter board.

# glied der Helmholtz-Gemeinsch

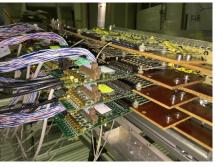

### **ASIC/TRB Test System**

- FE-boards with 2 PASTTREC-ASIC (2x 8ch), analog out (skip in final layout)

- LVDS for 16ch out + ASIC ctrl (0.5mm micro TwPair, 20 pairs), LV supply (5V)

- TRB3 readout, ~256ch per TRB3 board, ASIC control by central FPGA

- SODANet for time synchronization of multi-board system

- DAQ system (CTS) with online monitoring (TDC rates)

Straw test system and front-end electronics.

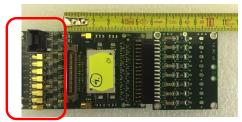

FE-board with 2xASIC, HV board. Analog out (red box)

PASTTREC parameters (design by AGH Krakow)

## tglied der Helmholtz-Gemeinsc

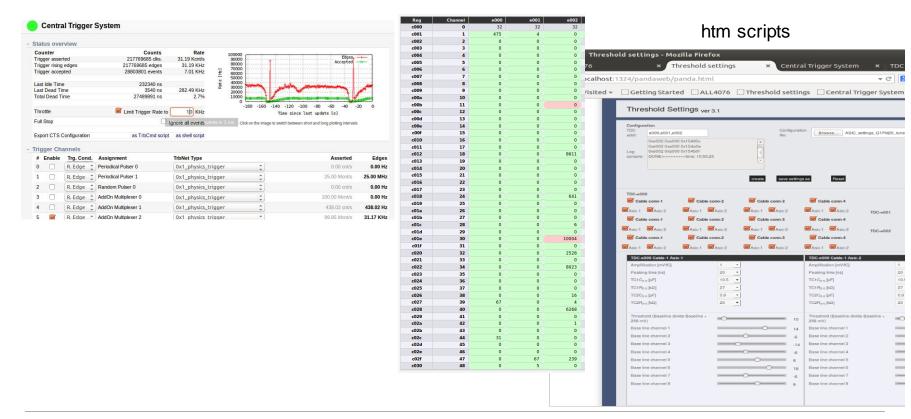

#### Readout DAQ & Control System

- By AGH & JU Krakow

- Central trigger system (CTS, GSI) for DAQ, external or channel trigger

- TDC registers, channel count rates monitor (ex. below, 6mV, no HV, 10sec)

- ASIC control (gain, PkT, TC, BL restor., thresh, individual ch BL ..)

#### **ASIC/TRB – Readout Status**

JÜLICH FORSCHUNGSZENTRUM

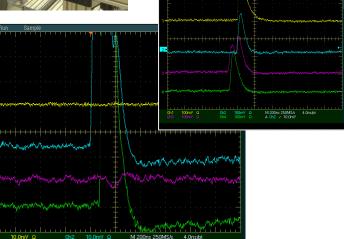

(Raw Spectra from April 2016 Beam Time)

In-beam position of straw setup (beam from the right)

FEB replaced later (ch1-16)

ASIC analog output signals (in-beam), NL <5mV (stable), thresh. at 10mV

TDC time (top) and time-overthreshold (below) vs channel

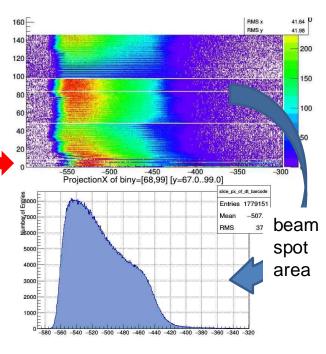

### dE/dx Separation by Time-over-Threshold

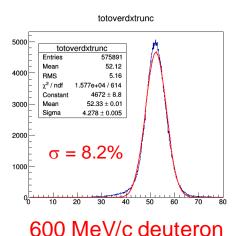

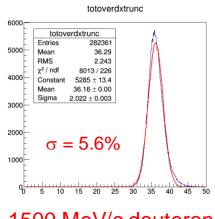

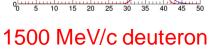

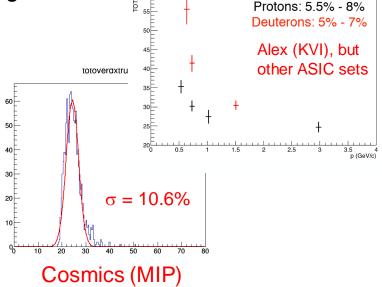

$\Sigma$ ToT /  $\Sigma$ dx per track seems better than  $\Sigma$  (ToT/dx)

Summary of TOT/dx

- better gaussian shape, only low truncation necessary

- no ASIC saturation (e.g. ion TC) seen for 600 MeV/c deuteron (dE/dx ~50 keV/cm)

- prelim.: S  $\cong$  5.1 deuteron separation, compare to S  $\sim$  9 in TDR ( $\pi/K$  at 0.23 GeV/c)

- very prelim:  $S \cong 8.1$  separation power for MIP & 600 MeV/c deuteron

further analysis and improvements ongoing

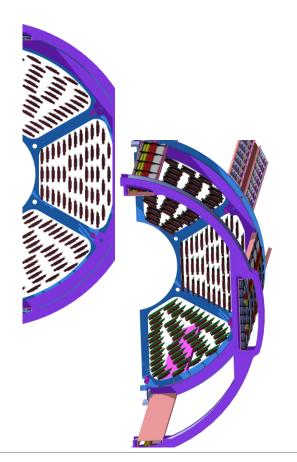

### **ASIC/TRB Front-End Layout**

#### Tasks done:

- Positioning of 134 FE boards per semi-barrel and

- Individual straw and FEB-channel association

- Challenging for close-packed straw geometry with increasing straw number in radial layers

#### Next:

- One STT sector set up as pre-series system

- Cable routing scheme

- Cooling scheme for 2x64 Watt (forced convection)

# tglied der Helmholtz-Gemeinsc

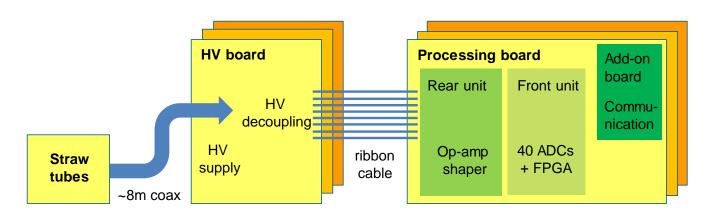

#### **ADC-Based Readout System**

- "Front-end electronics free"

- Direct straw cabling, mini coax (∅=1.1mm), tested HV stable

- HV supply, HV decoupling backend

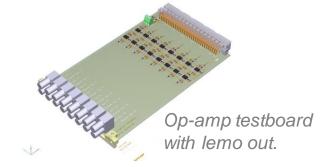

- Integrated op-amp, ADC and processing FPGA, add-on communication

- 3-stage op-amplifier, 20ns PkT, gain factor 400, 20 MHz BW, 100 mW

- Low power 4-ch ADC (HMCAD1520), 160 MSPS, interleaving mode (1000MSPS)

- One central FPGA (Xilinx Virtex 7) for 40 ADCs per readout board (160 ch)

Scheme of ADC-based readout system

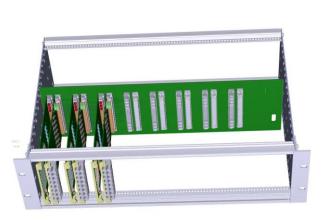

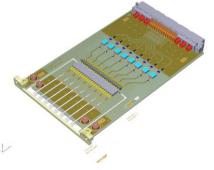

### **HW Designs**

- HV crate with decoupling boards, coax lines with plug instead of soldering

- Samtec ribbon cable to processing crate, cross-talk tests next

- Testcrate with additional amp-board for test of signal analog part

- Pre-series (final) crate with more slots (416 ch per crate, 26 boards)

HV crate for tests with HV decoupling boards and additional amp board.

HV supply and decouple board. Plug for coax lines.

# itglied der Helmholtz-Gemeinsc

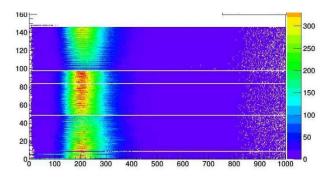

#### **Status ADC-based Readout**

- 16 ch prototype test in-beam in 2016

- Amplifier characteristics verified (2x diff. gain factor + logarithmic tested)

- Signal processing algorithms developed

- Different ADC sampling rates and influence on time/spatial resolution tested

- Pre-series system set up next, ~ 400 ch, in-beam tests

- HW in production, RO board available in September for 1<sup>st</sup> HW tests

- DAQ system set up and tests

- Cosmic tests prior to next beam time

## tglied der Helmholtz-Gemeinsc

#### **Summary**

- Pre-series system set up (~ 400 ch) for both readouts in Q4/2017

- Cosmic tests (extended) next

- Beam time planned for March + April 2018

- Proton and deuteron beam at COSY, 0.5 3.0 GeV/c, dE/dx ~ 5-50 keV/cm

- In-beam tests for both readout systems

- Performance results as basis for readout decision.

- Further criteria to be considered (costs, maintenance, ..)

- Readout decision planned for Q2/Q3 2018

- Then: full integration of readout system into PANDA (mech., DAQ, simu., ..)

# Thank you for your attention