# Status Update on the Activities on PASTA

Alessandra Lai, Forschungszentrum Jülich, 6 December, 2016

# Outline

**PASTA Readout Chain**

**Fixes for Known Bugs**

**New Developments**

Data Analysis - Preliminary

Summary

Outlook

Alessandra Lai | Status Update on the Activities on PASTA | 6 December, 2016

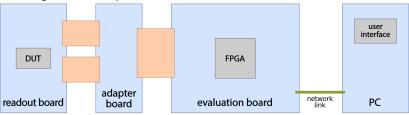

# JDRS: Jülich Digital Readout System

The basic components

### Jülich Digital Readout System (JDRS).

Data conversion and communication with the PC:

- DUT: ToPix, PASTA

- evaluation board: Xilinx ML605 (Virtex-6 FPGA)

- firmware: VHDL

Configuration and data handling:

- PC

- software: C++

- MVD readout framework (MRF)

- Qt-based GUI

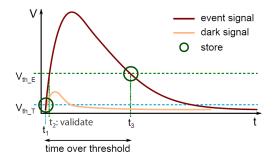

# **PASTA: PANDA Strip Asic**

Free running readout chip for the strips

Concept: measurement of points in time based on two leading-edge discriminator outputs.

- Low threshold time branch: resolve leading edge of pulse.

- High threshold energy branch: falling edge, pulse length (i.e. deposited charge)

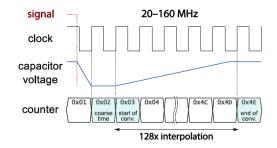

## **Timestamps**

- Clock resolution: 6.25 ns (@160 MHz) coarse timestamp.

- Enhanced resolution: up to 50 ps fine timestamp.

- t\_coarse  $\rightarrow$  leading edge of the clk after threshold crossing.

- $t_{fine} \simeq t_{eoc}^{1} t_{soc}^{2}$

<sup>1</sup>end of conversion <sup>2</sup>start of conversion

# **Bug Fixes**

Bugs reported @MVD meeting during June CM have been fixed:

- bug in channel configuration (address)

- bug on 10b/8b decoding (synchronization)

- problem on the transmission line (inversion)

Another bug in the local configuration not visible during configuration, affected the behavior of the chip:

```

constant DEFAULT_CH_CONFIG : std_logic_vector(CH_CONFIG_SIZE-1 downto 0) :=

'0' & -- 41 finish config

-- analogue configuration

b"1010" & -- 40..37 Iref_ratio, energy

b"1010" & -- 36..33 Iref_ratio, time

b"00000" & -- 32..28 HCLDAC_e

b"00000" & -- 27..23 HCLDAC_t

'0' & -- 22 not used

b"1000" & -- 21..18 If

...

```

By default all channels are enabled in a test mode. I.e. they all receive the test pulse.

$ch\_test\_configuration \rightarrow$  single channels to sensor or calibration circuit

| Global | Globa  | al (Ex | (pert) | C   | hann | el (Expert) I | Cha | nnel ( | Expe | rt) II | Te | st Pu | lse |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|--------|--------|--------|--------|-----|------|---------------|-----|--------|------|--------|----|-------|-----|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Channe | I Conf | liaur  | atio   | ,   |      |               |     |        |      |        |    |       |     |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|        |        | -      |        |     |      |               |     |        |      |        |    |       |     |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| It     | em     | Pos    | Len    | Min | Max  |               | 0   | 1      | 2    | 3      | 4  | 5     | 6   | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 |

| 1 test | config | 0      | 1      | 0   | 1    |               | 1   | 1      | 1    | 1      | 1  | 1     | 1   | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

## **Channel Scan**

- Define the type of injection.

- Scan a user define range of channels.

- Choose up to two parameters to sweep (at present, global thresholds and pulse amplitude available).

| test pulse to TDC (digital)                          | ✓ two param scan       |

|------------------------------------------------------|------------------------|

| <ul> <li>test pulse to front-end (analog)</li> </ul> | First Loop Second Loop |

| ch start 0                                           | HCGDACn - HCGDACp -    |

| ch stop 63                                           | start 0 🜲 start 0 🜲    |

| curr ch                                              | stop 15 🜩 stop 15 🜩    |

|                                                      | step 1 🔹 step 1        |

|                                                      | start scan             |

## **Data Handling**

- FPGA data handling:

- 10b/8b decoded data stored in FIFO.

- Software data handling:

- request data from fifo.

- store raw data in ASCII file (hex).

- convert data word into usable object.

| pathname:            |                                |

|----------------------|--------------------------------|

| oftware/GUI_modules/ | /daqReader/readoutData/decode/ |

| ilename:             |                                |

| test.dat             | ✓ suppress comma words         |

| rest.uat             | ✓ display frame indicator      |

| Save using:          | suppress empty frames          |

| ASCII                | auppress empty names           |

| boost serial         | readout iterations 200 🌻       |

|                      | current iteration              |

|                      | start readout stop readout     |

- Suppress comma words

- Display frame indicator

- Suppress empty frames

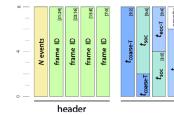

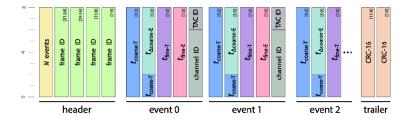

## **Data Format**

#### Full mode: two words per event not decoded in the software.

t<sub>coarse-T</sub>

trailer

CRC-16

Compact mode: one word per event decoded in the software .

Alessandra Lai | Status Update on the Activities on PASTA | 6 December, 2016

# **Empty Frames Suppression**

#### Problem:

After the FIFO buffer(s) are completely filled  $\rightarrow$  data loss inbetween two readout requests.

Solution:

Different (more or less) complicated options to fix this. Quick and efficient workaround for testing phase

- $\longrightarrow$  suppression of empty frames @FPGA level.

- $\implies$  Sufficient for high intensity beam?

## Data Analysis - Preliminary

Offline data analysis in ROOT.

- Import decoded data from ASCII file.

- Store it in a TTree.

- Several macros available for different analysis.

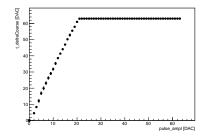

# **TOT Linearity**

#### Rough extimation of the time over threshold: $t_{\Delta coarse} = t_{coarseE} - t_{coarseT}$

- Saturation at  $t_{\Delta coarse=}$  63 due to compact mode:  $\rightarrow$  value transmitted using only 6 bits.

- Maximum amplitude detectable @50 MHz: 1.3 μs.

- Maximum amplitude detectable @160 MHz: 400 ns.

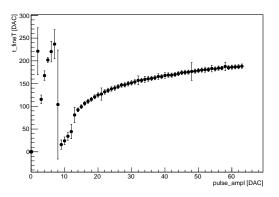

# Fine Time - Time Branch

$t_fine \simeq t_eoc - t_soc$

Discontinuity (probably) due to which clock edge is used for calculation (i.e. the first one after a falling edge).

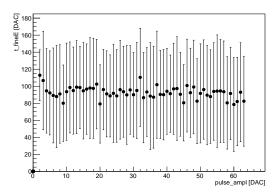

# Fine Time - Energy Branch

$t_fine \simeq t_eoc - t_soc$

- Falling edge slower than the rising edge.

- Susceptible to noise.

- Jitter in the timestamp.

- Quite big error bars. (?)

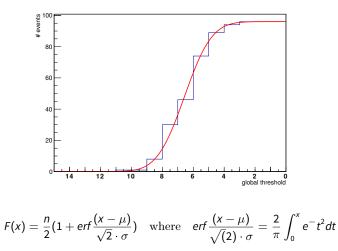

# **Threshold Scan - qualitative**

Global thresholds

- $\Delta_{th} = HCGDAC + -HCGDAC -$

- $\longrightarrow$  midvalue of an interval with predefined amplitude.

- Sweep over  $\Delta_{th}$  at fixed pulse amplitude.

- Expected: S-curve shape.

- Observed: box-like shape

- $\longrightarrow$  for pulse amplitude > 2 the signal is already above threshold.

## **Threshold Scan - qualitative**

Global thresholds

Pulse amplitude = 1

Alessandra Lai | Status Update on the Activities on PASTA | 6 December, 2016

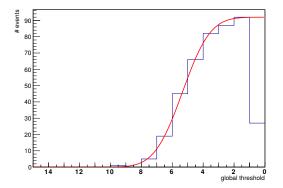

## **Threshold Scan - qualitative**

- Not all the channels behave the same  $\rightarrow$  no threshold distribution. n.

- Events loss at small  $\Delta_{th} \rightarrow$  lower limit of interval below baseline.

Possible improvements:

- fine tuning with local thresholds

- adjusting the baseline voltage

Alessandra Lai | Status Update on the Activities on PASTA | 6 December, 2016

## Summary

- Development of the JDRS is ongoing.

- Tools for first analysis of data from PASTA available.

- Overall behavior of the chip still unclear (e.g. channels behave differently).

- Need input from the experts on how to tackle this problem.

# Outlook

- Calibration of the DAC for meaningful estimation of noise etc.

- Understand behavior of nasty channels.

- Continue analysis towards chip characterization.

- Continue developing JDRS with needed features.

- Implementation in the firmware of a test pulse with configurable phase shift wrt the clock.