# The Silicon Tracking System of the CBM experiment at FAIR

Anton Lymanets<sup>1,2</sup> for the CBM collaboration

14th Vienna Conference on Instrumentation

February 15 - 19, 2016 Vienna University of Technology

- <sup>1</sup> GSI, Darmstadt, Germany

- <sup>2</sup> Institute for Nuclear Research, National Academy of Sciences, Ukraine

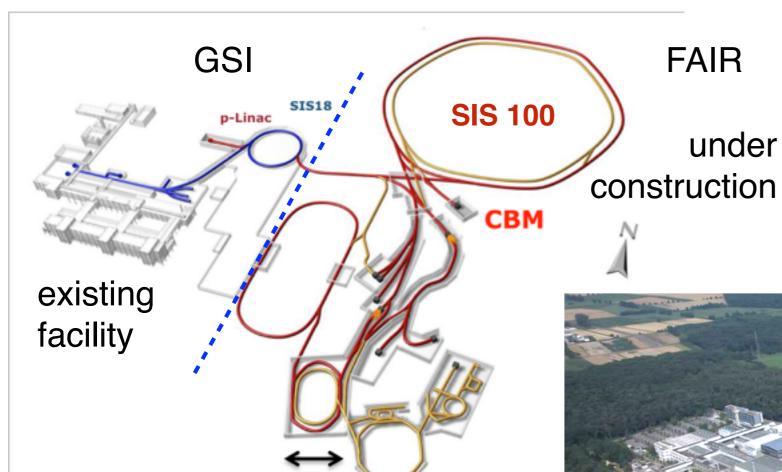

## Facility for Antiproton and Ion Research

**SIS-100**

protons: 30 GeV

Au: 8 AGeV

Aerial photo of the construction site taken on July 27, 2013 (photo: Jan Schäfer for FAIR)

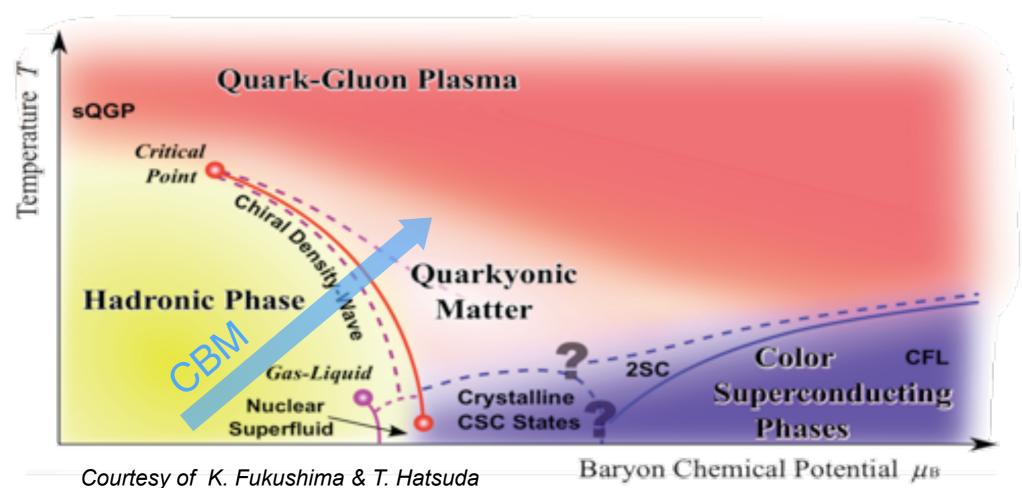

# QCD phase diagram

- nuclear matter formation at high baryon density and temperature

- models predict 1<sup>st</sup> oder phase transition with formation of mixed and exotic phases

- existence of critical end-point

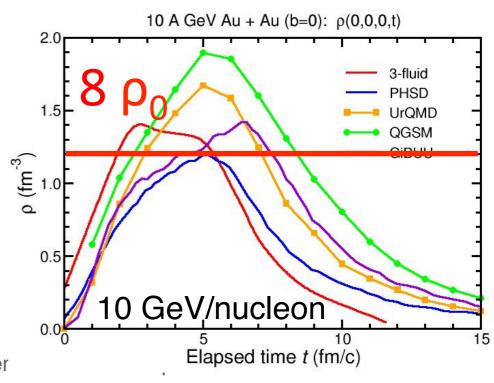

### Probing the dense fireball

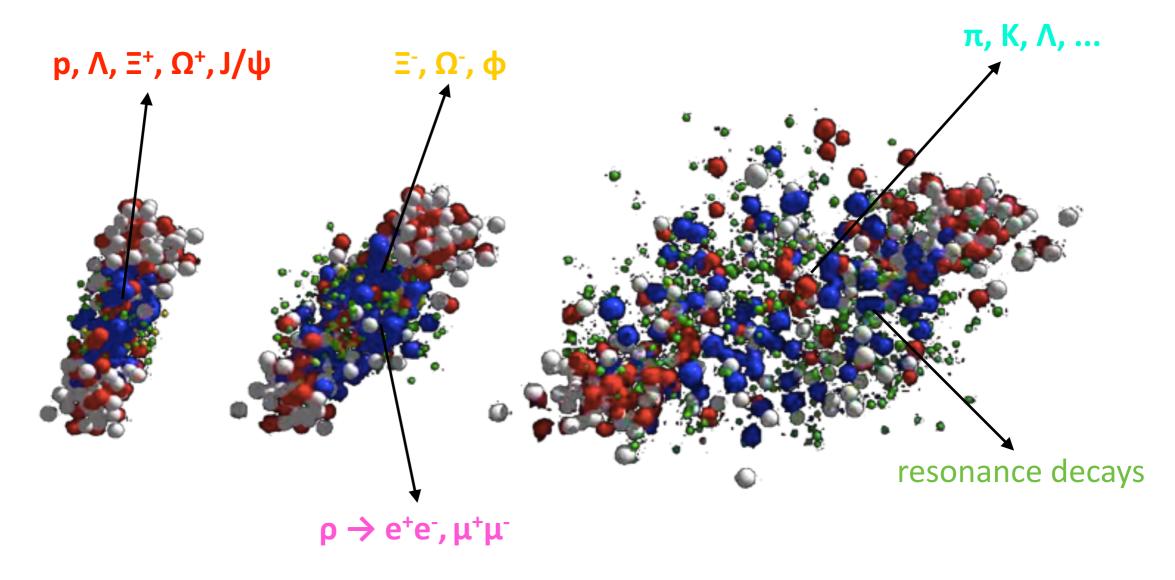

Au+Au collision at 10.7 GeV/nucleon as simulated in the UrQMD transport code

- Leptonic and hadronic signals from all stages of nucleus-nucleus collisions

- Rare probes: multistrange hyperons, low mass vector mesons, charmonium, strange dibaryons, hypernuclei.

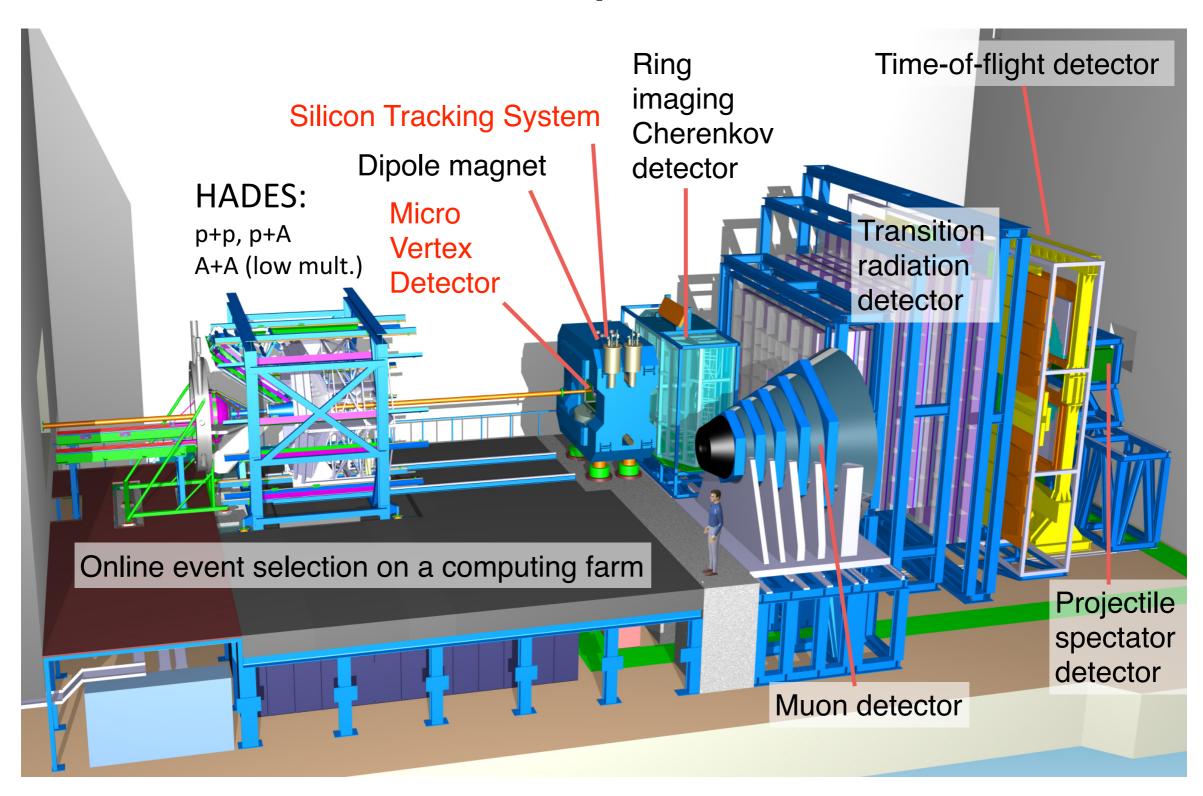

## **CBM** experiment

Vertexing: MVD

Particle ID: RICH, TRD, ToF

Tracking: STS, MUCH, TRD, ToF

· Calorimetry: ECAL, PSD

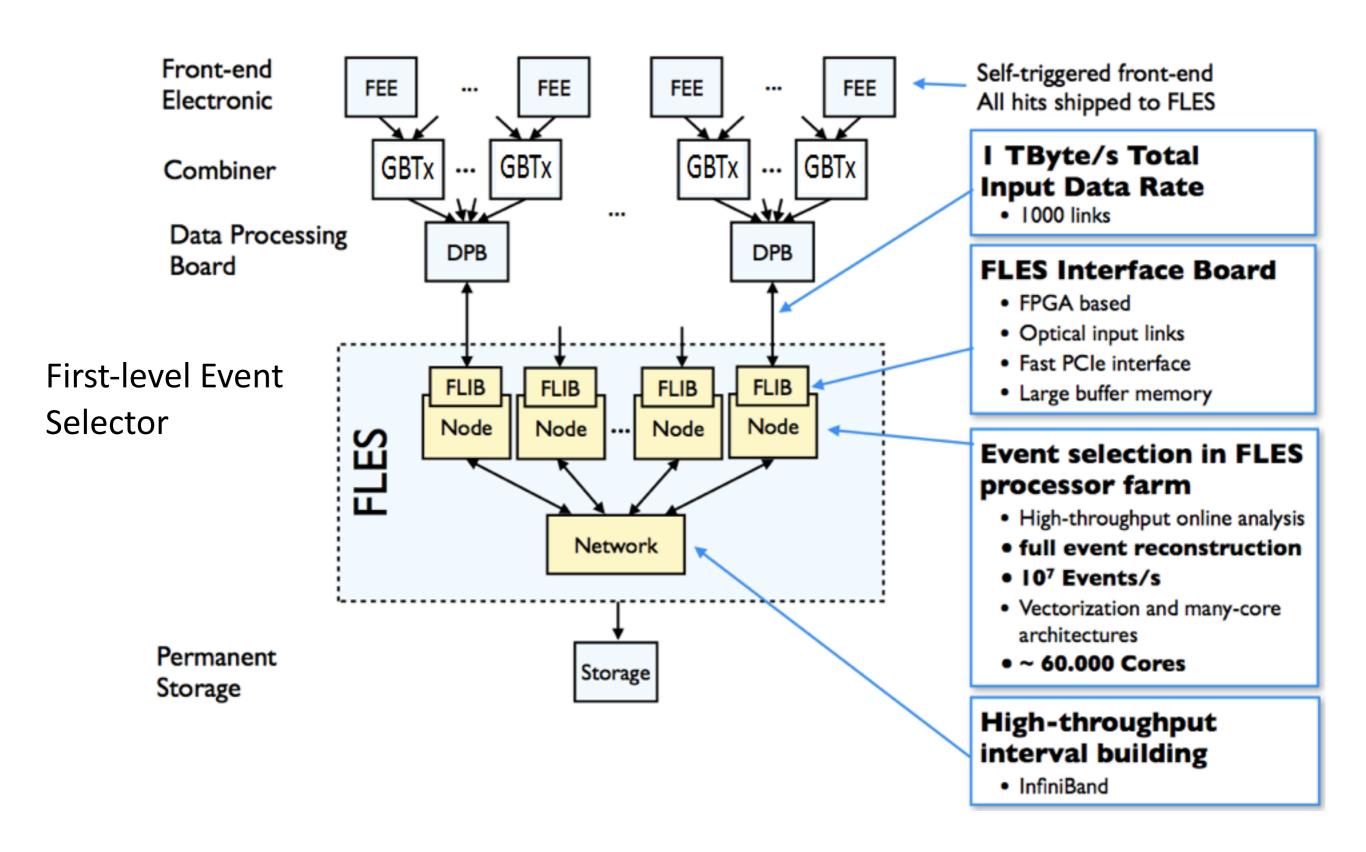

#### Online data flow

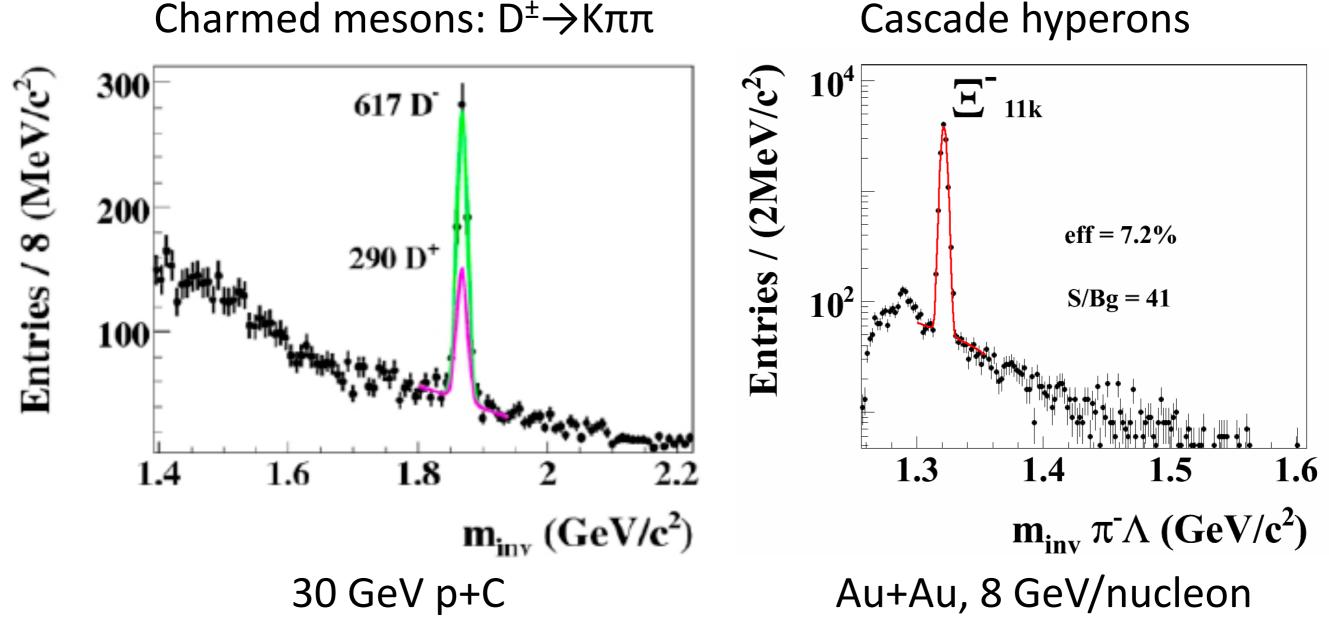

## Feasibility studies at SIS-100

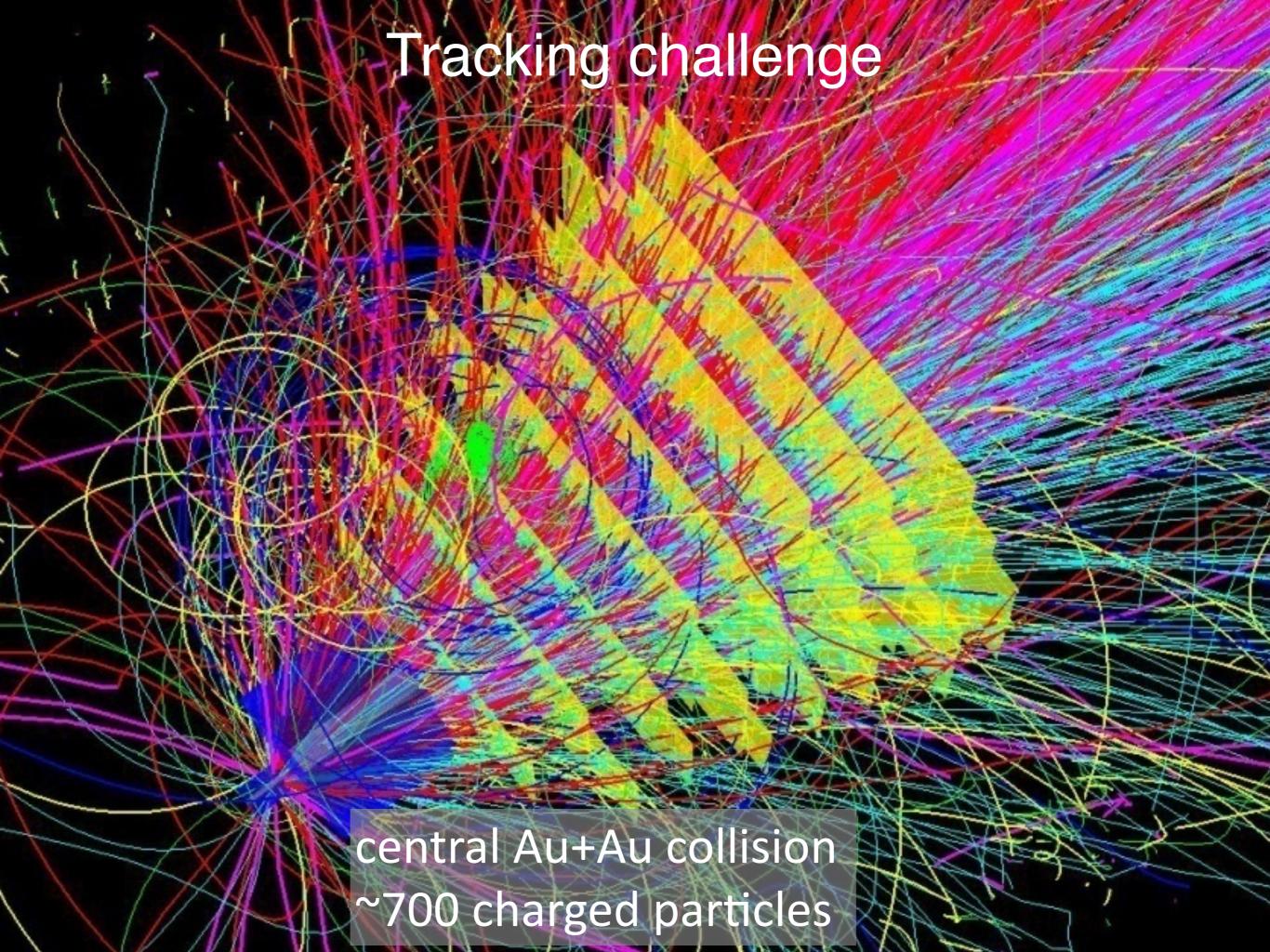

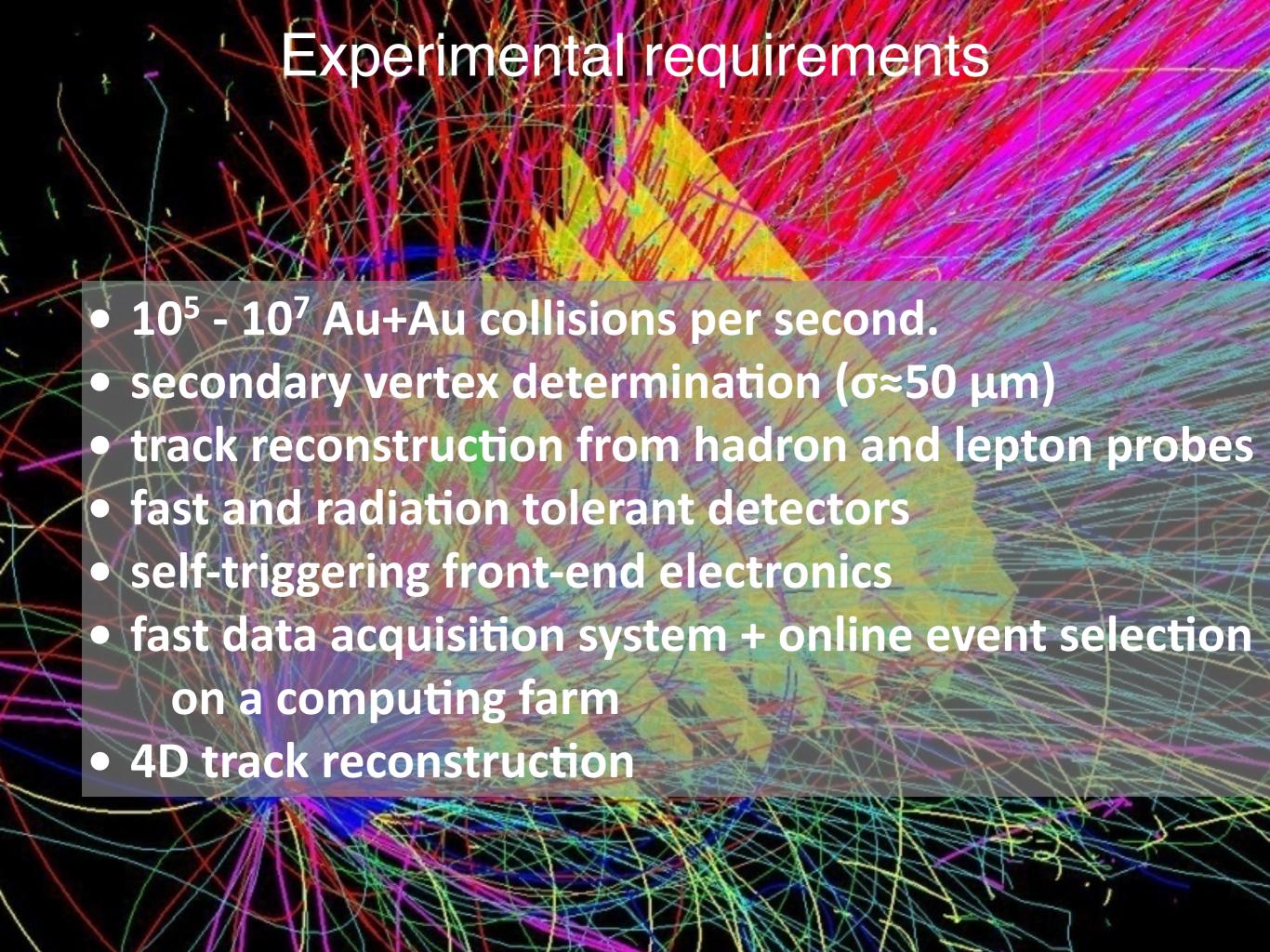

Operation scenario: Au+Au, C+C at 4, 6, 8, 10 GeV/nucleon

Example: 10<sup>6</sup> central events, interaction rate 100 kHz – 1 MHz

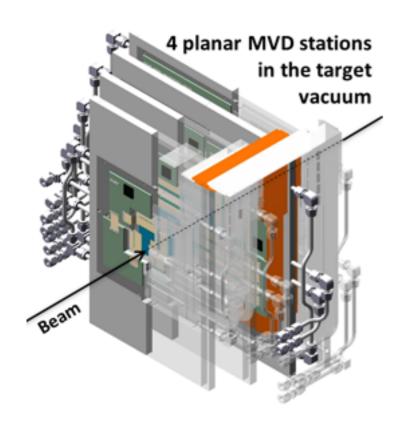

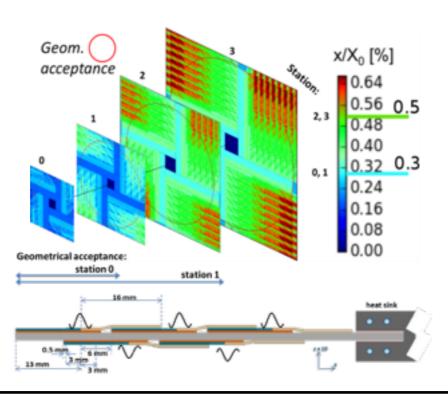

#### **CBM Micro Vertex Detector**

#### **Ultra-thin: CVD diamond, TPG**

#### **Sensors: CMOS MAPS**

Radiation hard, •Thinned to 50 μm, •< 150 mW/cm<sup>2</sup>, •spatial resol. < 5 μm, •R/O several 10 μs/frame

#### **Prototyping & test beam:**

#### **MVD** demonstrator

**RVC** foam

#### **MVD** prototype

#### **PRESTO**

#### **Customized FEE & DAQ:**

**TRB-based** 80 pin flat cable

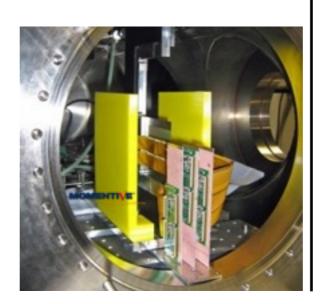

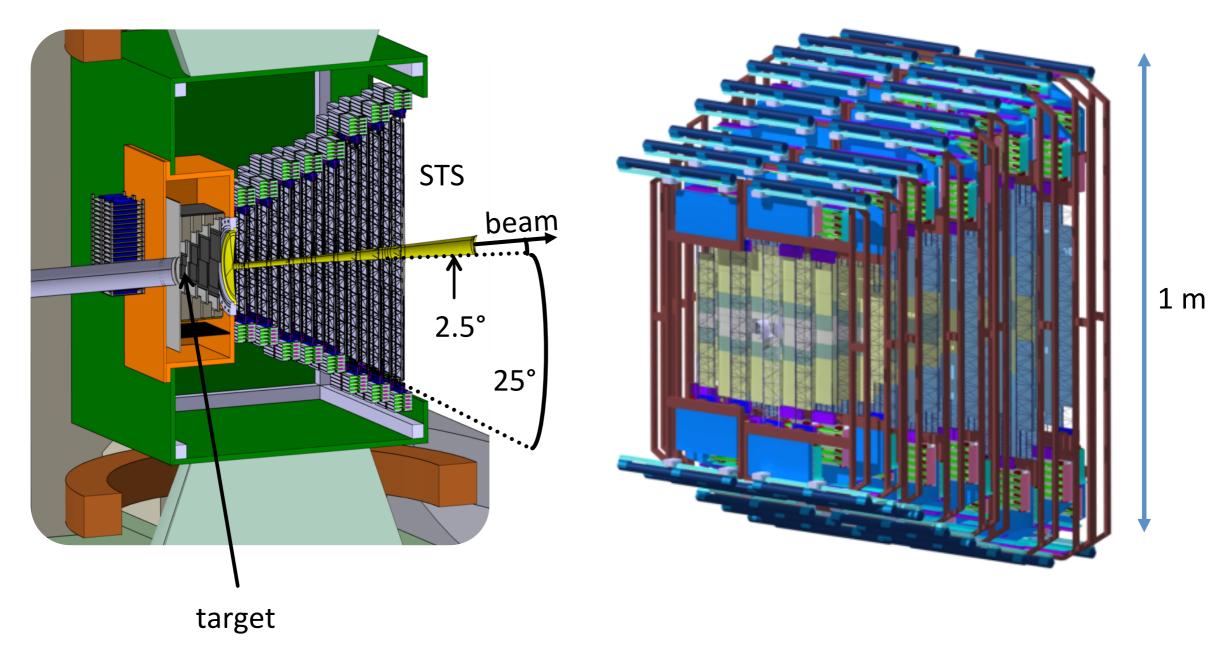

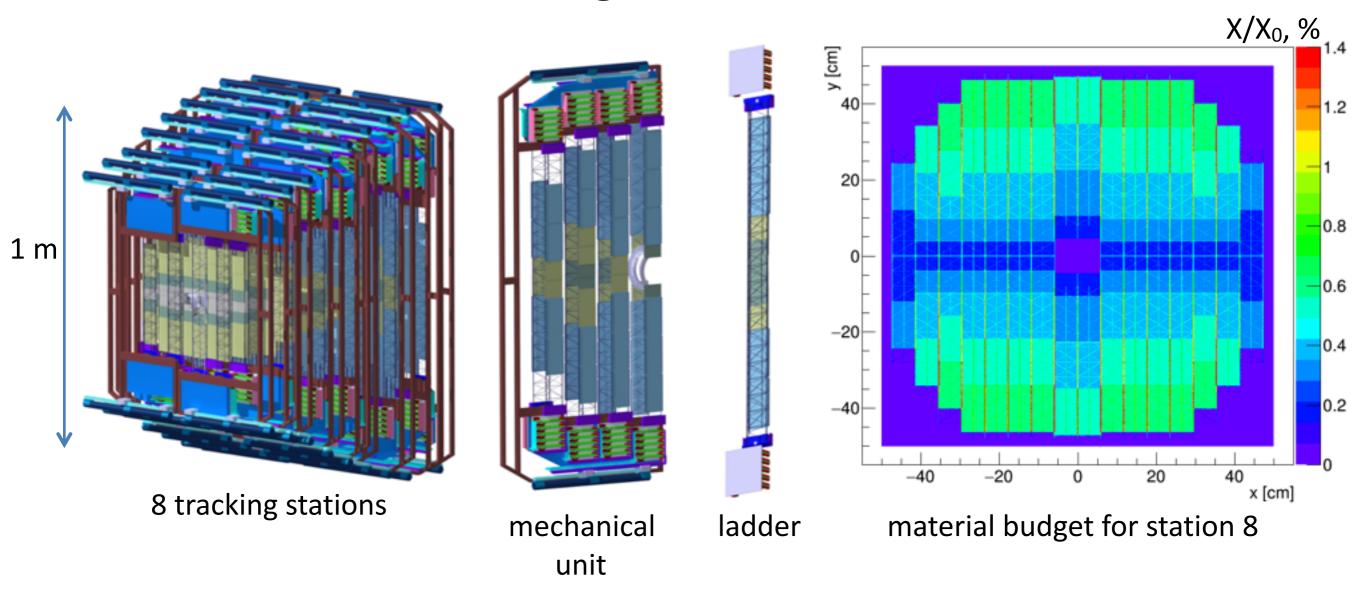

# Silicon Tracking System

- 8 tracking stations in the magnet aperture

- double-sided silicon microstrip detectors

- Acceptance:  $2.5^{\circ} < \theta < 25^{\circ}$

- Active area: 4 m<sup>2</sup>

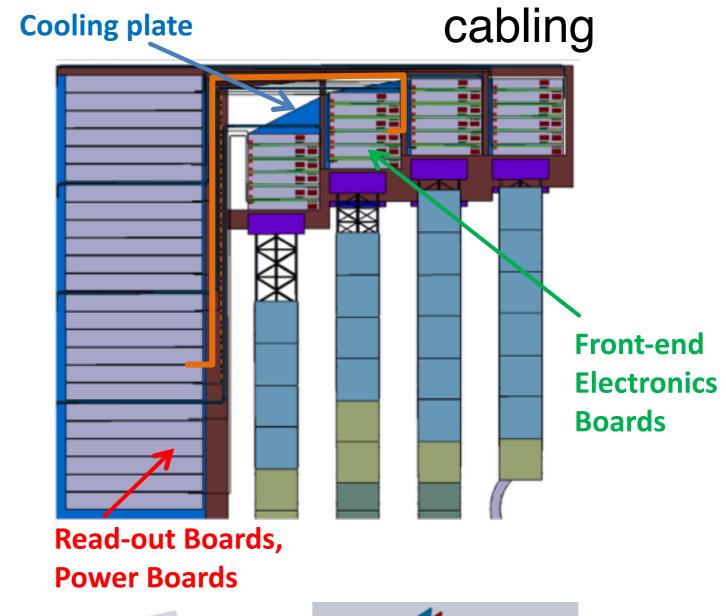

# STS integration concept

896 detector modules including:

1220 double-sided microstrip sensors

- ~ 1.8M readout channels

- ~ 16 000 readout chips

- ~ 16 000 ultra-thin readout cable stacks

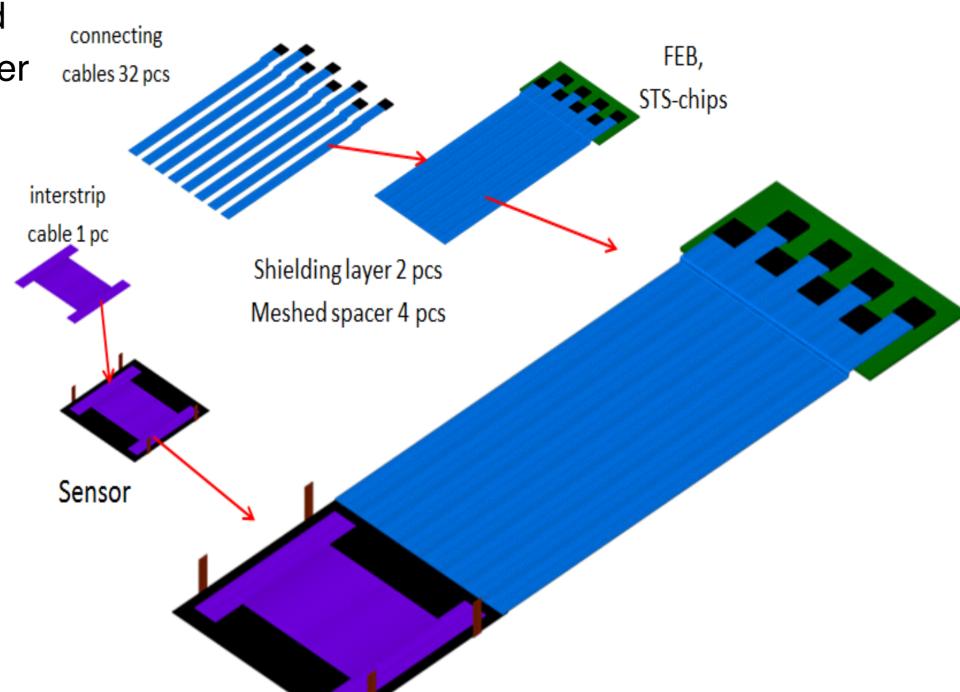

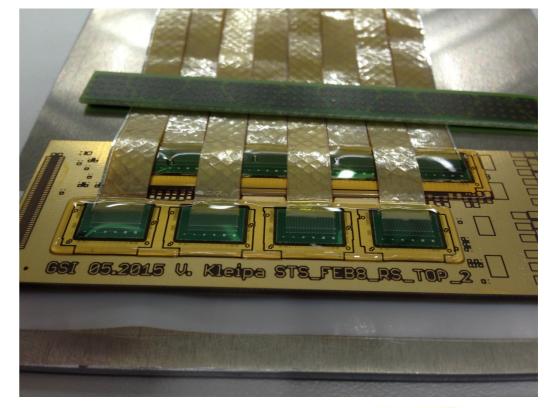

#### Detector module concept

896 modules required4-5 modules per ladder

#### Modules comprises:

- · sensor

- analog mirocables

- front-end board

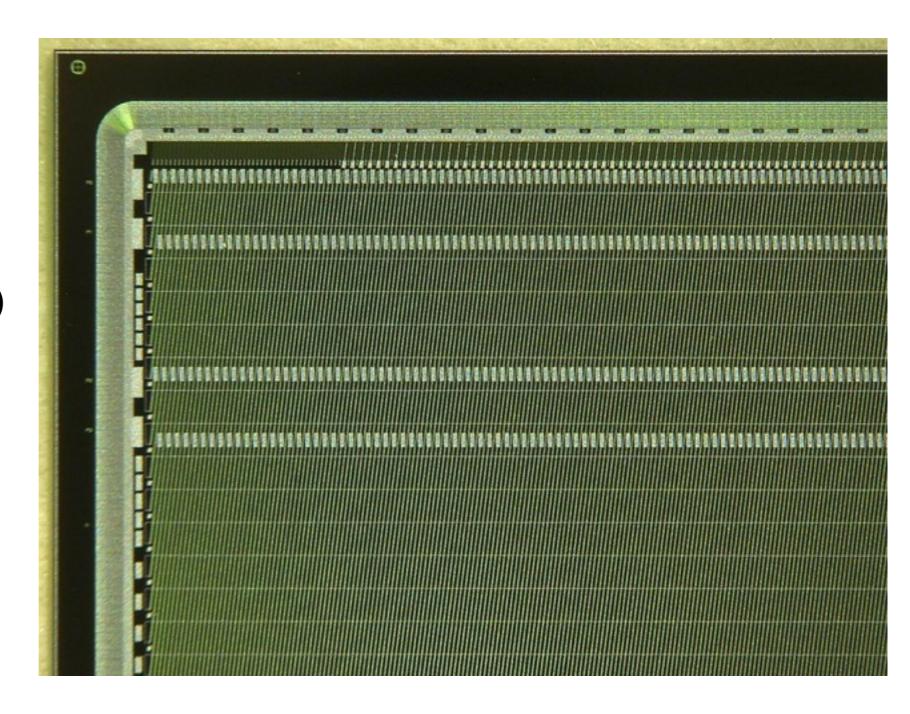

## Silicon microstrip sensors

- double-sided

- 1024 channels per side

- 58 *µ*m pitch

- 300  $\mu$ m thick

- stereo angle 7.5°(p-side)

- dimensions:

6×2 cm<sup>2</sup>, 6×4 cm<sup>2</sup>,

6×6 cm<sup>2</sup>, 6×12 cm<sup>2</sup>

- 2<sup>nd</sup> metallization to interconnect short corner strips

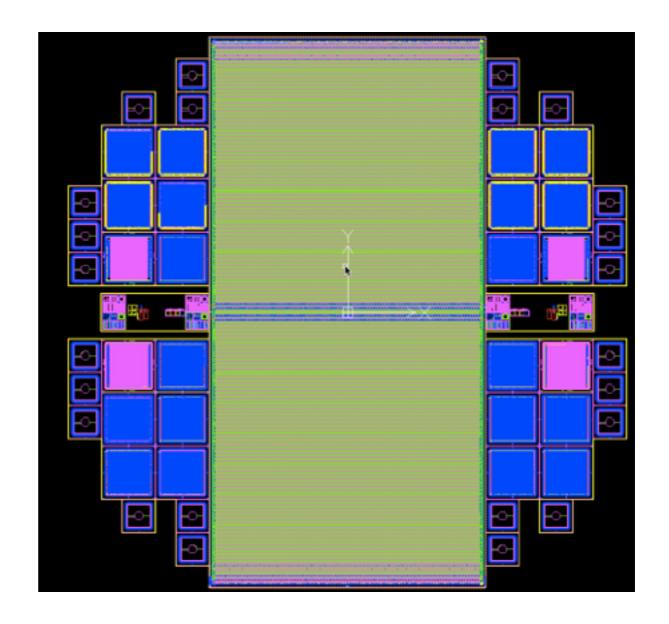

## Silicon microstrip sensors

two daisy-chained sensors

6×12 cm<sup>2</sup> sensor design with readout pads in the middle of the sensor (in production by Hamamatsu)

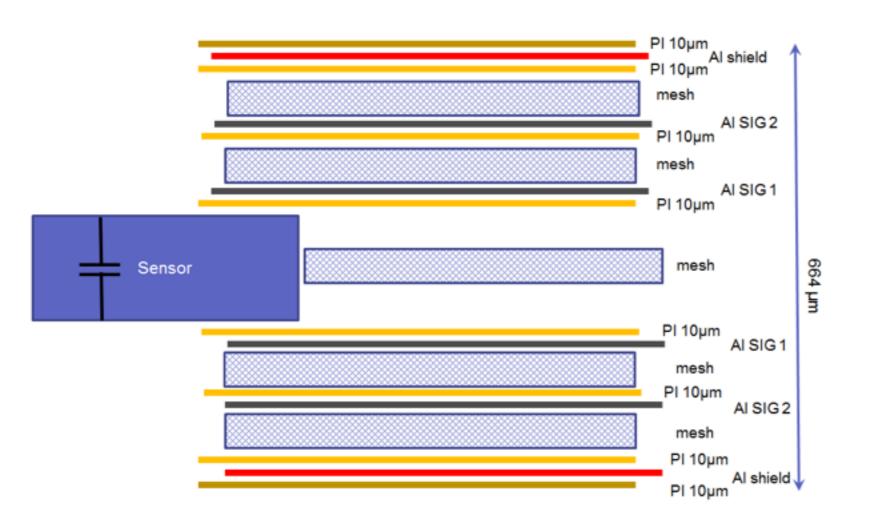

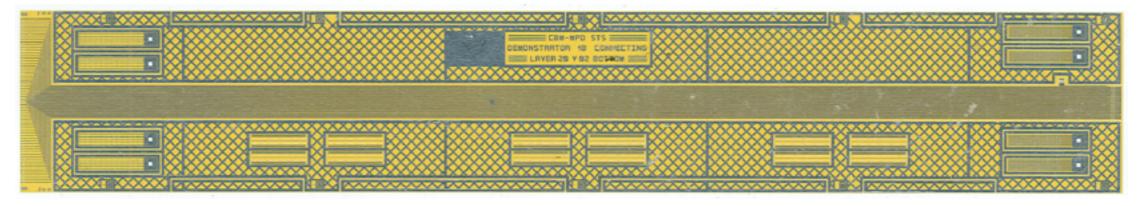

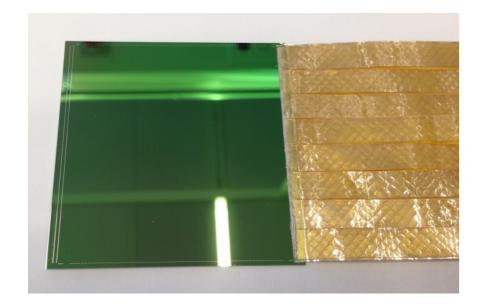

#### Microcables

14th VCI conference, 16 Feb 2016

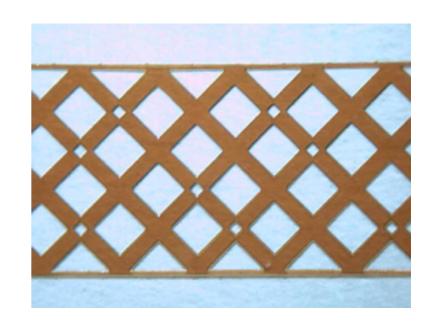

meshed spacer

signal layer: 64 Al lines of 116 μm pitch, 10 μm thick on 14 μm polyimide, lengths up to 55 cm

Material budget: 0.228  $X_0$  (equivalent to 213  $\mu$ m Si)

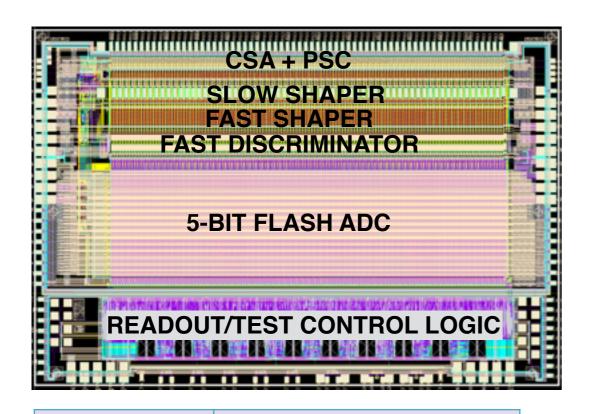

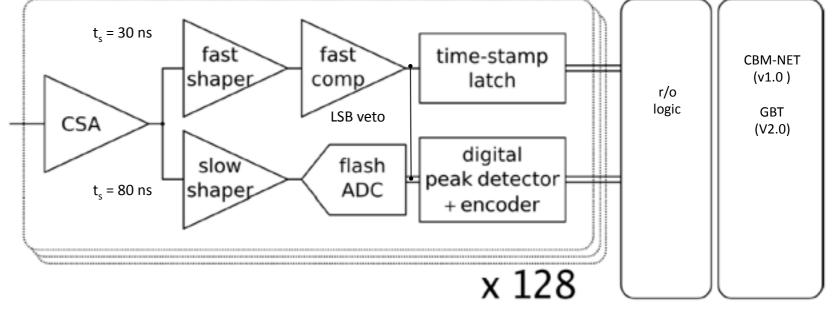

#### STS-XYTER ASIC

#### **STS-XYTER ASIC**

- data driven architecture

- fast branch: time-stamp

- slow branch: signal digitization

- double-threshold discrimination: time stamp is vetoed if ADC produced no signal

| channels      | 128, polarity +/-                 |

|---------------|-----------------------------------|

| noise         | 1000 e <sup>-</sup> at 30 pF load |

| ADC range     | 16 fC, 5 bit                      |

| clock         | 250 MHz                           |

| power         | < 10 mW/channel                   |

| timestamp     | < 5 ns resolution                 |

| out interface | 4(5) × 500 Mbit/s LVDS            |

17

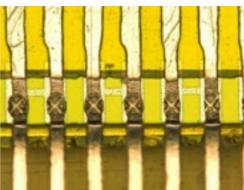

#### Detector module assembly

TAB bonding of microcables to ASICs and sensors

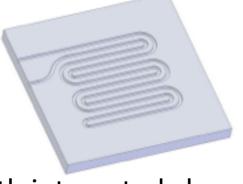

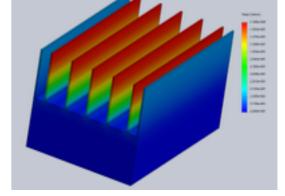

# Current engineering studies

cooling

TRACI XL: 1 kW cooling prototype

bi-phase CO<sub>2</sub> cooling system STS electronics total: 42 kW

FEB stack 200 W

cooling plate with integrated channels

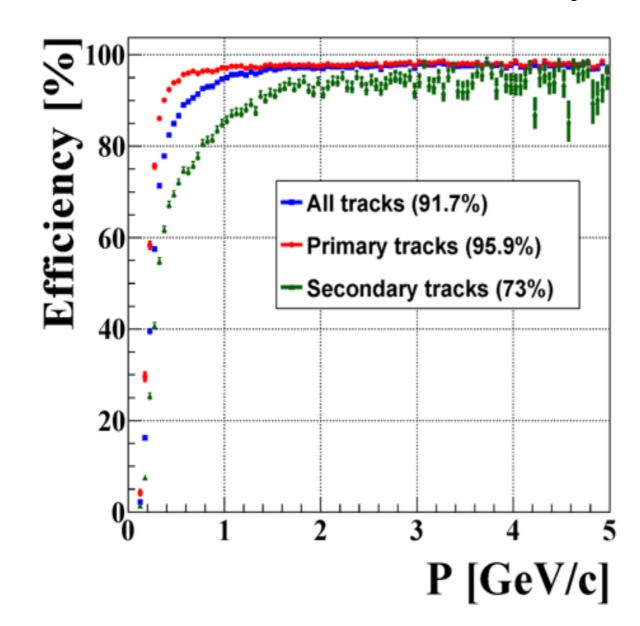

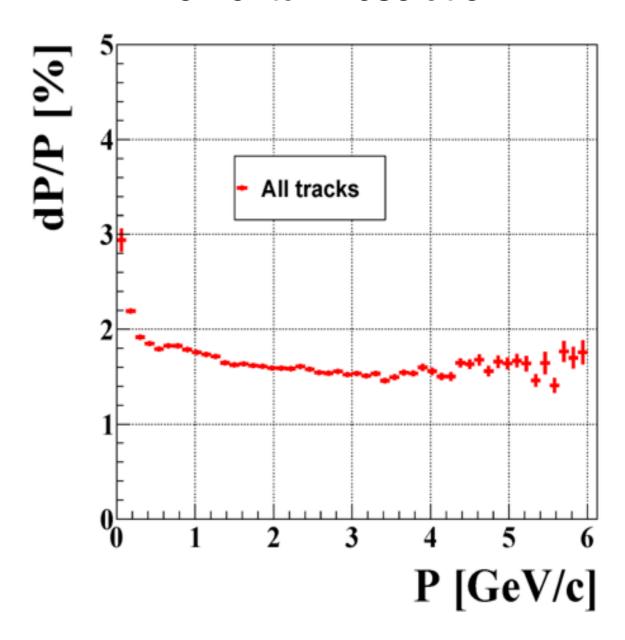

## STS performance simulation

#### Track reconstruction efficiency

#### Momentum resolution

- realistic detector model

- CbmRoot simulation framework

- Cellular Automaton track finder

- Kalman Filter track fitting

## Summary

- STS system concept has been presented

- Detailed geometry has been assessed in simulations: performance OK

- Current activity is module assembly and system integration

- Full-size module mockup has been produced

- Production readiness by the end of 2016

#### **BACKUP**

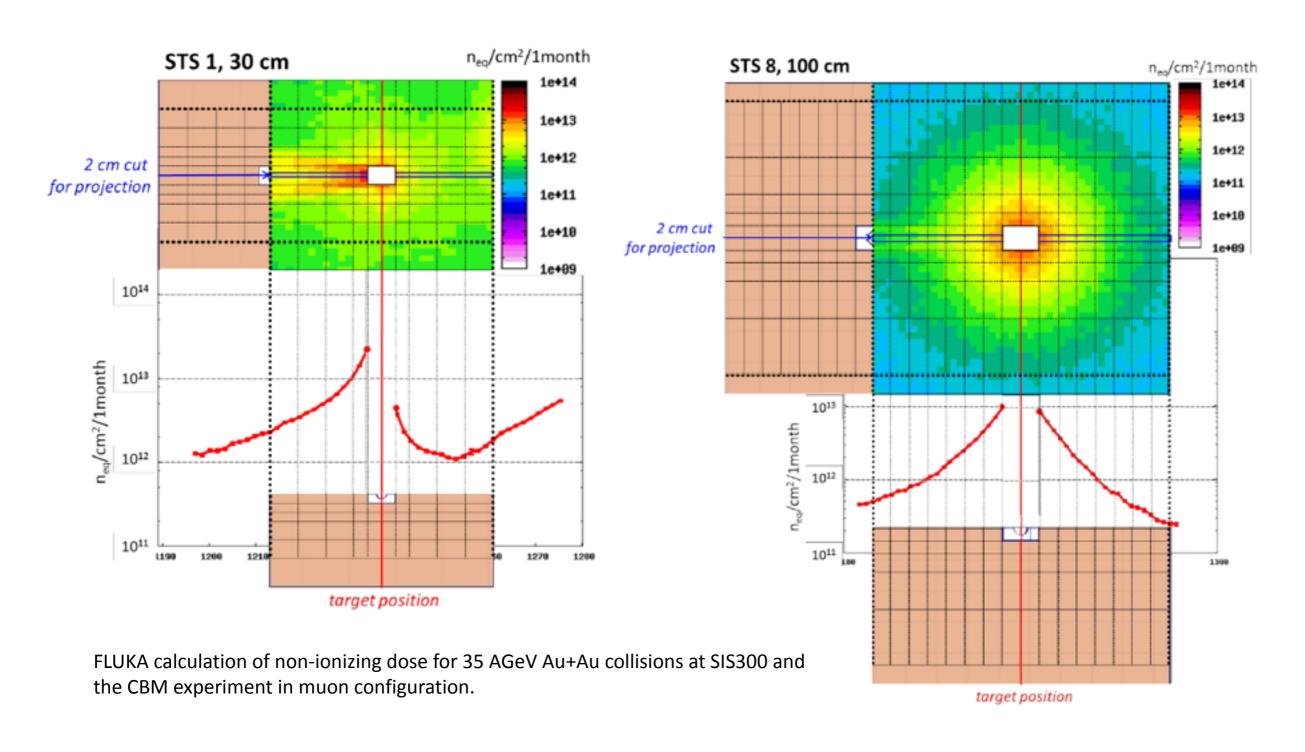

# Radiation environment