# Some updates on the electronics for the data link

Daniela Calvo Paolo De Remigis Cecilia Giovinazzo Marco Mignone Richard Wheadon

November 30, 2015

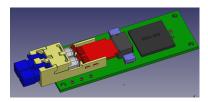

# The board design for the GBT link

#### Board top view

The first design aiming to the final dimension.

GBTX ASIC and VTRX transceiver on the same side.

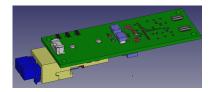

#### Board bottom view

Passive parts distributed on both sides.

Aluminium cable connectors on the bottom side.

# The change in the new board design

- Due to cooling constraints the GBTX has been moved on the bottom side.

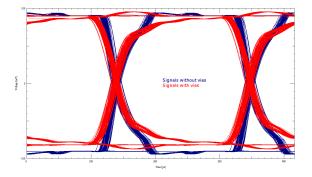

- Vias have been added on the high speed tracks, with moderate effects at first glance.

De Remigis — Updates on the electronics — November 30, 2015 3/10

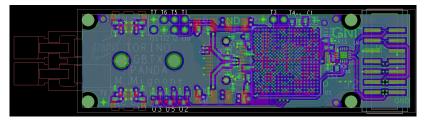

## The submitted board design

- The board submitted for production is once more different due to the connectors for the E-link.

- The board delivery is expected for the next January, waiting for the parts compatible with the magnetic field.

# The Versatile Link Demo Board

#### Versatile Link Demo Board

The first Versatile Link Demo Board (VLDB) is just received.

The VLDB will be used as data source for the GBT-FPGA.

#### Versatile Transceiver

The Versatile Transceiver (VTRX) is used on the VLDB.

The 4.8 Gbit/s VTRX will be also used on the custom board.

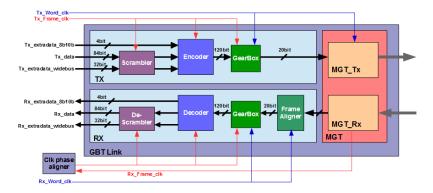

### The GBT-FPGA firmware

- The GBT-FPGA firmware has been configured to be implemented on a ml605 evaluation board with a Virtex6.

- Due to the bottleneck of the ml605 and of the current Avago transceiver the line data rate has been reduced to 2.4 Gbit/s.

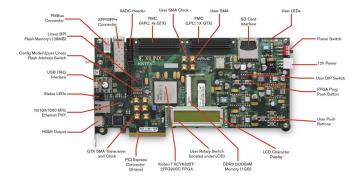

## The new board for developing

- To allow a test at full speed a new kc705 evaluation kit, based on Xilinx Kintex7 has been bought.

- A new transceiver running at 10 Gbit/s, from Finisar, is available to test the GBT-FPGA firmware on the Kintex.

## The test bench for the power rod

- A test for the DCDC power rod assembled with 88 channel is in progress, with load heat dissipation based on fans.

- To completion of the system, since the DCDC power rod is water cooled, a chiller and a pump are needed.

# The supply rack for power rod

- To provide the required current, a 19 inch rack has been almost filled with power supplies.

- The present solution with 24 power rods around the beam pipe should be carefully evaluated.

# Summary and outlook

#### Conlusion

- A board design for the GBT ASIC and VTRX transceiver was completed providing a solutions to facilitate the cooling.

- The fist prototype is expected for January with the aim to connect it to a Topix board.

- A GBT-FPGA implementation at 2.4 Gbit/s was completed; the next step will be the migration to Kintex7 at 4.8 Gbit/s.

- A test bench for the power rod with 88 channel is in progress, with the full current load and the water cooling system.

- At INFN no manpower was allocated to PANDA for 2016; each task could be only accomplished on a voluntary basis.