# PASTA Chip Status

#### Valentino Di Pietro and Alberto Riccardi

PANDA LII. Collaboration Meeting, Gießen March 2015

### Contents

#### PASTA Chip

- Requirements

- Building blocks

- Performance

- Back to December

- Updates

- Perspectives

# PANDA STrip ASIC

#### Specifications

- Event rate up to 40kHz

- Detector capacitance (15 - 25)pF

- Input charge (1 40)fC

• Linear time measurement with input charge

Goals

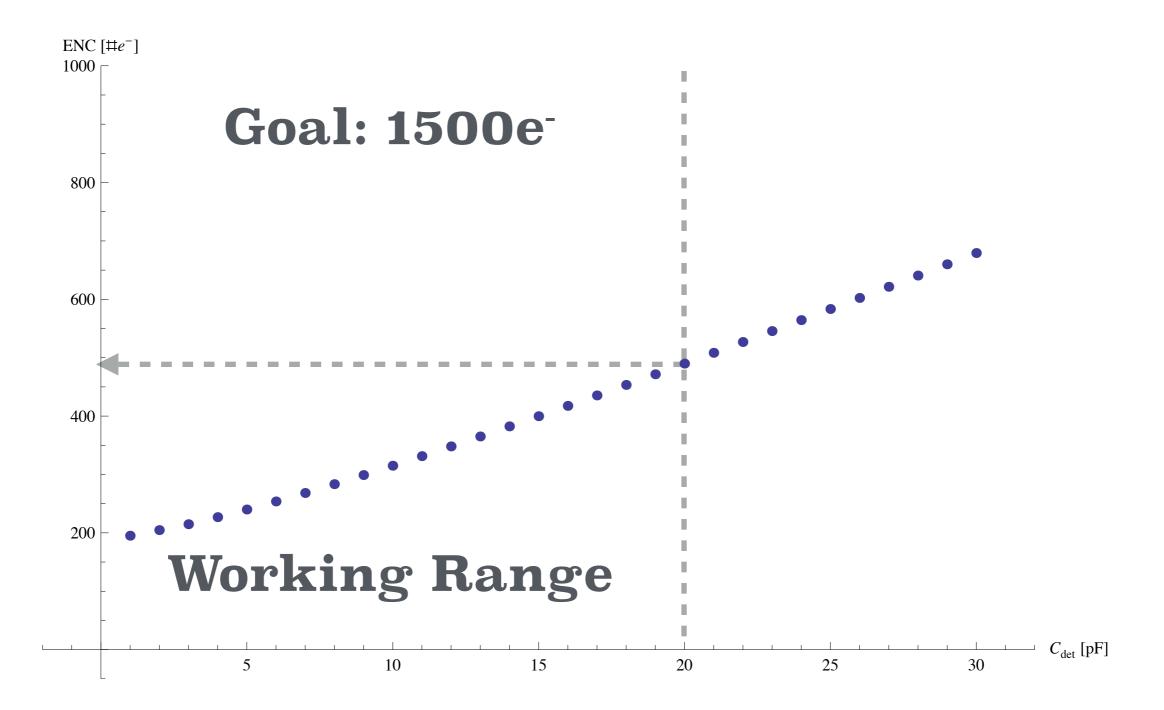

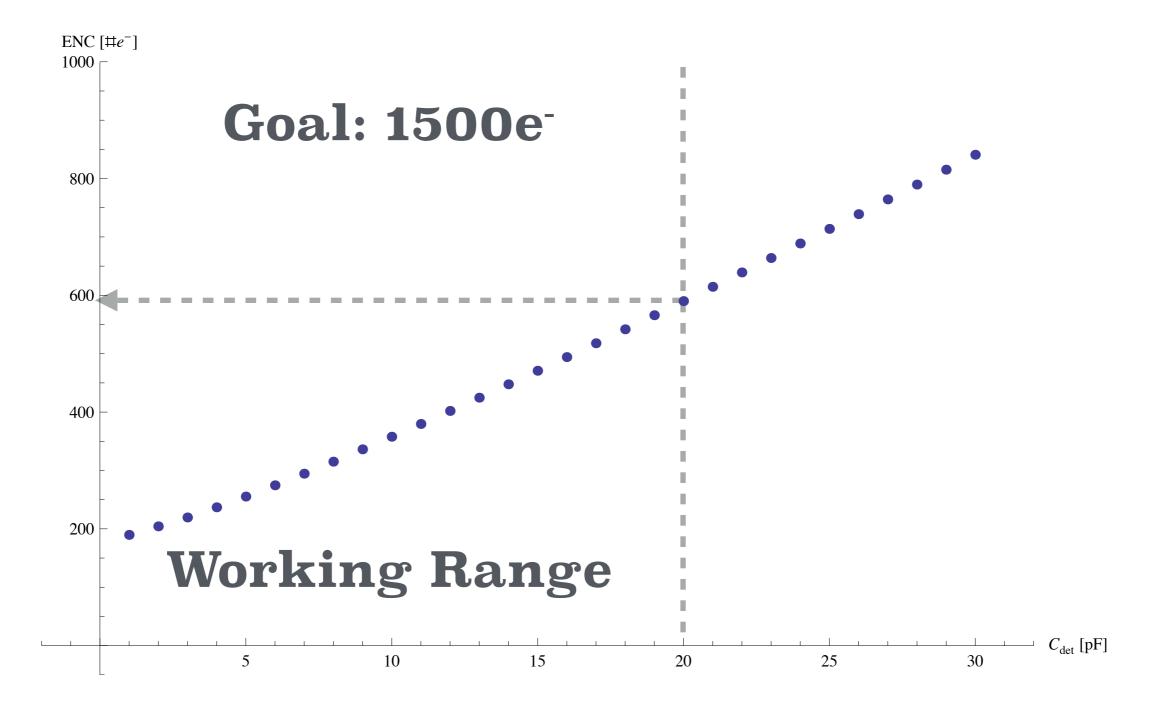

- Noise

< 1500 e<sup>-</sup>

- Power consumption

~ 4mW per channel

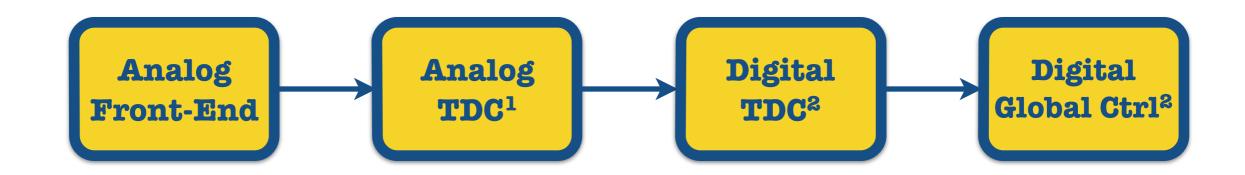

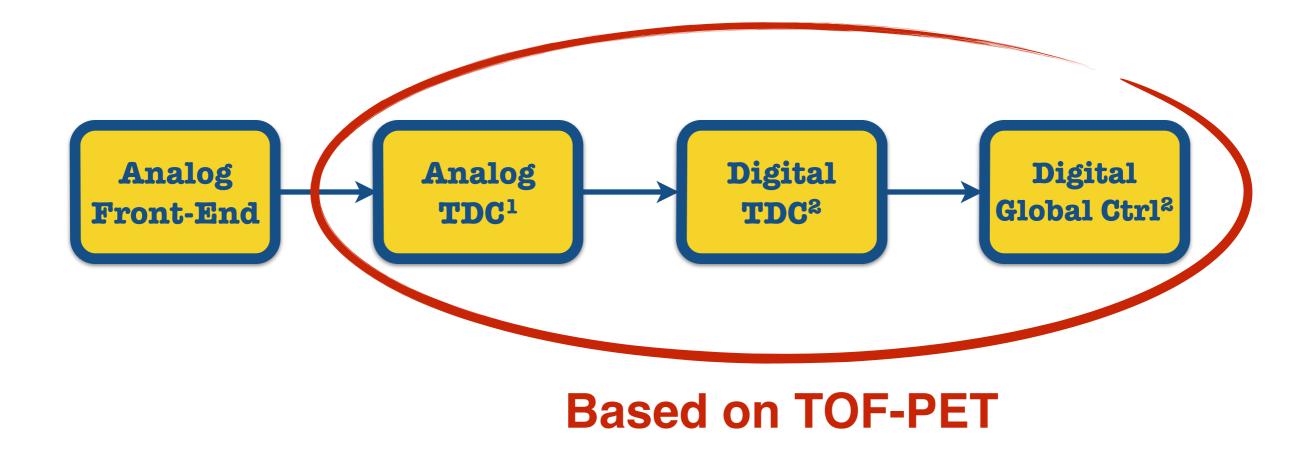

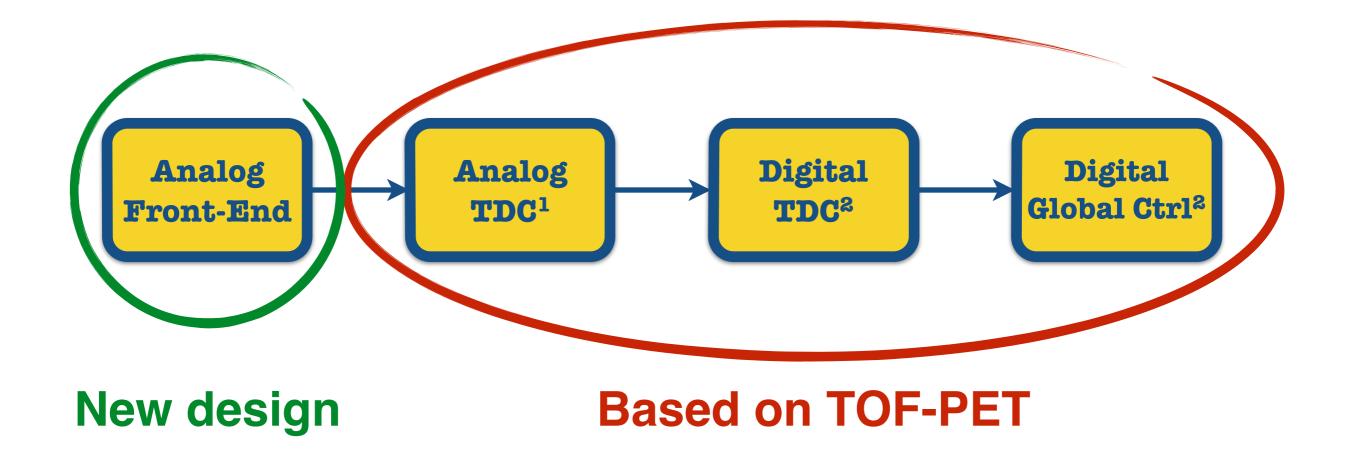

## PASTA Chip

1: Alberto Riccardi 2: André Goerres

## PASTA Chip

1: Alberto Riccardi 2: André Goerres

## PASTA Chip

1: Alberto Riccardi 2: André Goerres

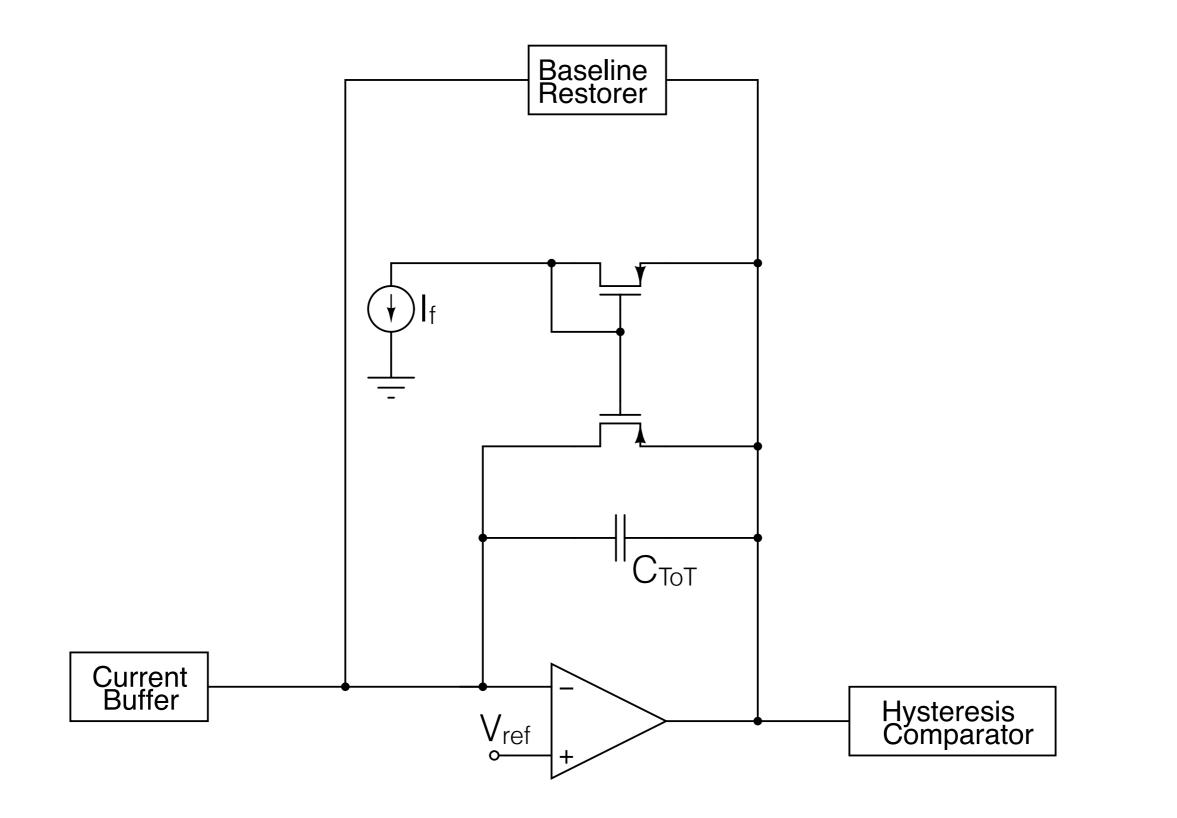

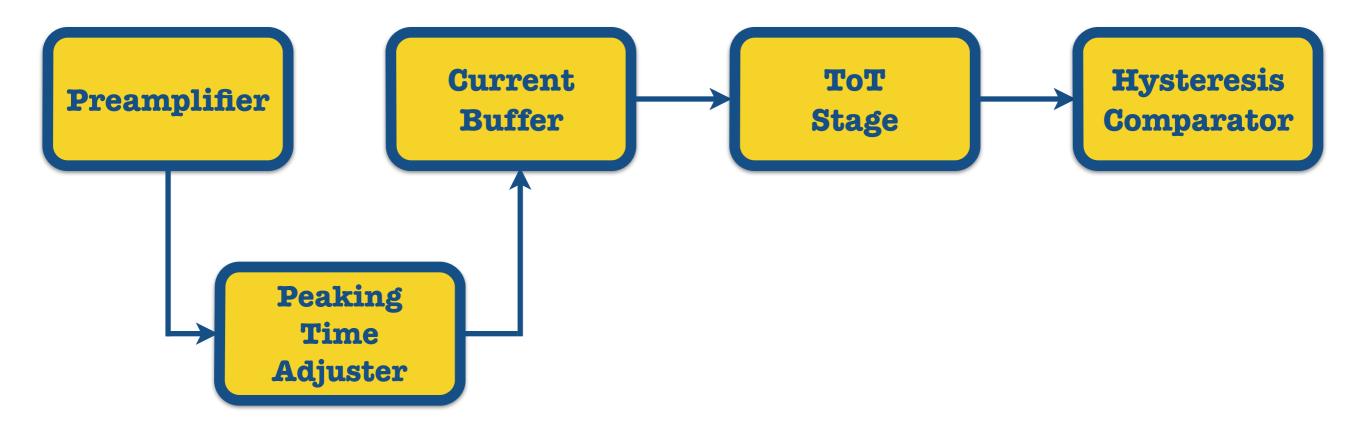

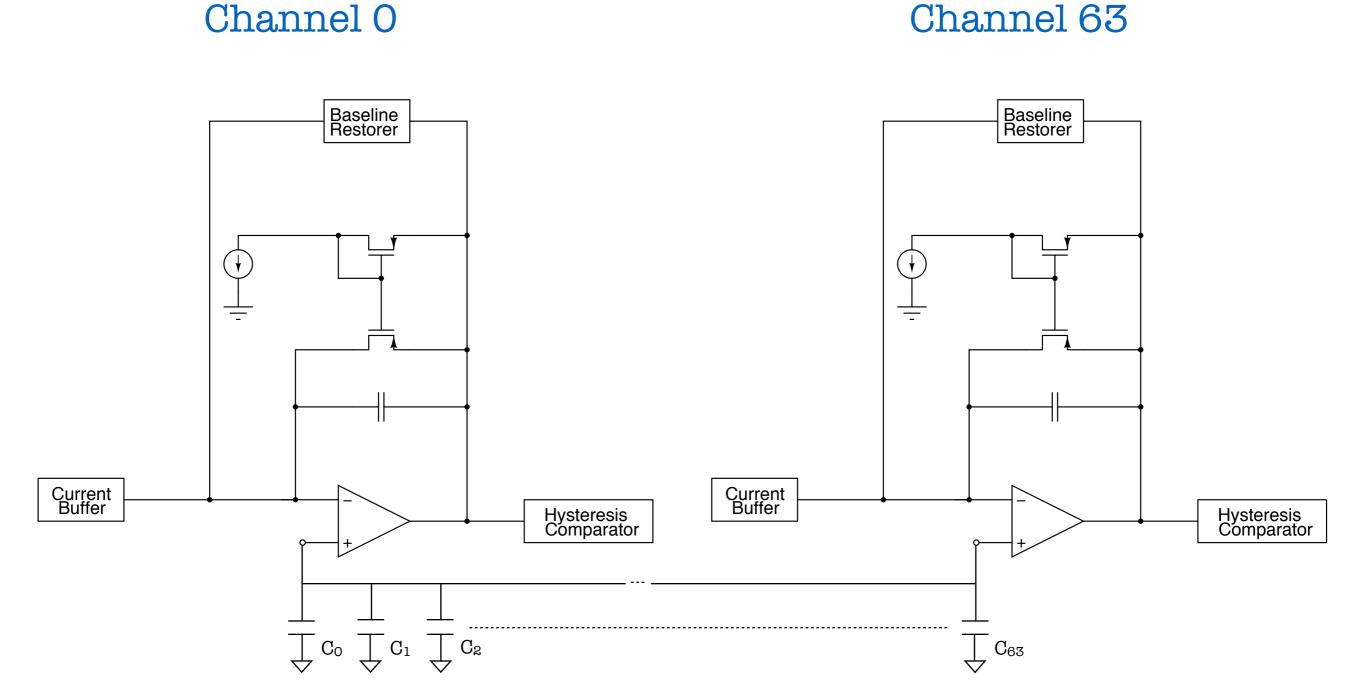

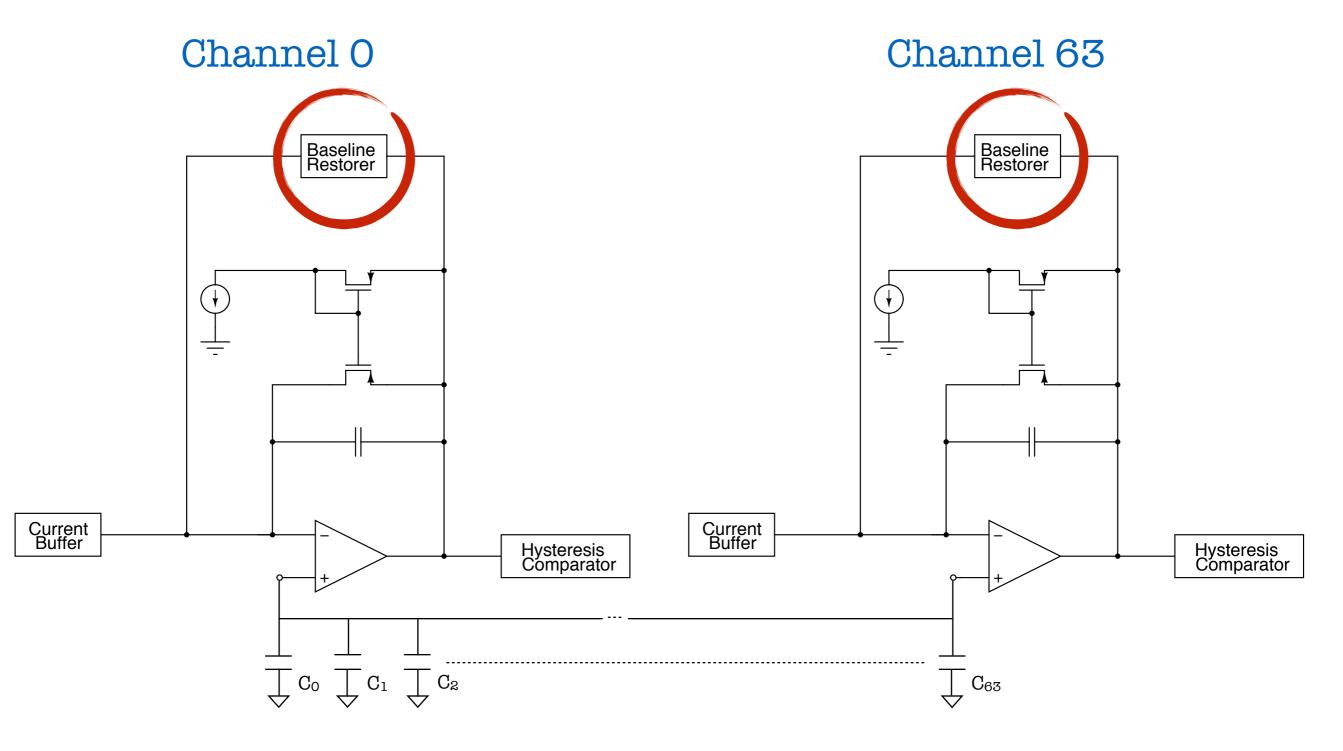

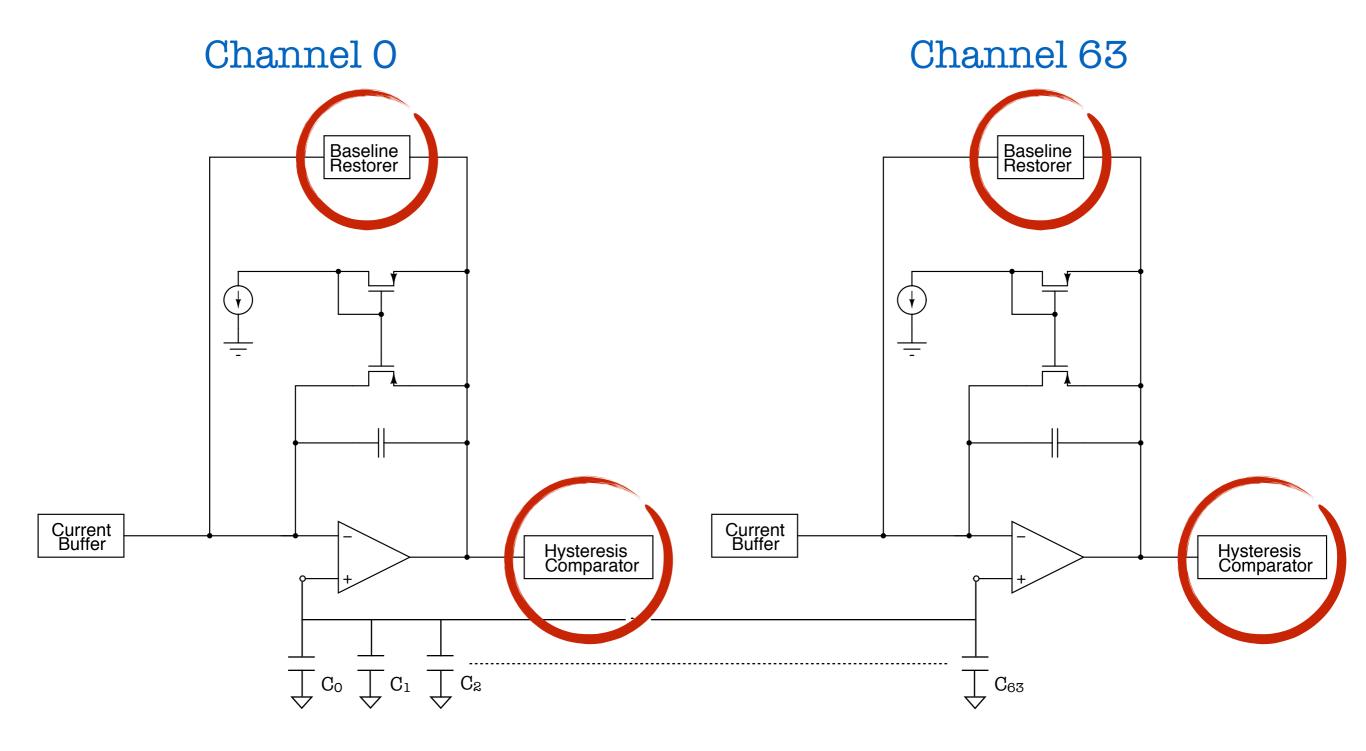

## PASTA Analog FE

$\sim 10 ns \rightarrow \sim 30 ns$

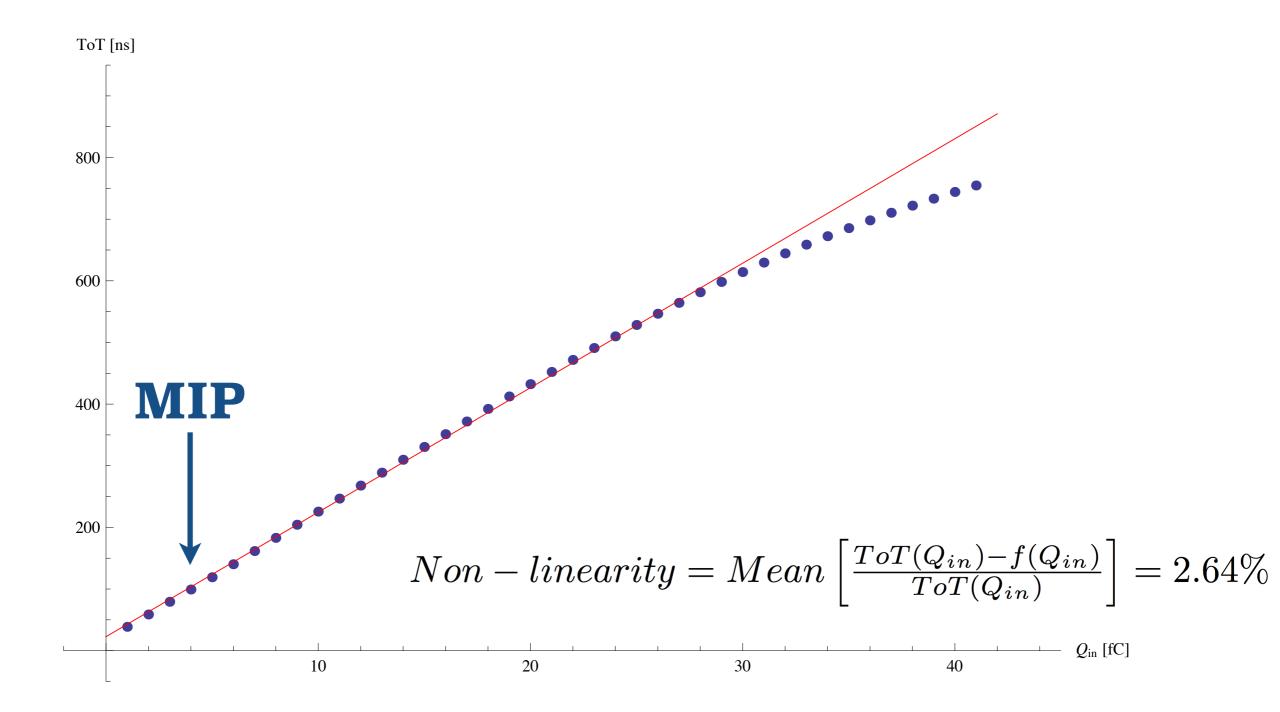

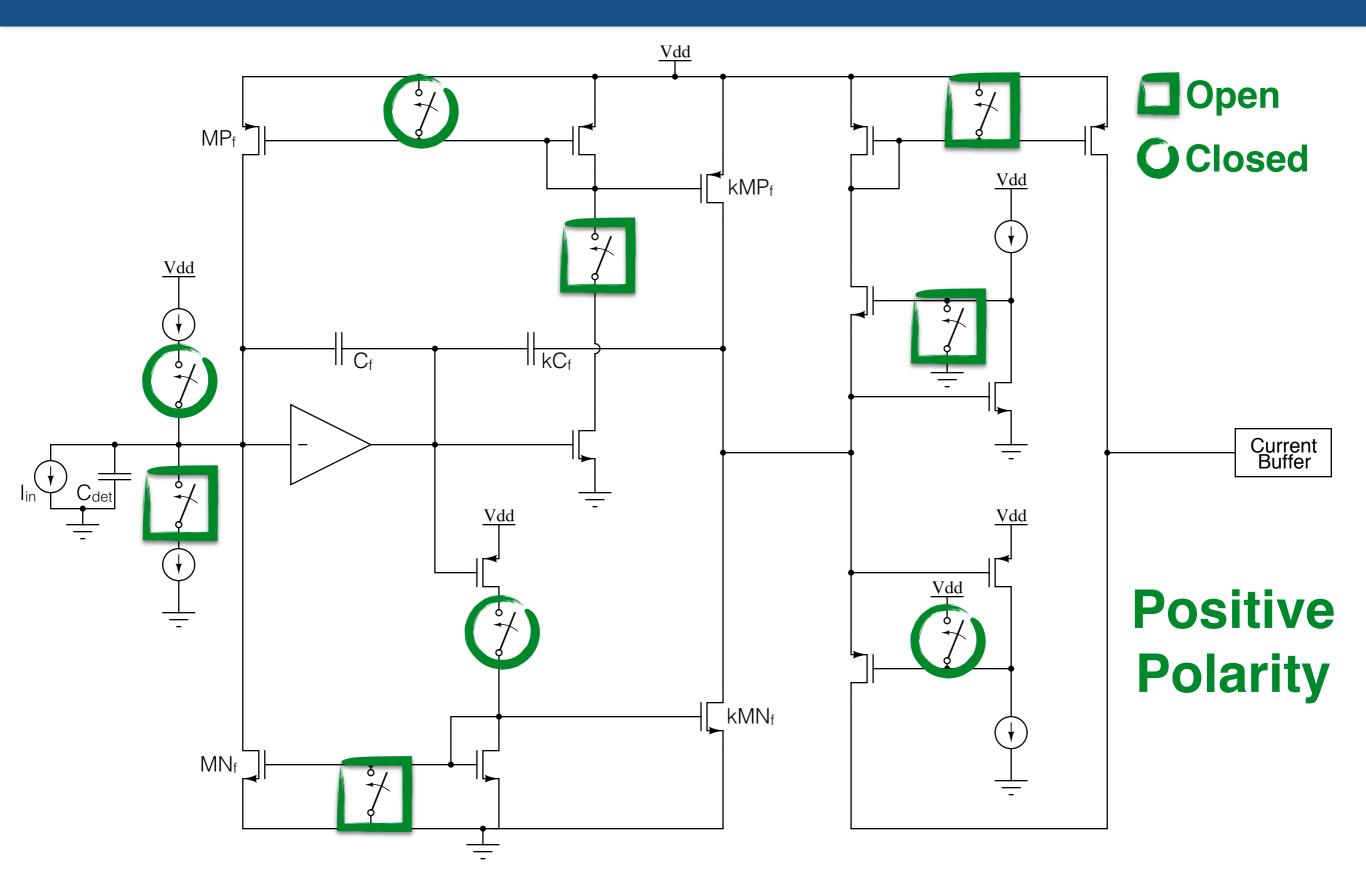

# pSconf\*: Linearity

\*pSconf: Configuration for the p-type Strips

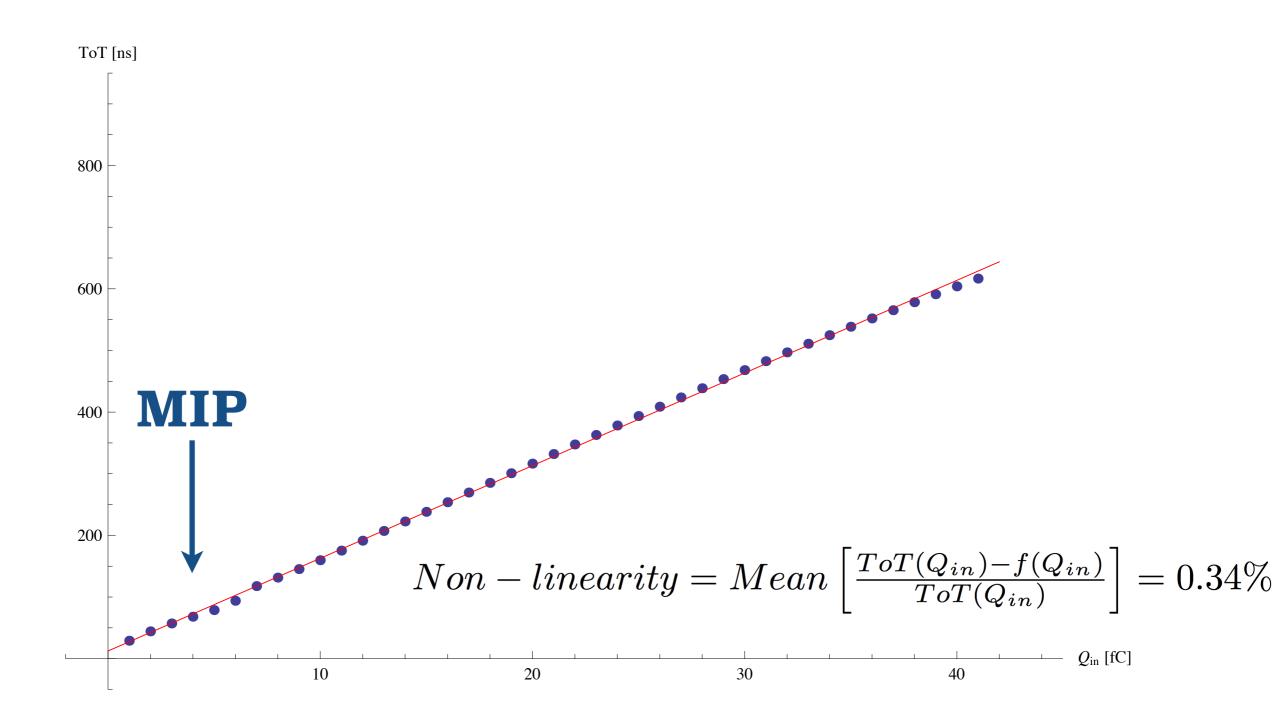

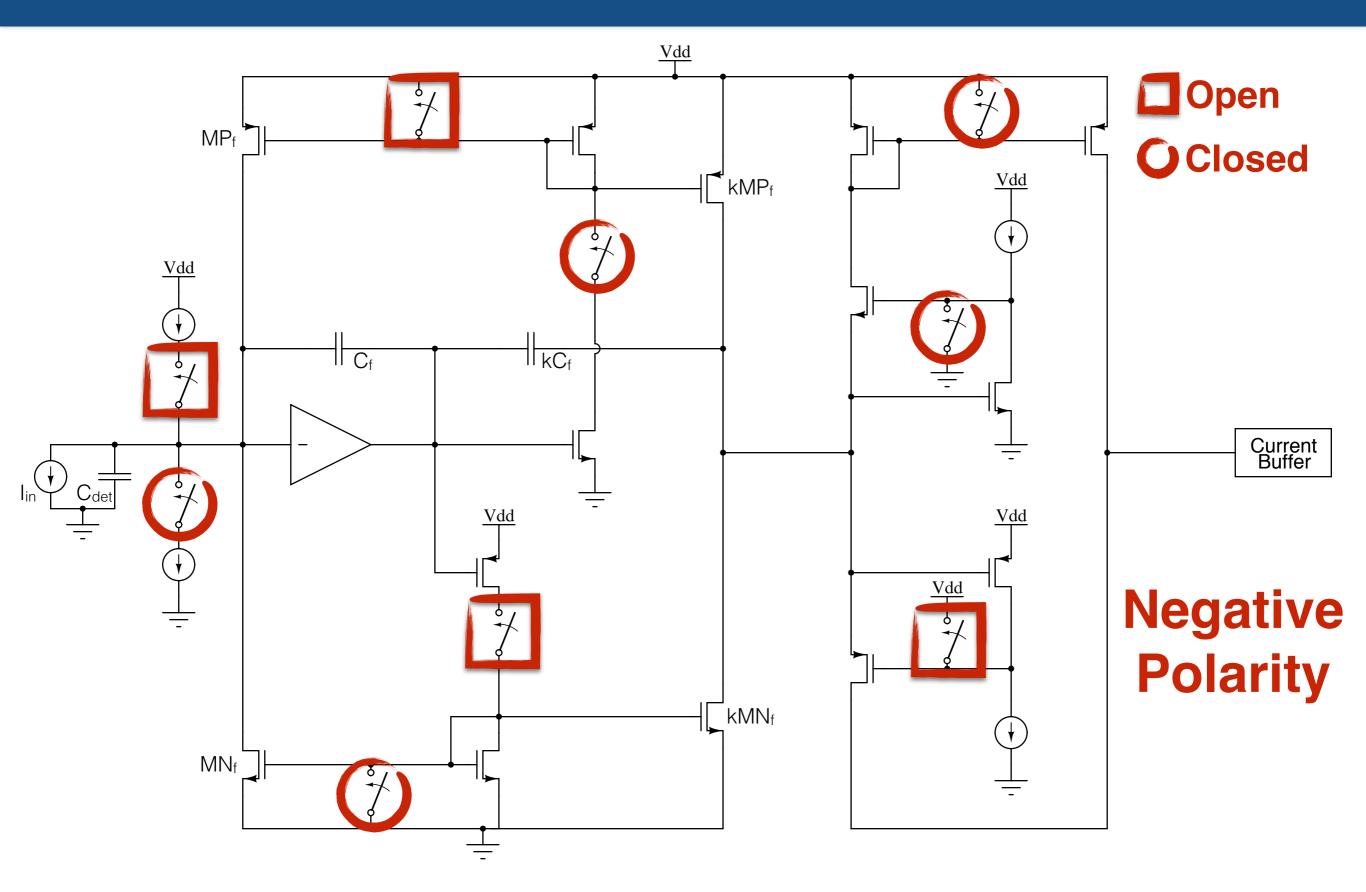

## nSconf\*: Linearity

\*nSconf: Configuration for the n-type Strips

### pSconf: ENC

### nSconf: ENC

## Back to December

- Layout completed with no PAD Ring

- GCTRL no DRC and LVS clean

- Post-integration and post-layout simulations started (FE + ATDC + TDC\_CTRL)

| Estimation for power consumption    |           |           |            |              |           |            |  |

|-------------------------------------|-----------|-----------|------------|--------------|-----------|------------|--|

|                                     | front-end | TDC       | TDC ctrl.  | global ctrl. |           | total      |  |

|                                     | 1 mW/ch   | 0.4 mW/ch | 0.25 mW/ch | 60 mW        | 4x 8.5 mW | 3.12 mW/ch |  |

| André Goerres, December 2014 update |           |           |            |              |           |            |  |

## Updates

- Layout completed with no PAD Ring

- GCTRL no DRC and LVS clean

- Post-integration and post-layout simulations started (FE + ATDC + TDC\_CTRL)

- PAD Ring DRC and LVS clean

- GCTRL DRC and LVS clean

- Simulations ongoing

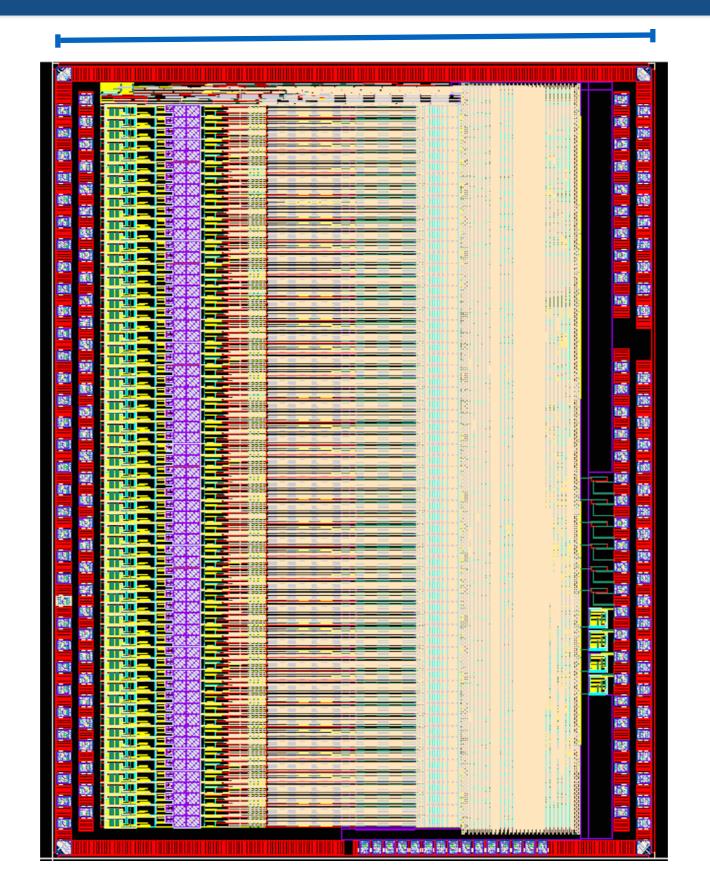

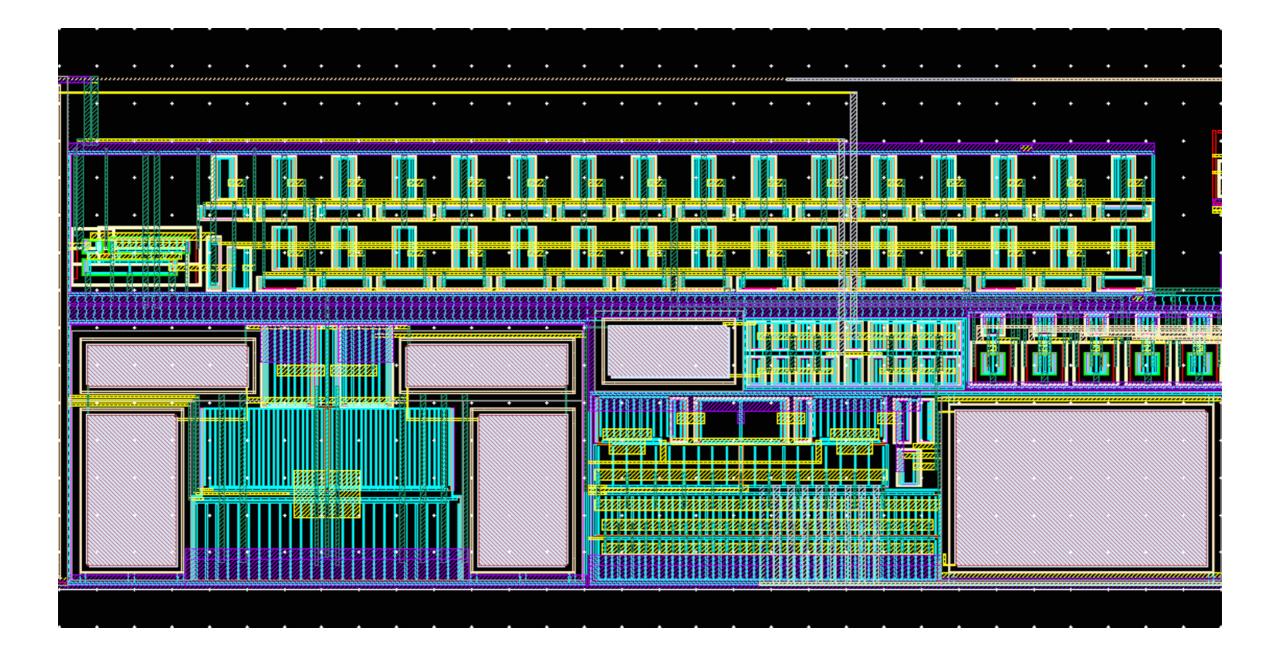

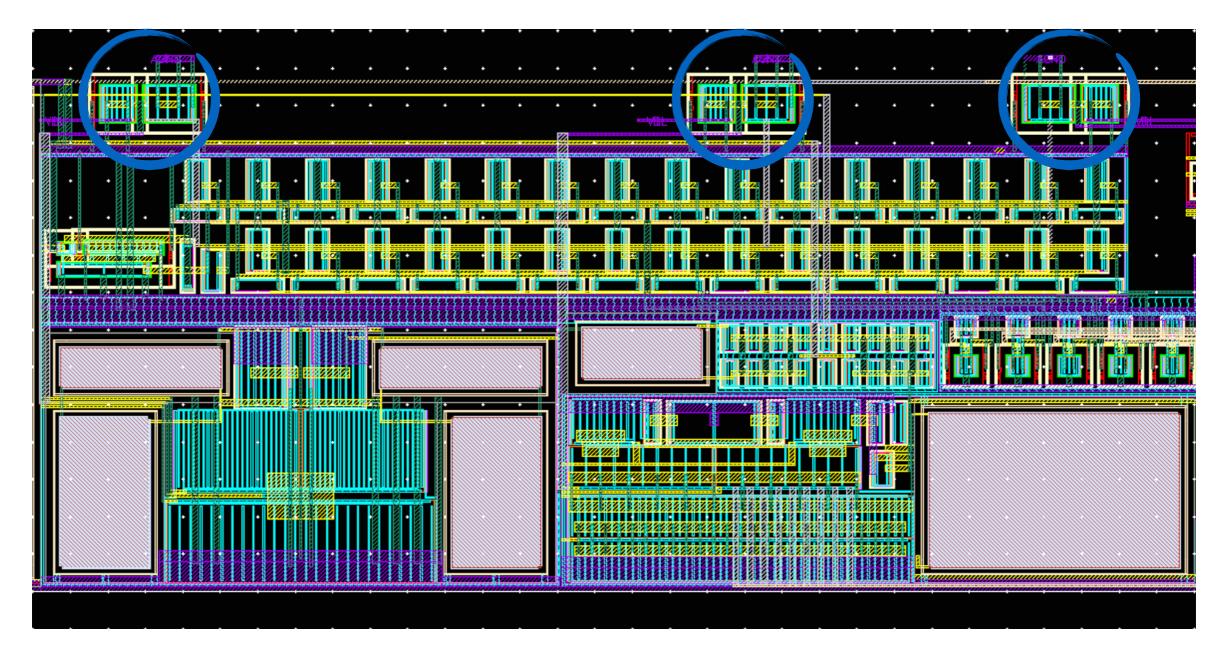

## Full Chip Layout

3.4mm

4.5mm

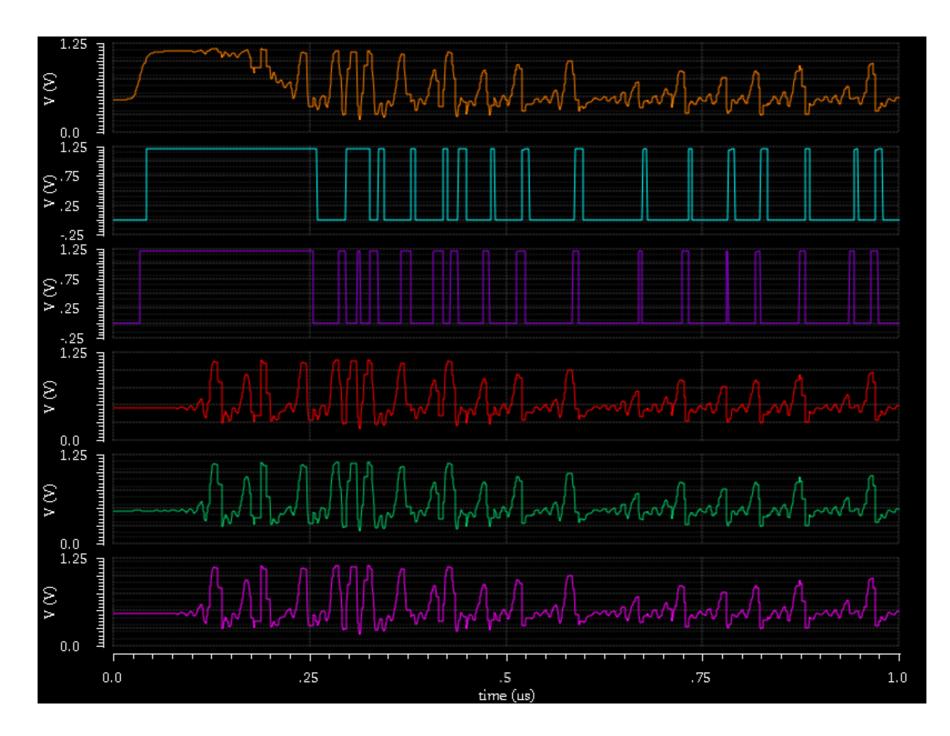

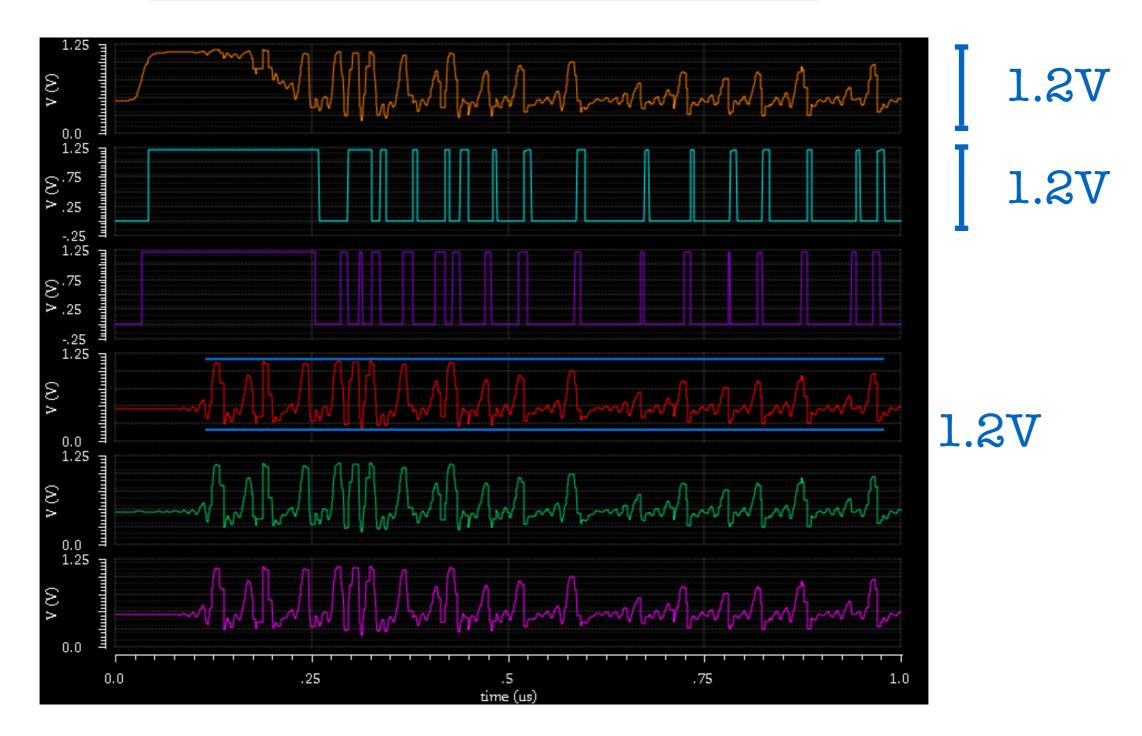

## Simulations

### Done

- 64 Channels + Bias (schematic)

- Full Analog Channel (post-layout)

- Antenna Check

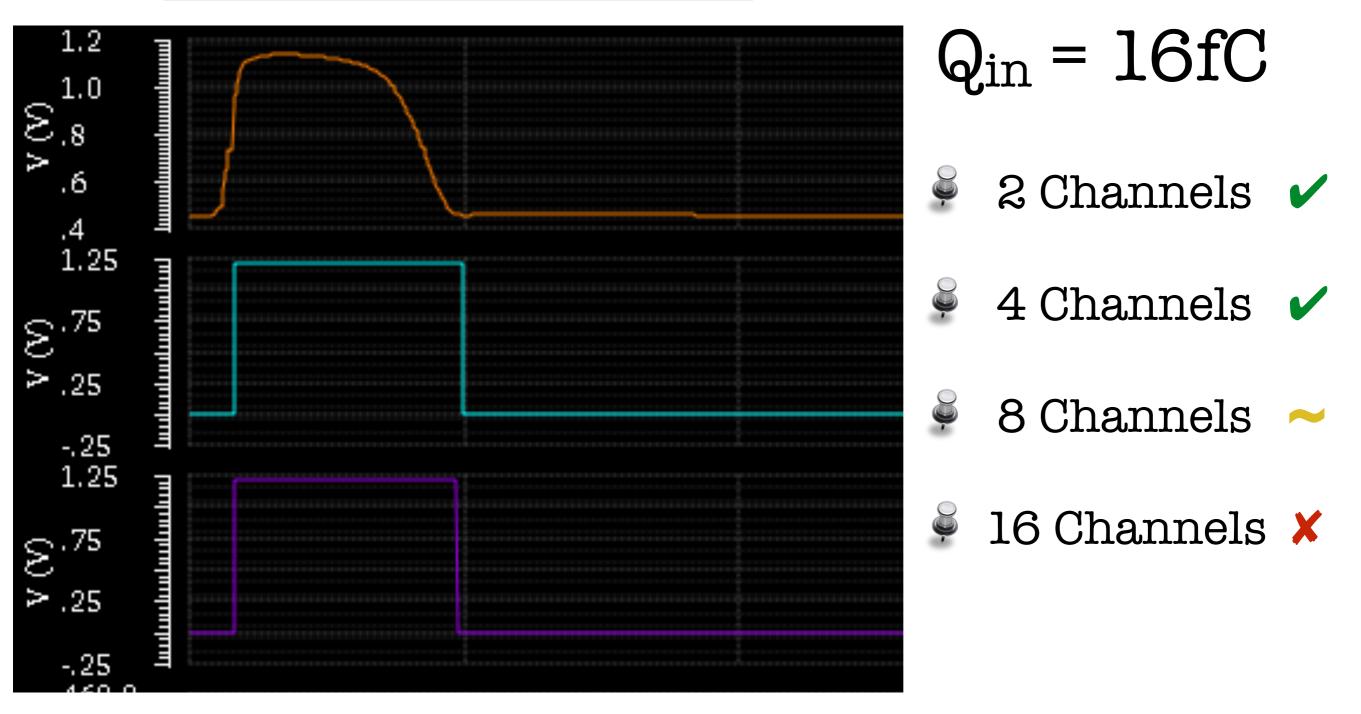

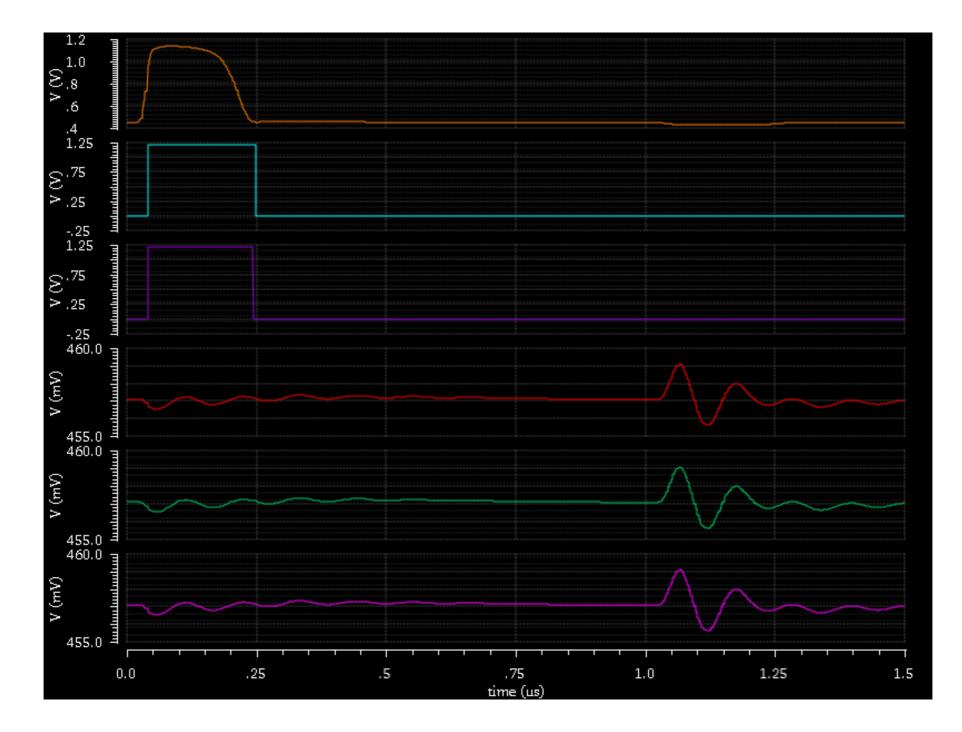

### **Post-integration Simulations**

### 1 Channel + Bias

### Results

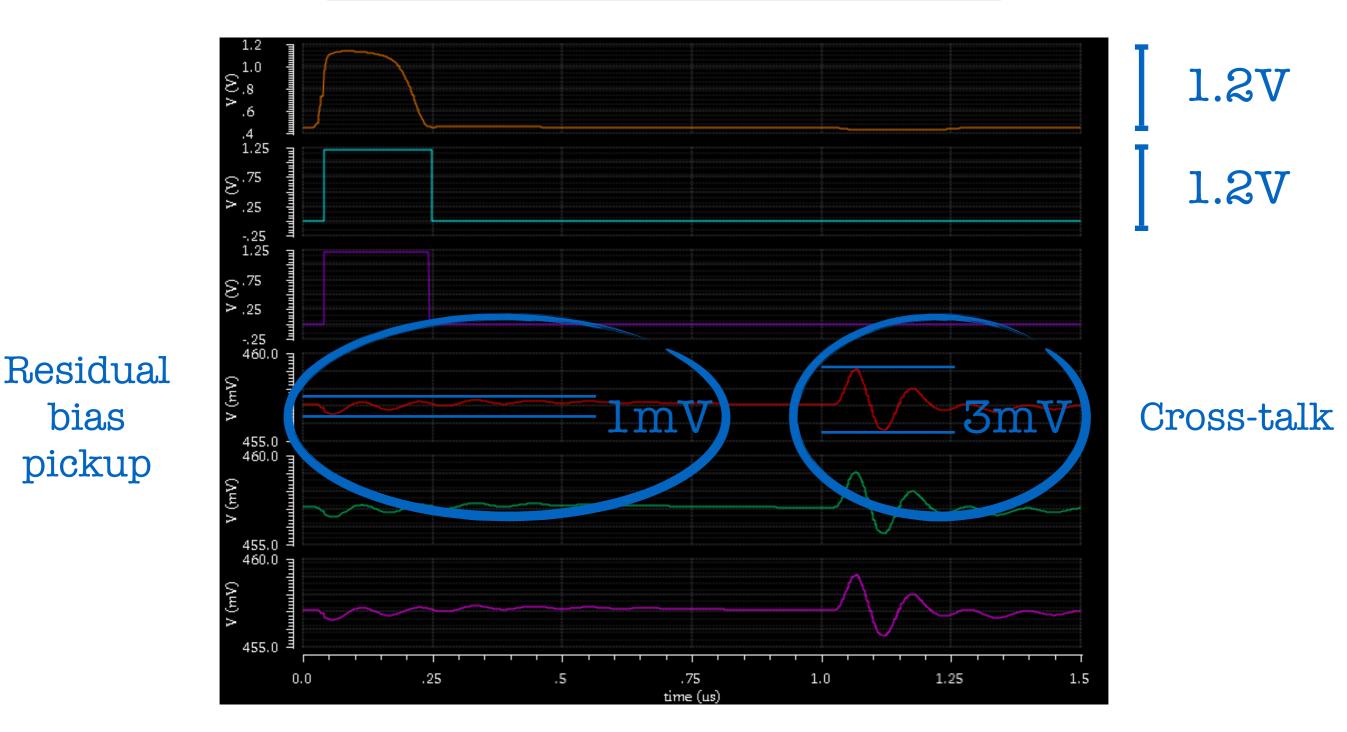

#### 16 Channels + Bias

### Results

#### 16 Channels + Bias

### Issue detected

### Issue detected

### Issue detected

# Results (post fixing)

#### 64 Channels + Bias

# Results (post fixing)

#### 64 Channels + Bias

### Before

#### After

#### Power consumption increased by $100\mu W$

### Simulations

### Planned checks

- PAD Ring + 64 Analog Channels + Bias (schematic)

- PAD Ring + 64 Analog Channels + Bias + Power Grid (post-layout dc analysis)

- Further refinement on channels decoupling

- TDC conversion (schematic) [to verify what seen in September]

## Perspectives

- Complete the fixing of the issues detected by postintegration simulations

- Implement the modifications into the layout

- Submit the project to the foundry on April  $20^{\text{th}}$

## Perspectives

- Complete the fixing of the issues detected by postintegration simulations

- Implement the modifications into the layout

- Submit the project to the foundry on April 20<sup>th</sup>

Special thanks to Angelo Rivetti and Manuel Rolo for the great help provided

## Perspectives

- Complete the fixing of the issues detected by postintegration simulations

- Implement the modifications into the layout

- Submit the project to the foundry on April 20<sup>th</sup>

# Backup Slides

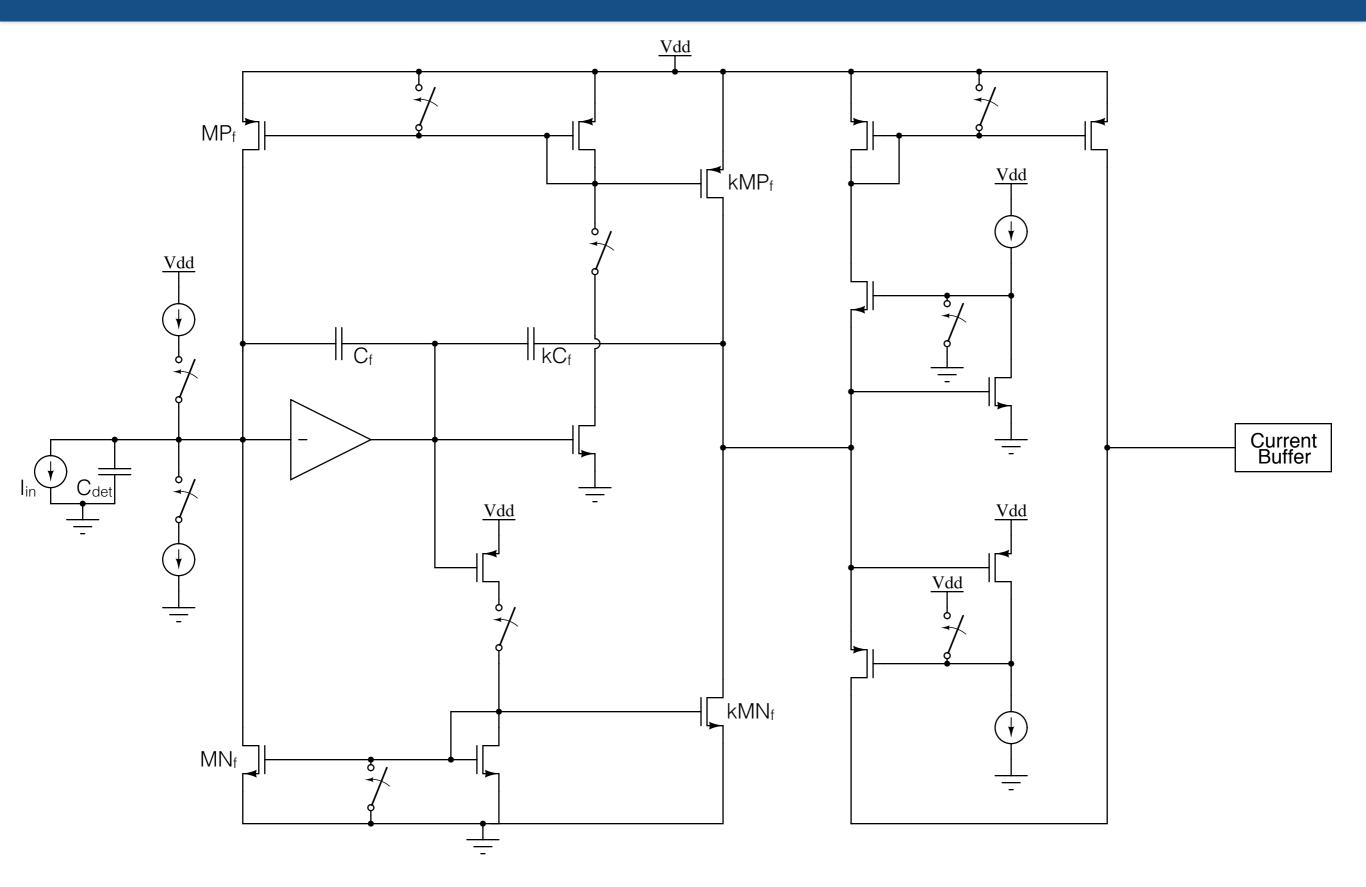

## Preamplifier

## Preamplifier

## Preamplifier

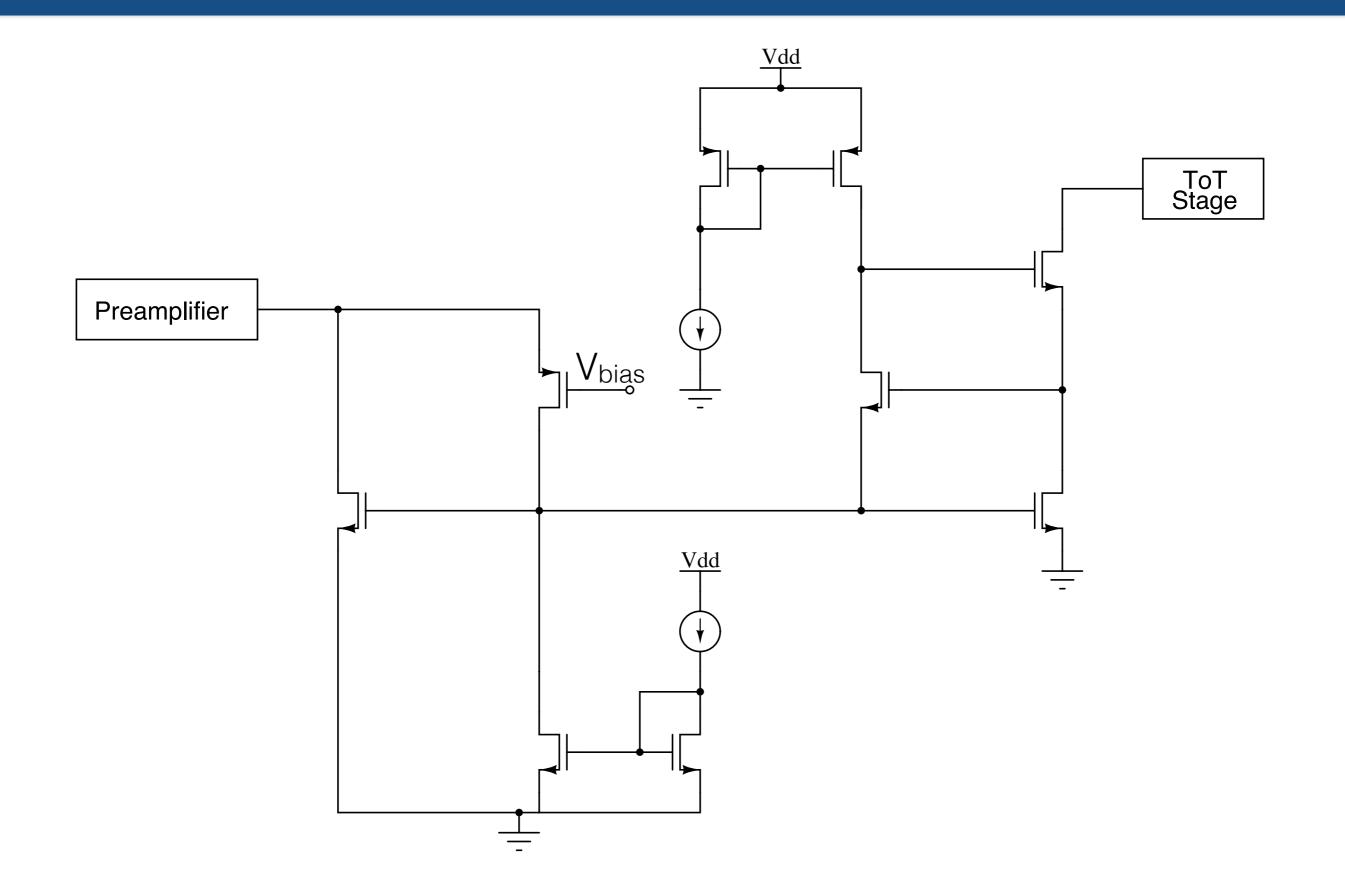

### Current Buffer

ToT Stage