#### First steps with the TOFPET ASIC

#### Lukas Gruber<sup>a,b</sup>

<sup>a</sup>Stefan Meyer Institute for Subatomic Physics, Vienna, Austria <sup>b</sup>GSI Helmholtz Centre for Heavy Ion Research, Darmstadt, Germany

PANDA TOF meeting March 17, 2015

Paul Bühler<sup>a</sup>, Johann Marton<sup>a</sup>, Herbert Orth<sup>b</sup>, Carsten Schwarz<sup>b</sup>, Dominik Steinschaden<sup>a</sup>, Ken Suzuki<sup>a</sup>

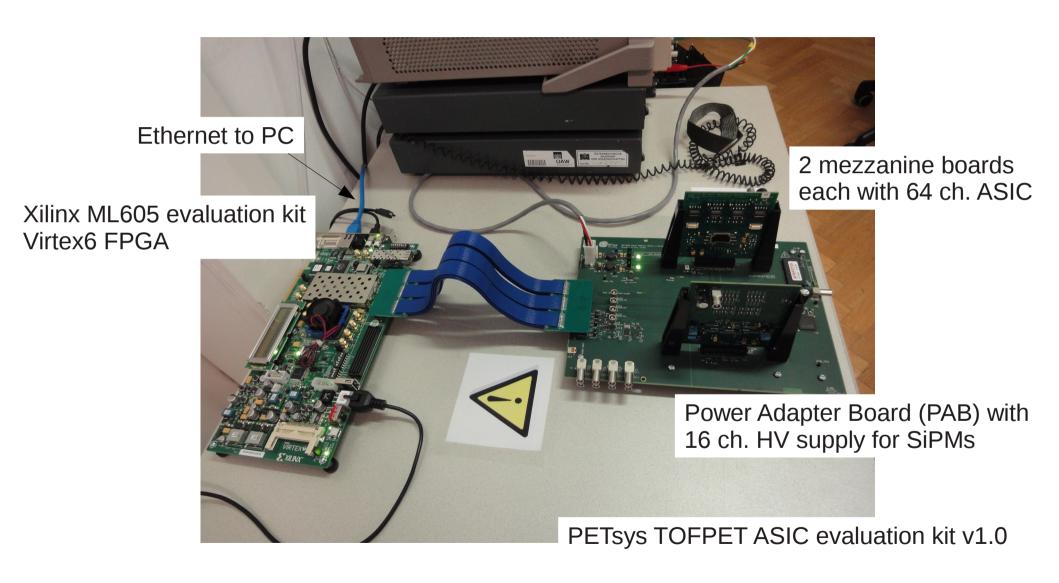

#### **Evaluation kit**

### First steps

- Documentation, firmware, demo programs, etc. provided by PETsys (GoogleDrive)

- Getting started with test routines and calibration

- Test functionality of ML605 board running a Build-In System Test

- Check the communication between the two boards (FPGA and TOFPET) by testing clock and HV

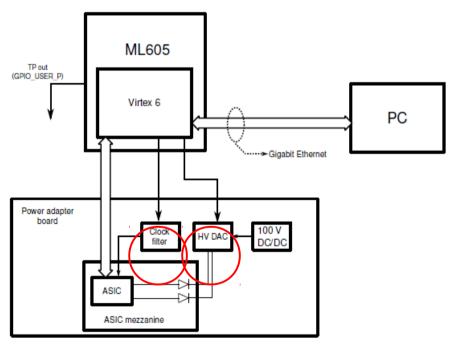

Figure 1.1: System diagram

TOFPET ASIC evaluation kit software user guide v3.1, PETsys, March 2015

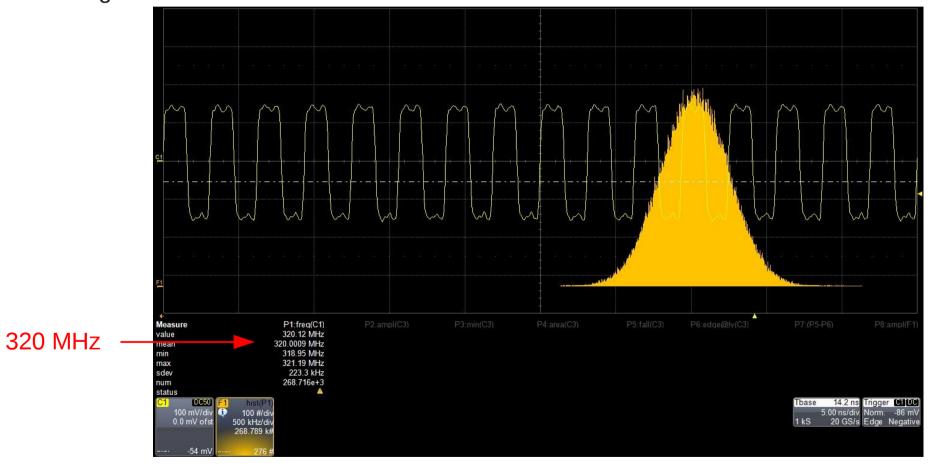

### 320 MHz clock

The PAB should receive a 320 MHz clock from the FPGA Clock signal measured at the PAB:

→ Communication between FPGA and TOFPET works

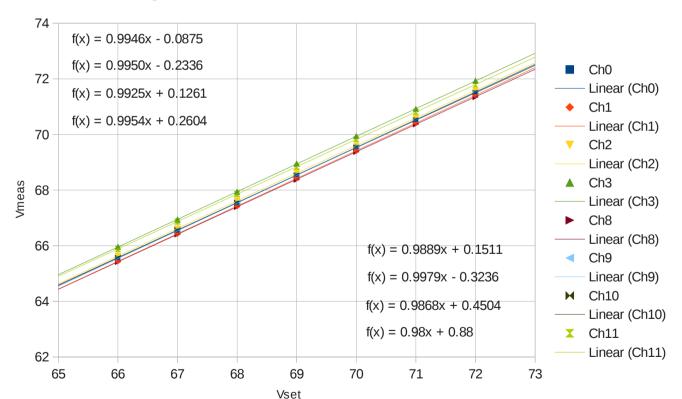

## HV supply

- The PAB has an internal HV supply module which can be controlled via the FPGA

- The HV DAC has to be calibrated by comparing the set voltage ( $V_{set}$ ) and the actual voltage ( $V_{meas}$ ) at the output of the mezzanine bords

- Shows again that communication works

Simple linear regression:

$$V_{\text{meas}} = m \times V_{\text{set}} + b$$

Parameters m,b are used to produce a calibration file and calibrate the HV DAC.

### Current work and next steps

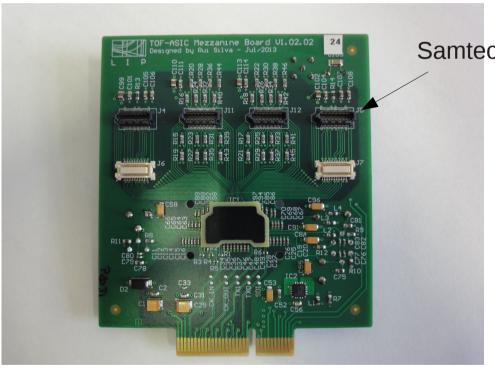

- The mezzanine board connects to 4 Hamamatsu 16 channel arrays

- We need an adapter to connect single SiPMs

Samtec SS4 connector fits to ST4

We will prepare a printboard with ST4 on one side and connectors for SiPMs on the other side.

Next steps: read-out SiPM signals, determine time resolution, attach scintillator tile

# Thank you!