#### AFCK - Hardware and Software

#### Wojciech M. Zabołotny

#### Institute of Electronic Systems, Warsaw University of Technology

(significantly based on materials provided by other members of CBM team)

PANDA DAQT-FEE Workshop 9.04.2015

## Why AFCK?

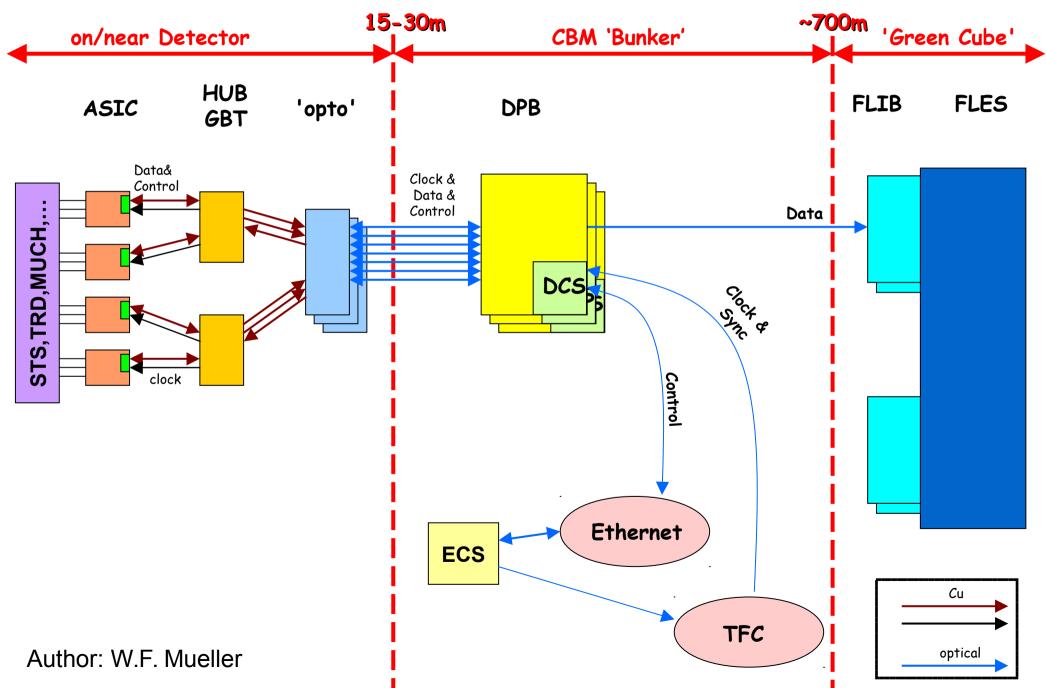

- There was a need for a prototyping platform for DPB boards for CBM experiments

- What are requirements for the DPB boards?

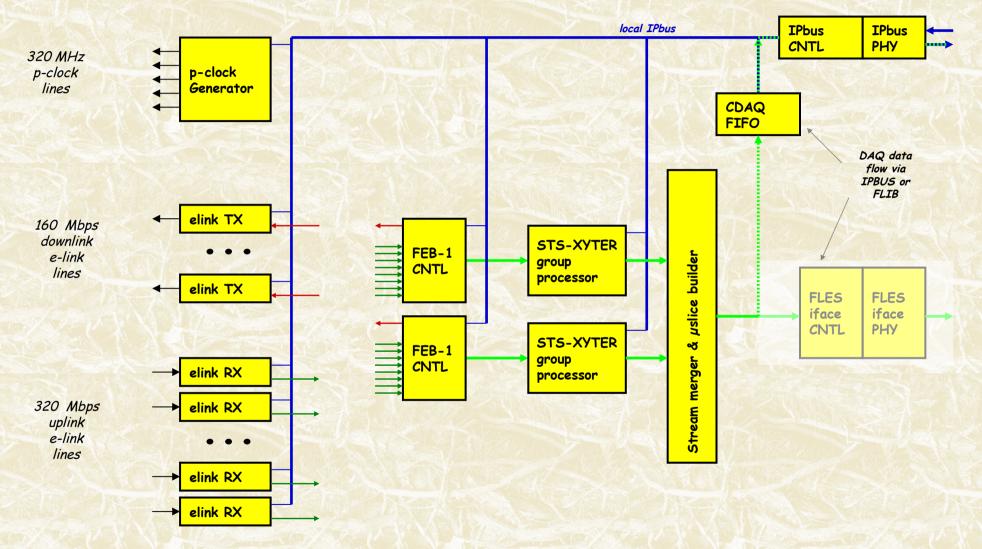

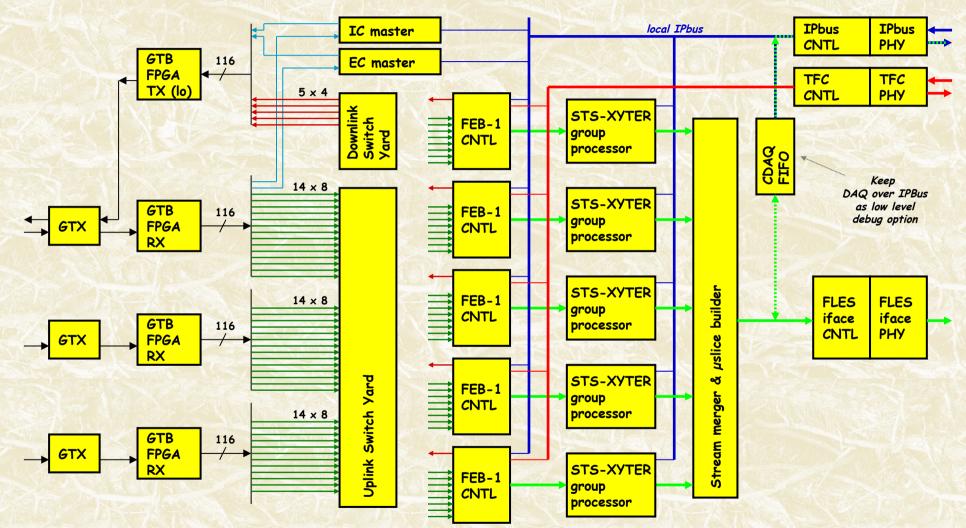

- The Data Processing Boards are intended to be an important component of the CBM readout chain and control system

- They should concentrate and possibly preprocess data received from the front-end electronics, before sending them via long optical links to FLES

- They should provide control (both fast and slow) for FE electronics

- They should distribute reference clock and timing to the FE electronics

#### CBM Data Flow (ASIC based FEE)

#### Requirements for DPB boards

- The Data Processing Boards are intended to be an important component of the CBM readout chain and control system

- They should concentrate and possibly preprocess data received from the front-end electronics, before sending them via long optical links to FLES

- They should provide control (both fast and slow) for FE electronics

- They should distribute reference clock and timing to the FE electronics

- From the above requirements we can see, that the DPB boards should provide quite complex communication capabilities

- For prototyping we needed versatile board, allowing to check and verify different concepts, related to possible solutions of communication interfaces and associated firmware

#### MTCA.4 (for Physics) as DPB platform

- Micro TCA Carrier Hub 1 (MCH1) with clocking, Ethernet switch is standard interface.

- 12x custom AMC with FPGA and 6 QSFP optical transceivers. On mid-height AMC.0 doublewidth board, one can fit 24 + 8 optical links into it. Optionally, one of AMC implements WR core and acts as a timing source. 8 GTX ports are routed to the RTM connector.

- Rear Transition Module (RTM) can be used to further extend number of optical links

- JTAG Switch Module. Used to communicate between MCH1, MCH2 and 12 AMCs for remote debugging (chipscope) and FPGA upgrade

- MCH2 optional, redundant carrier hub with White Rabbit switch, crosspoint switch, low jitter clock distribution circuit and JTAG master port. WR management port can be connected to the general Ethernet network

- Optional AMC with 5 White Rabbit ports (SFPs). In this configuration, the crate may also perform function of WR switch

- MTCA.4, 8U crate with JTAG module (JSM), redundant power supply module and dual fan tray. VT811 from Vadatech is recommended.

- Optional AMC CPU with x86 Intel processor, connected do all AMCs using PCIe interface via MCH PCIe switch

- Optional RTM modules with SFP+ or QSFP connectors

#### Existing AFC board

- There was existing Open Hardware AMC FMC Carrier (AFC) board

- Artix based, flexible board in MTCA standard

- After replacement of Artix FPGA with bigger and faster Kintex, and adding even more flexible clocking and communication functionalities it was converted to AFCK, which may be used for development of DPB

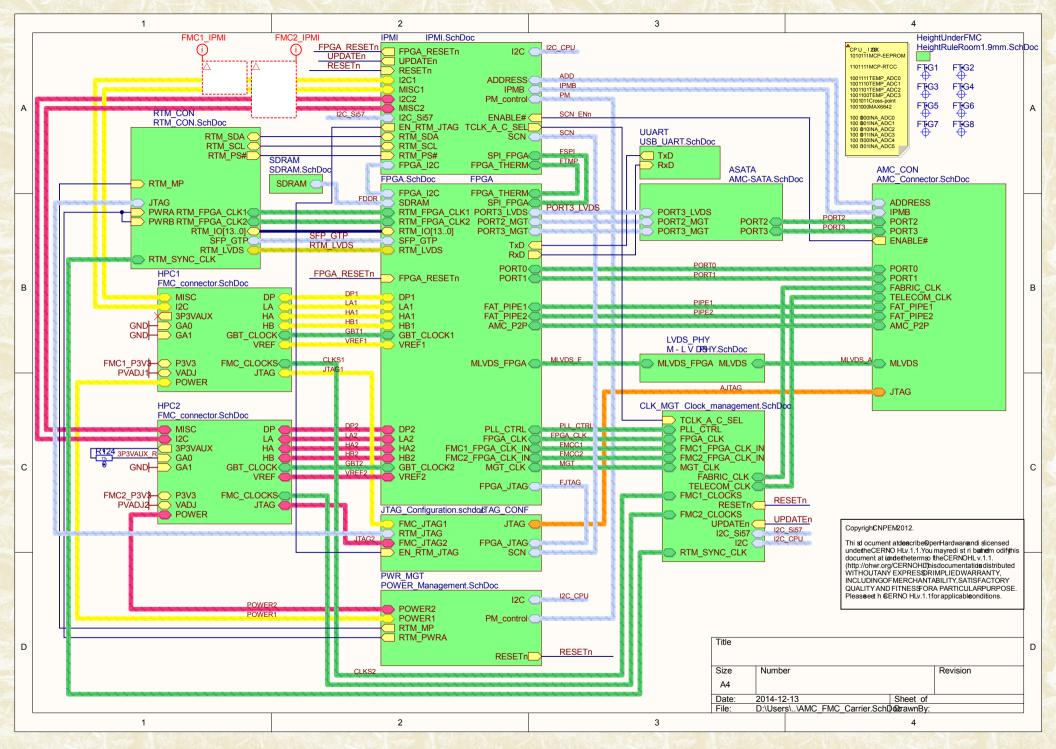

#### AFCK board

- Available as Open Hardware solution on OHWR website

- Ready to work in the MTCA crate, but usable also in stand alone mode

- This is a prototyping platform, not a final DPB solution!

#### Programmable resources

- Module Management Controller (MMC) -LPC1764FBD100 - software may be modified by the user

- Xilinx Kintex 7 325T FFG900 FPGA

- 326080 logic cells (50950 slices)

- 840 DSP slices

- 890 1kb BRAMs, 10 CMTs, 1 PCIe, 16 GTX

#### Memory resources

- 2 GB(16 Gb) of DDR3 SDRAM with 32-bit interface and 800 MHz clock - for huge amount of data requiring relatively slow access

- SPI Flash for FPGA configuration (accessible from MMC)

- SPI Flash for user data storage

- EEPROM with MAC and unique board ID

- 16020 kb of data in FPGAs BRAMs for data requiring high speed parallel access

# High speed communication capabilities

- 2 HPC connectors for 2 single width FMC or one dual width FMC

- Up to 4 GTXs may be routed to each FMC

- In the prototype: GTXs in FMC1 are proven to work at 10 Gbps, while GTXs in FMC2 up to 5 Gbps (in next revision higher speed in FMC2 should be achievable)

- GTXs available in FMC connectors may be optionally routed to the RTM connector

- Another 8 GTX transceivers are available at AMC FP ports (in MTCA backplane)

#### Examples of Ethernet connectivity

- FMC board with SFP+ cages (there are COTS boards with 4 SFP+ cages)

- Connection to the standard MTCA backplane - Ethernet lines or Ext. FP lines

- Connection to the mounted SATA connector (and further via COTS or self made SATA ↔ SFP adapter)

#### Other connectivity functions

- Mini USB connector connected to MMC

- Mini USB with UART converter connected either to FPGA or to MMC

- SATA connector connected to AMC PORT 2 and 3, which may be routed to FPGA GTX

#### Flexible clocking

- Why do we need flexible clocking?

- Different clock domains:

- GBT-FPGA 120MHz or 40MHz

- 1 Gbps Ethernet/WR 125 MHz

- 10 Gbps Ethernet 156.25 MHz

- Clock distribution circuit compatible with White Rabbit

- Based on CDCM61004RHBT and Si57X

- Jitter cleaner allowing to use clock recovered from GTX receiver to drive GTX transmitter

- Clock crossbar with 16 inputs and 16 outputs

|                                              | IC8B         |

|----------------------------------------------|--------------|

| FMC2_CLK3_BIDIR_C_P 2                        | IP0          |

| FMC2_CLK3_BIDIR_C_N3                         | IN0          |

| FMC2_CLK1_M2C_C_P_5                          |              |

| FMC2_CLK1_M2C_C_N_6                          | IPI<br>INI   |

|                                              | 1191         |

| FMC2 CLK0 M2C C P 8<br>FMC2 CLK0 M2C C N 9   | IP2          |

| FMC2_CLK0_M2C_C_N_9                          | IN2          |

| FMC2 CLK2 BIDIR C PI1                        | IP3          |

| FMC2_CLK2_BIDIR_C_N2                         | IP3<br>IN3   |

| TCLKD CDL N                                  | 110          |

| TCLKB_CIN_N 14<br>TCLKB_CIN_P 15             | IP4          |

|                                              | IN4          |

| TCLKA_CIN_N 17                               | IP5          |

| TCLKA_CIN_P 18                               | IN5          |

| TCLKC CIN N 20                               |              |

| TCLKC CIN P 21                               | IP6          |

|                                              | IN6          |

| TCLKD_CIN_N 23                               | IP7          |

| TCLKD CIN P 24                               | IN7          |

| FCLKA_C_P 52                                 |              |

| FCLKA_C_N 53                                 | IP8          |

|                                              | IN8          |

| FMC1 CLK3 BIDIR C 155                        | IP9          |

| FMC1_CLK3_BIDIR_C_N6                         | IN9          |

| FMC1 CLK1 M2C C P 58                         | 1010         |

| FMC1_CLK1_M2C_C_N 59                         | IP10<br>IN10 |

|                                              |              |

| FMC1_CLK0_M2C_C_P_61<br>FMC1_CLK0_M2C_C_N_62 | IPII         |

|                                              | IN11         |

| FMC1 CLK2 BIDIR C R64                        | IP12         |

| FMC1_CLK2_BIDIR_C_N65                        | IN12         |

| WR PLL CLK1 C P 67.                          |              |

| WR_PLL_CLK1_C_N 68                           | IP13<br>IN13 |

|                                              | 11813        |

| CLK20_VCXO_C_P 70<br>CLK20_VCXO_C_N 71       | IP14         |

| CLK20_VCK0_C_N /I                            | IN14         |

| SI57X_CLK_C_N 73                             | IP15         |

| SI57X_CLK_C_P 74                             | IN15         |

|                                              | ADN4604ASVZ  |

|                                              |              |

| 0.00       | 27     | TCLKD COUT P                 |

|------------|--------|------------------------------|

| OP0<br>ON0 | 28     | TCLKD COUT N                 |

| ONU        |        |                              |

| OP1        | 30     | TCLKC_COUT_P                 |

| ONI        | 31     | TCLKC_COUT_N                 |

| UNI        | -      |                              |

| OP2        | 33     | TCLKA_COUT_P                 |

| ON2        | 34     | TCLKA_COUT_N                 |

| 0.12       |        |                              |

| OP3        | 36     | TCLKB_COUT_P                 |

| ON3        | 37     | TCLKB_COUT_N                 |

|            | 20     | TROL OF MILLOR               |

| OP4        | 39     | FPGA_CLK1_C_P                |

| ON4        | 40     | FPGA_CLK1_C_N                |

|            | 42     | EP2 CLV2 C P                 |

| OP5        | 42     | FP2_CLK2_C_P<br>FP2_CLK2_C_N |

| ON5        | > +3   | FP2_CLK2_C_N                 |

|            | 45     | LINK01 CLK P                 |

| OP6        | 46     | LINK01 CLK N                 |

| ON6        |        | CHINKOI_CER_N                |

|            | 48     | FP2 CLKL C P                 |

| OP7        | 49     | FP2_CLK1_C_P<br>FP2_CLK1_C_N |

| ON7        |        |                              |

| ODO        | 77     | PCIE_CLK1_C_P                |

| OP8        | 78     | PCIE CLKI C N                |

| ON8        |        |                              |

| OP9        | 80     | LINK23 CLK_P                 |

| ON9        | 81     | LINK23 CLK_N                 |

| 0149       | -      |                              |

| OP10       | 83     | FIN1_CLK3_P                  |

| ON10       | 84     | FIN1_CLK3_N                  |

| 01110      |        |                              |

| OP11       | > 86   | FINI_CLK2_P                  |

| ON11       | 87     | FINI_CLK2_N<br>C813          |

|            | 90 100 |                              |

| OP12       | 89 100 | RTM SYNC CLK                 |

| ON12       | 100nF  | C814                         |

|            | 92     | OP15C C P                    |

| OP13       | 93     | OP15C C N                    |

| ON13       |        | 01100_0_1                    |

|            | 95     | FIN2 CLK2 P                  |

| OP14       | 96     | FIN2 CLK2 N                  |

| ON14       |        |                              |

| ODIC       | 98     | FIN2_CLK3_P                  |

| OP15       | 99     | FIN2_CLK3_N                  |

| ON15       |        |                              |

|            |        |                              |

#### Other functions

- Flexible JTAG

- The JTAG chain uses the TI SCANSTA JTAG switch, allowing to access either main FPGA or FMC cards

- Monitoring capabilities

- Temperature measurement: FMC1, FMC2, power supply, FPGA core, DDR memory

- Monitoring of voltage and current in all FMC buses

PANDA DAQT-FEE Workshop 9.04.2015

#### Modes of operation

- The AFCK board may be used in two modes:

- In the standard MTCA crate

- In the stand alone mode. In this case only a single 12V power supply is necessary.

#### AFCK - software needed

- Firmware development

- Xilinx Vivado suite

- Configuration of the board

- via JTAG interface (also limited control is possible)

- Communication with the board

- Currently IPbus via Ethernet is used

- PCIe control should be also possible

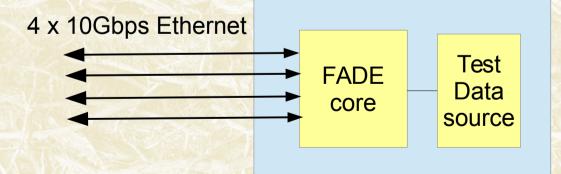

- High speed data transfer from AFCK

- Currently the FADE protocol was tested

- (Later on: FLES interface based solution should be added)

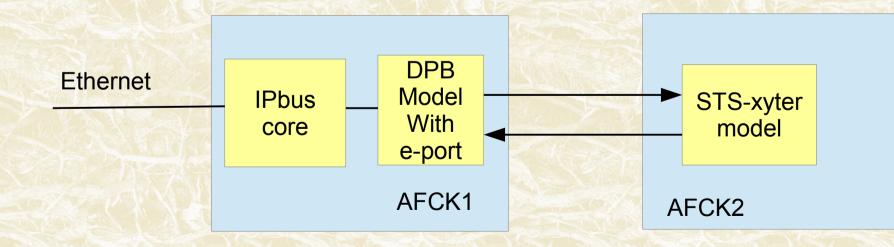

#### Usage of IPbus with AFCK

- IPbus system for control of FPGA based electronics via 1Gbps Ethernet link https://svnweb.cern.ch/trac/cactus

- Free & Open source, but for Xilinx relies on non-free MAC core (may be replaced with simplified, open source implementation)

- Very convenient software prototyping in Python possible

- Final version of software may be implemented in C++

- Testing of the communication with the STS-XYTER ASIC

- Developed firmware and software for control of the STS-XYTER (eg. for link synchronization, for data transmission)

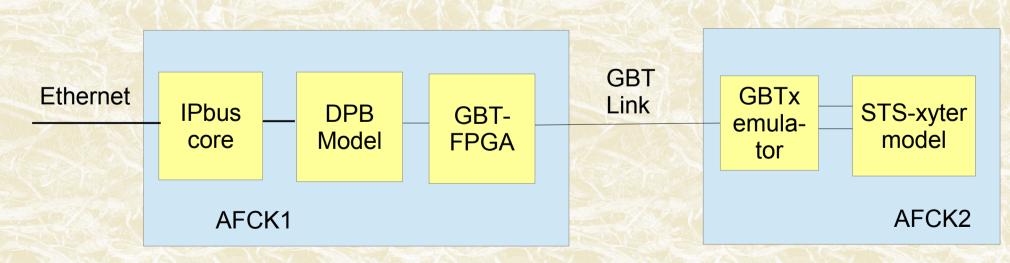

- Testing of the communication with the STS-XYTER ASIC via GBTx emulator

- Tests of GBT-FPGA and GBTx emulator on AFCK platform (to be done in cooperation with colleagues from VECC)

- Testing of high speed data transmission

- Verification of data transmission and control via FADE protocol

(http://opencores.org/project,fade\_ether\_protocol)

- AFCK as a White Rabbit slave

- AFCK was connected to the White Rabbit switch, working as a WR master

- Correct operation of the White Rabbit core was confirmed

- It is a proof of AFCK capability to provide reference clock and timing

• AFCK used for minimalistic setup of real data acquisition (plan)

Slide prepared by Walter Müller for DAQ Meeting 25.03.2015

PANDA DAQT-FEE Workshop 9.04.2015

# AFCK - use scenarios AFCK used for real data acquisition (plan)

Slide prepared by Walter Müller for DAQ Meeting 25.03.2015

PANDA DAQT-FEE Workshop 9.04.2015

#### What next for DPB?

- Possible solutions should be tested on the AFCK platform

- The final, cost optimized version of the DPB board should be designed

- Removal of unnecessary interfaces and functionalities

- Implementation of cost optimized interfaces (e.g. multi-link transceivers like MiniPOD or MicroPOD from Avago)

### Thank you for your attention!