#### Hardware AFCK

Wojciech M. Zabołotny

Institute of Electronic Systems, Warsaw University of Technology

Based on materials provided by Grzegorz Kasprowicz (IES WUT)

#### Requirements for DPB boards

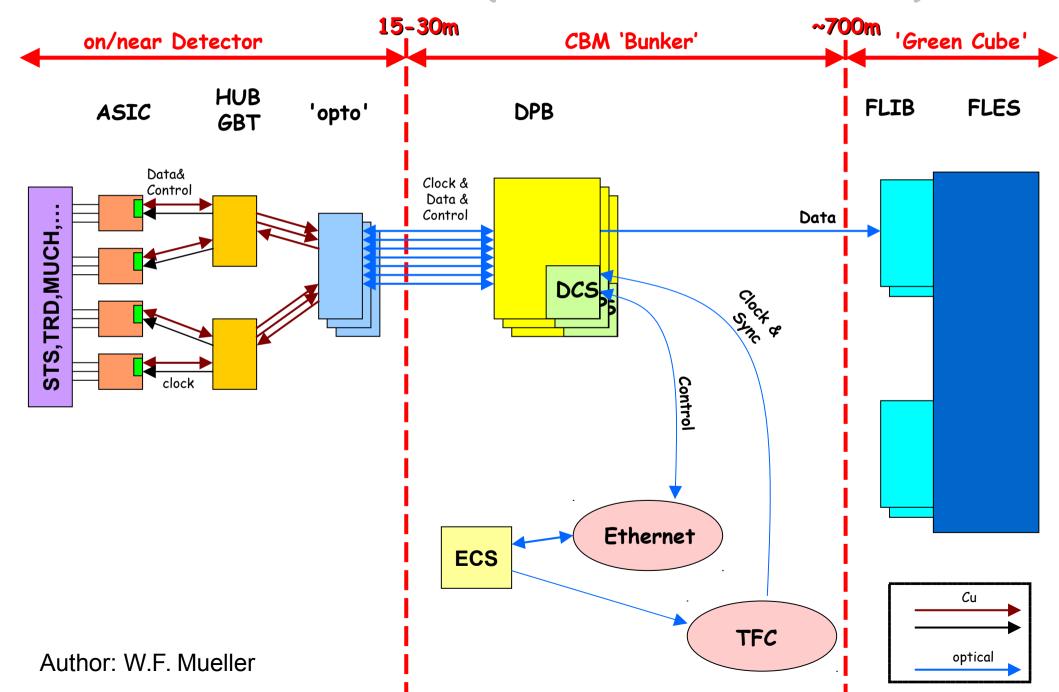

- The Data Processing Boards are intended to be an important component of the CBM readout chain and control system

- They should concentrate and possibly preprocess data received from the front-end electronics, before sending them via long optical links to FLES

- They should provide control (both fast and slow) for FE electronics

- They should distribute reference clock and timing to the FE electronics

#### CBM Data Flow (ASIC based FEE)

#### Requirements for DPB boards

- The Data Processing Boards are intended to be an important component of the CBM readout chain and control system

- They should concentrate and possibly preprocess data received from the front-end electronics, before sending them via long optical links to FLES

- · They should provide control (both fast and slow) for FE electronics

- They should distribute reference clock and timing to the FE electronics

- From the above requirements we can see, that the DPB boards should provide quite complex communication capabilities

- For prototyping we needed versatile board, allowing to check and verify different concepts, related to possible solutions of communication interfaces and associated firmware

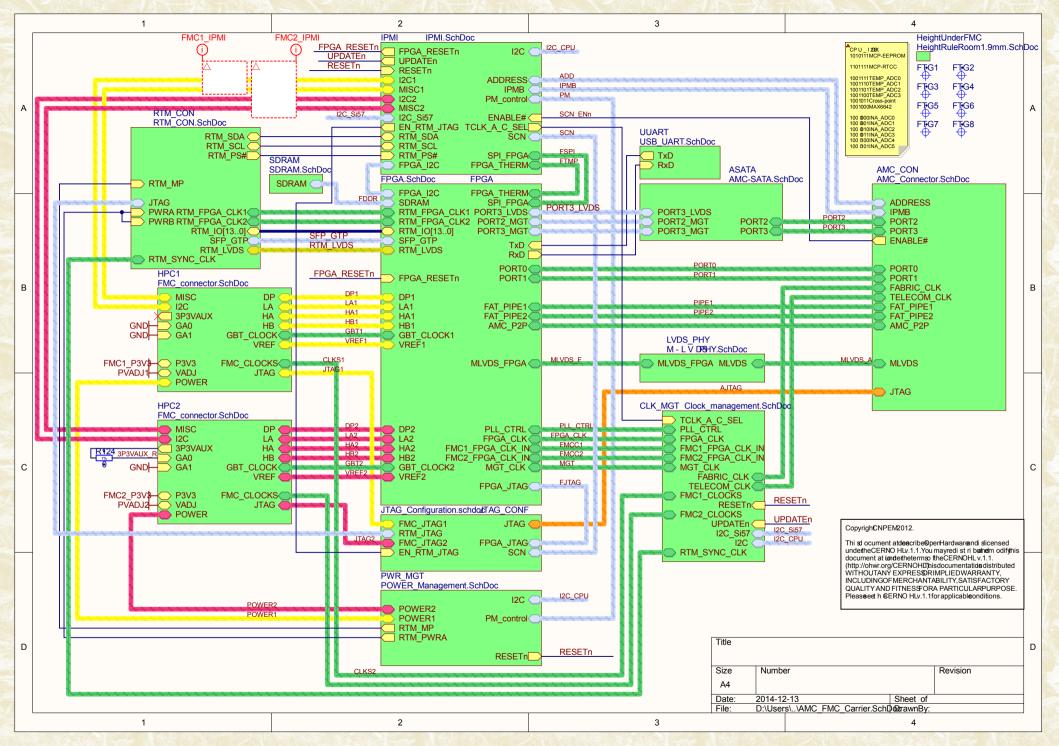

#### MTCA.4 (for Physics) as DPB platform

- Micro TCA Carrier Hub 1 (MCH1) with clocking, Ethernet switch is standard interface.

- 12x custom AMC with FPGA and 6 QSFP optical transceivers. On mid-height AMC.0 double-width board, one can fit 24 + 8 optical links into it. Optionally, one of AMC implements WR core and acts as a timing source. 8 GTX ports are routed to the RTM connector.

- Rear Transition Module (RTM) can be used to further extend number of optical links

- JTAG Switch Module. Used to communicate between MCH1, MCH2 and 12 AMCs for remote debugging (chipscope) and FPGA upgrade

- MCH2 optional, redundant carrier hub with White Rabbit switch, crosspoint switch, low jitter clock distribution circuit and JTAG master port. WR management port can be connected to the general Ethernet network

- Optional AMC with 5 White Rabbit ports (SFPs). In this configuration, the crate may also perform function of WR switch

- MTCA.4, 8U crate with JTAG module (JSM), redundant power supply module and dual fan tray. VT811 from Vadatech is recommended.

- Optional AMC CPU with x86 Intel processor, connected do all AMCs using PCIe interface via MCH PCIe switch

- Optional RTM modules with SFP+ or QSFP connectors

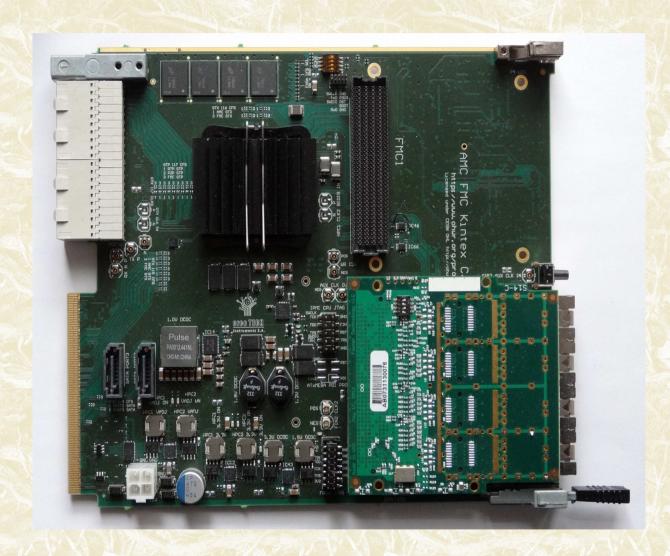

## Existing AFC board

- There was existing Open Hardware AMC FMC Carrier (AFC) board

- Artix based, flexible board in MTCA standard

- with bigger and faster Kintex, and adding even more flexible clocking and communication functionalities it was converted to AFCK, which may be used for development of DPB

#### AFCK board

- Available as Open

Hardware solution on

OHWR website

- Ready to work in the MTCA crate, but usable also in stand alone mode

- This is a prototyping platform, not a final DPB solution!

## Programmable resources

- Module Management Controller (MMC) -LPC1764FBD100 - software may be modified by the user

- Xilinx Kintex 7 325T FFG900 FPGA

- 326080 logic cells (50950 slices)

- 840 DSP slices

- 890 1kb BRAMS, 10 CMTs, 1 PCIe, 16 GTX

#### Memory resources

- 2 GB(16 Gb) of DDR3 SDRAM with 32-bit interface and 800 MHz clock - for huge amount of data requiring relatively slow access

- SPI Flash for FPGA configuration (accessible from MMC)

- · SPI Flash for user data storage

- · EEPROM with MAC and unique board ID

- 16020 kb of data in FPGAs BRAMs for data requiring high speed parallel access

# High speed communication capabilities

- · 2 HPC connectors for 2 single width FMC or one dual width FMC

- Up to 4 GTXs may be routed to each FMC

- In the prototype: GTXs in FMC1 are proven to work at 10 Gbps, while GTXs in FMC2 up to 5 Gbps (in next revision higher speed in FMC2 should be achievable)

- GTXs available in FMC connectors may be optionally routed to the RTM connector

- Another 8 GTX transceivers are available at AMC FP ports (in MTCA backplane)

# Other connectivity functions

- · Mini USB connector connected to MMC

- Mini USB with UART converter connected either to FPGA or to MMC

- SATA connector connected to AMC PORT 2 and 3, which may be routed to FPGA GTX

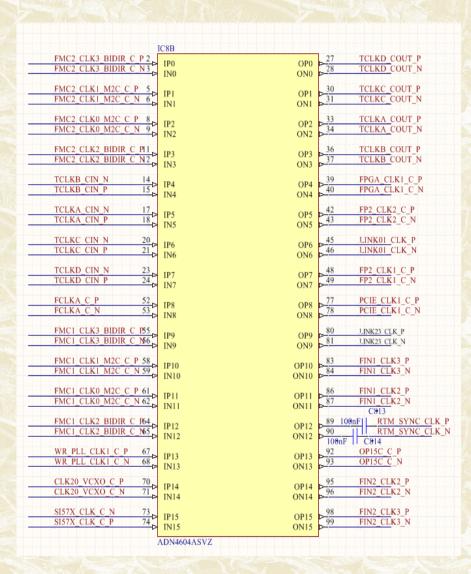

# Flexible clocking

- · Why do we need flexible clocking?

- Different clock domains:

- GBT-FPGA 120MHz or 40MHz

- 1 Gbps Ethernet/WR 125 MHz

- 10 Gbps Ethernet 156.25 MHz

- Clock distribution circuit compatible with White Rabbit

- Based on CDCM61004RHBT and Si57X

- Jitter cleaner allowing to use clock recovered from GTX receiver to drive GTX transmitter

- Clock crossbar with 16 inputs and 16 outputs

#### Other functions

- · Flexible JTAG

- The JTAG chain uses the TI SCANSTA JTAG switch, allowing to access either main FPGA or FMC cards

- Monitoring capabilities

- Temperature measurement: FMC1, FMC2, power supply, FPGA core, DDR memory

- Monitoring of voltage and current in all FMC buses

Joint CBM/Panda DAQ developments-"Kick-off" meeting 19-20.02.2015

## Modes of operation

- · The AFCK board may be used in two modes:

- In the standard MTCA crate

- In the stand alone mode. In this case only a single 12V power supply is necessary.

### Firmware done up to now

- IPbus core successfully ported control of board via Ethernet is working

- Transmission via 4 10 Gbps links through FMC1, using the FADE protocol done

- · Porting of the FPGA-GBT core to AFCK board done

- Porting of the WR core to the AFCK board in progress

- STS-XYTER protocol tester (which includes significant parts of future DPB firmare) - developed on KC705, porting to AFCK - in progress

# Thank you for your attention!