# Summary of the current status of the Cluster-Jet Target test facility established at GSI, Darmstadt

Target Session of LI PANDA Meeting

# **Test Facility at GSI**

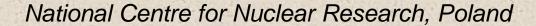

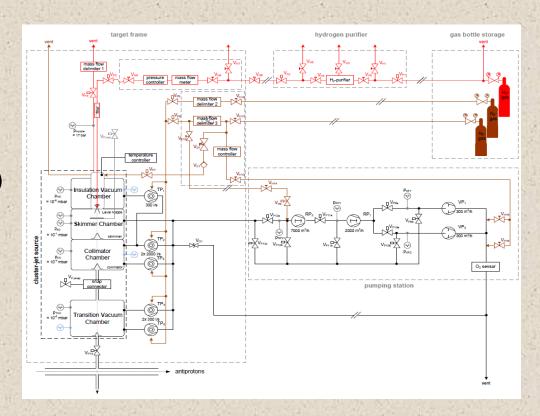

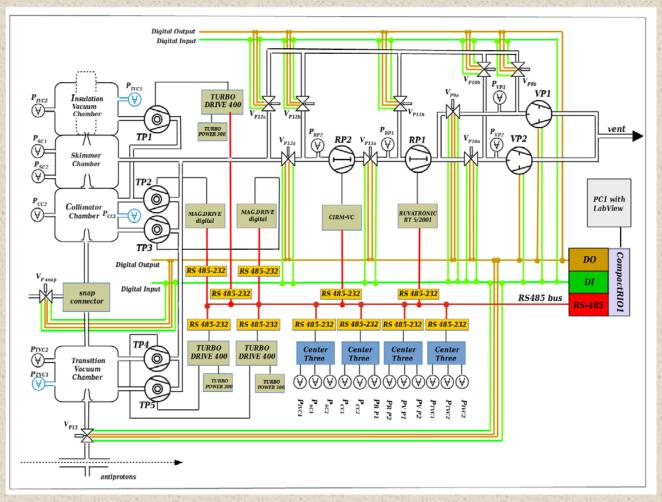

There is a test facility setup established in Darmstadt at GSI Target Laboratory where we can test the ideas with devices similar to the one which are going to be used in final PANDA Slow Control design. Most of the LabVIEW solutions can be transferred to the final set-up with not big modifications or even directly. In the photos we can see the hardware parts of the source, hydrogen supply system and beam-dump.

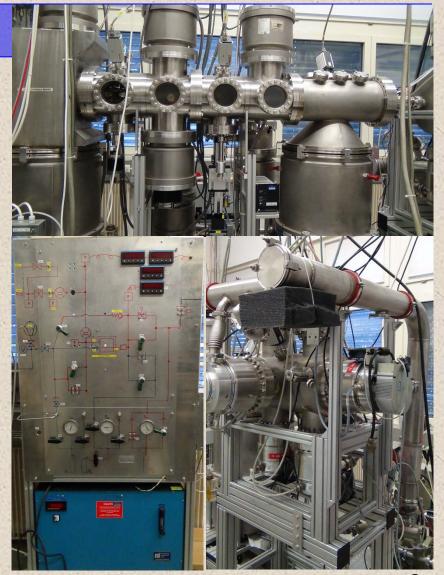

# Hydrogen Supply System

- Pumps the hydrogen, purifies it and supplies the source part of target

- Consists of manual part and controlled part

- Manual part:

- hydrogen container

- pumps

- valves

- Controlled part:

- purifier

- pneumatic valves

- pressure gauges

- temperature sensor (built into purifier)

- CompactRIO + Digital Output Module + RS-485 Module

- Hardware + LabVIEW software works OK

Schematic of Hydrogen Supply System Hardware

# Source Vacuum System

- Controls vacuum level for insulation vacuum chambers, skimmer chamber and collimator chamber

- Consists of:

- pumps

- pump controllers

- pneumatic valves

- pressure gauges

- National Instruments

ADC box

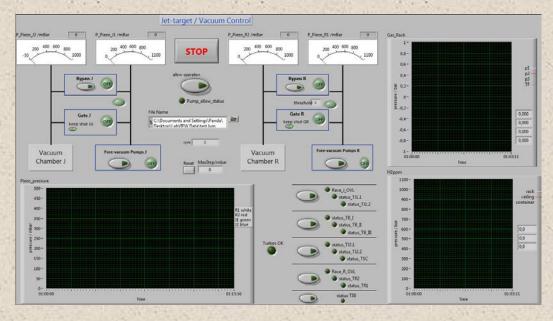

Front Panel of Vacuum Control Program

- CompactRIO + Digital Input Module + Digital Output Module + Analog

Input Module + Analog Output Module + RS-232 Module

- Hardware + LabVIEW software works OK

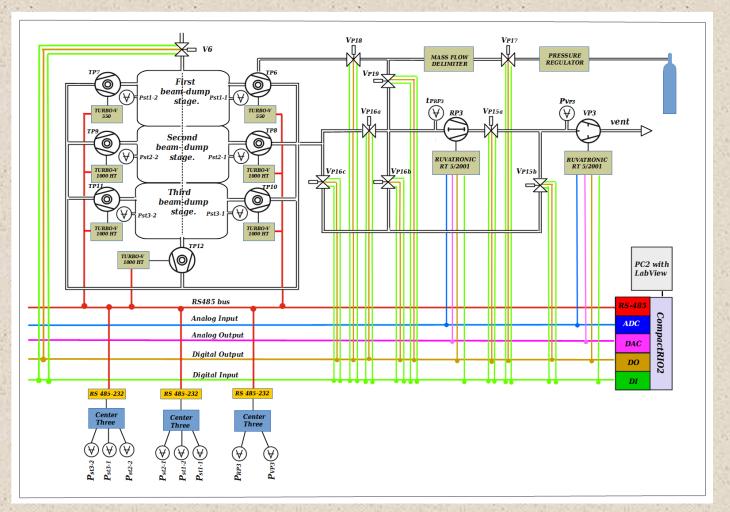

# **Beam-dump System**

- Receives the rest of hydrogen left from the target beam

- Consists of:

- pumps

- pump controllers

- pressure gauges

- CompactRIO + RS-485

Module

- Hardware + LabVIEW software works OK

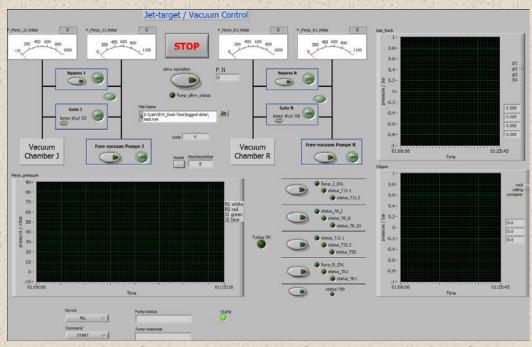

Front Panel of Vacuum Control Program integrated with Beam-dump Control

# **LabVIEW Software Integration**

- At first the programs were running separately and it was needed to integrate some of their parts

- FPGA Program Integration

- integrated into one piece with all necessary control of CompactRIO Modules

- Real Time Operating System (RTOS) Program Integration

- integrated into one piece with all necessary interacting with CompactRIO FPGA and Host Programs

- Host Programs Integration

- there is a separate program for each part of the Cluster-jet Target

- each program displays data and controls in its own window

### **Present State of Software**

Now all the software used in the test facility is in the state that it is possible to run at GSI the whole Facility Target System with its usage.

# **PANDA Target Hardware**

- Cluster-Jet Source

- Hydrogen Supply System (design not finished)

- Main Nitrogen Supply System

- Auxiliary Nitrogen Supply

System (design not finished)

- Cluster Target Vacuum System

- Scattering Chamber Vacuum System (in charge of HESR)

- Cluster Beam-Dump

- Nitrogen Supply System

- Vacuum System

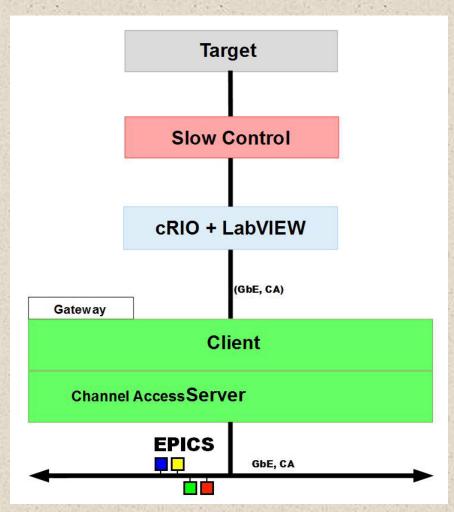

# **Source Slow Control Hardware**

## **Beam-dump Slow Control Hardware**

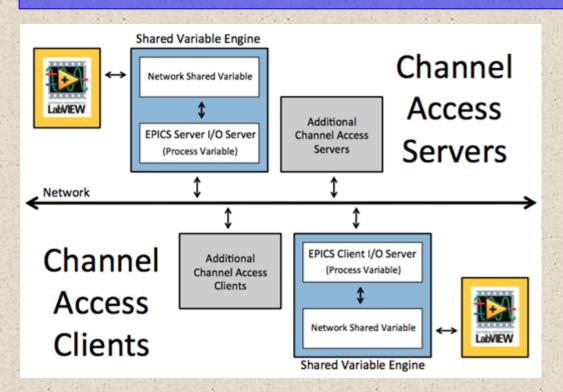

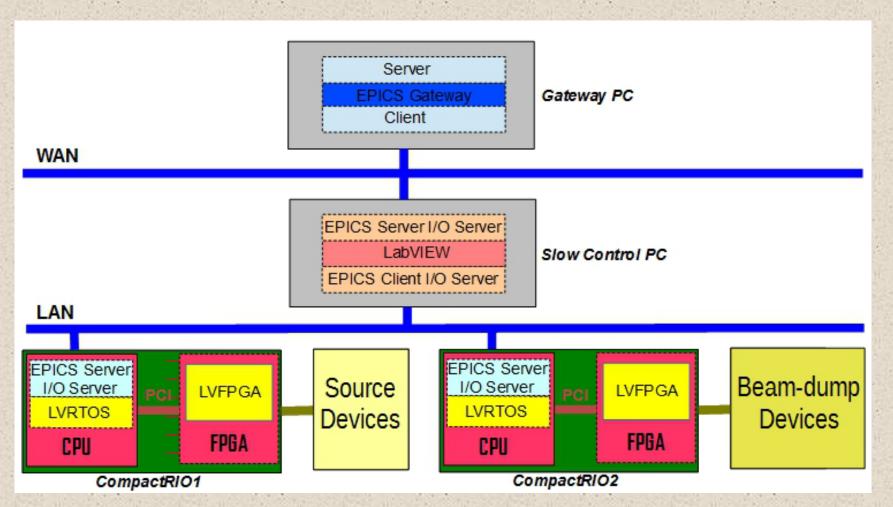

### LabVIEW EPICS I/O Servers

LabVIEW Datalogging and Supervisory Control (DSC) Module and the LabVIEW Real-Time Module act as Channel Access (CA) clients through I/O servers. Use the EPICS Client I/O servers to monitor and update process variables (PVs) that an input/output controller (IOC) or Channel Access server (CAS) publishes using the CA network protocol. With EPICS Server I/O servers, LabVIEW acts as a server that uses the Channel Access (CA) network protocol. Use EPICS Server I/O servers to publish shared variables by using the CA network protocol. An EPICS Server I/O server is a Channel Access server (CAS). You can create an EPICS Server I/O server to publish local and remote shared variables and CompactRIO I/O variables (IOVs).

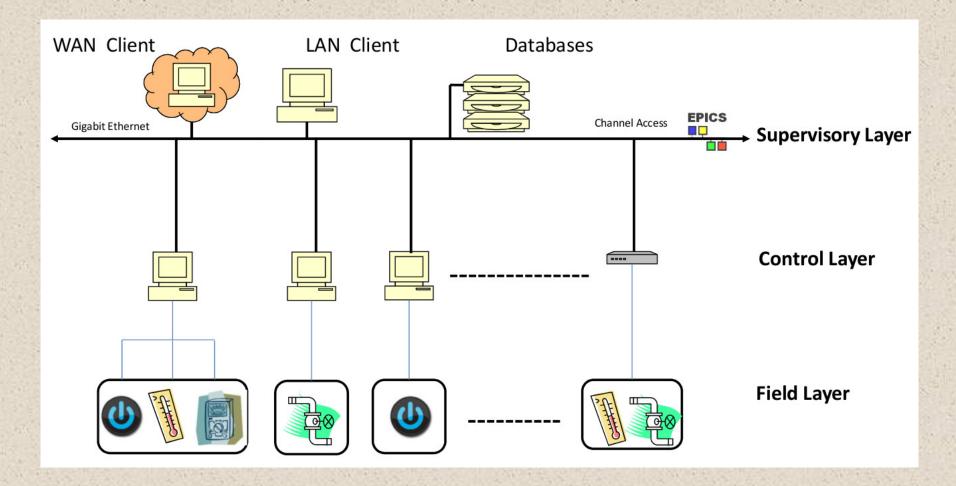

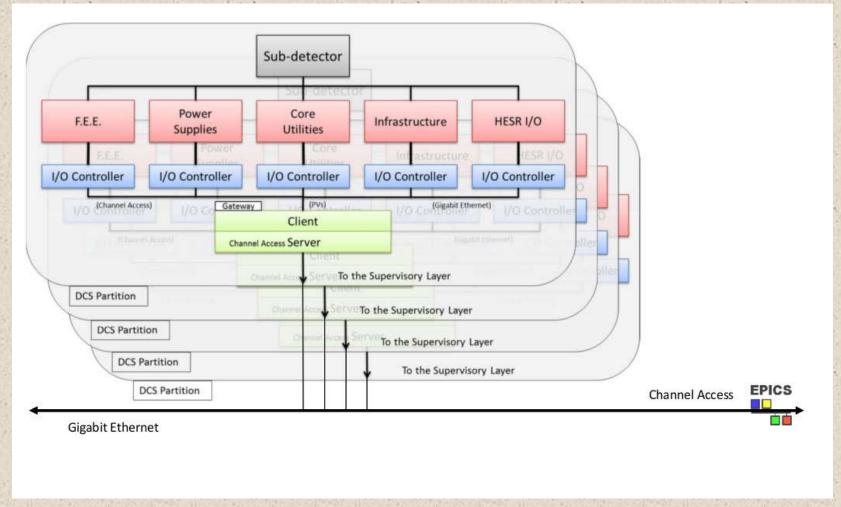

# **Layer Concept for PANDA DCS**

## **Sub-detectors Partitioning**

# **Target Partition**

# Data Exchange Between Layers

### National Centre for Nuclear Research, Poland

# **New CompactRIO Chassis Integrated with Controller**

| Model Type                                       | NI cRIO-9074                                                                                 | NI cRIO-9081                                                                                                | NI cRIO-9082                                                                                                |

|--------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Processor and memory                             | 400 MHz industrial real-time processor                                                       | 1.06 GHz dual-core Intel<br>Celeron processor, 16 GB<br>nonvolatile storage, 2 GB<br>DDR3 800 MHz RAM       | 1.33 GHz dual-core Intel<br>Core i7 processor, 32 GB<br>nonvolatile storage, 2 GB<br>DDR3 800 MHz RAM       |

| Operating System                                 | Vx Works                                                                                     | LabVIEW Real-Time for<br>determinism or Windows<br>Embedded Standard 7 for<br>flexibility                   | LabVIEW Real-Time for<br>determinism or Windows<br>Embedded Standard 7 for<br>flexibility                   |

| Chassis                                          | 8-slot Spartan-3 (2M gate) FPGA chassis                                                      | 8-slot Spartan-6 LX75 FPGA chassis                                                                          | 8-slot Spartan-6 LX150<br>FPGA chassis                                                                      |

| Peripherals                                      | Two 10/100BASE-T<br>Ethernet ports;<br>RS232 serial port for<br>connection to<br>peripherals | 1 MXI-Express, 4 USB Hi-<br>Speed, 2 Gigabit Ethernet,<br>and 2 serial ports for<br>connectivity, expansion | 1 MXI-Express, 4 USB Hi-<br>Speed, 2 Gigabit Ethernet,<br>and 2 serial ports for<br>connectivity, expansion |

| Price (with power supply + mounting accessories) | ~2900 euro                                                                                   | ~6600 euro                                                                                                  | ~7500 euro                                                                                                  |

# **Pictures of CompactRIO Chassis**

NI cRIO-9074

NI cRIO-9081

NI cRIO-9082

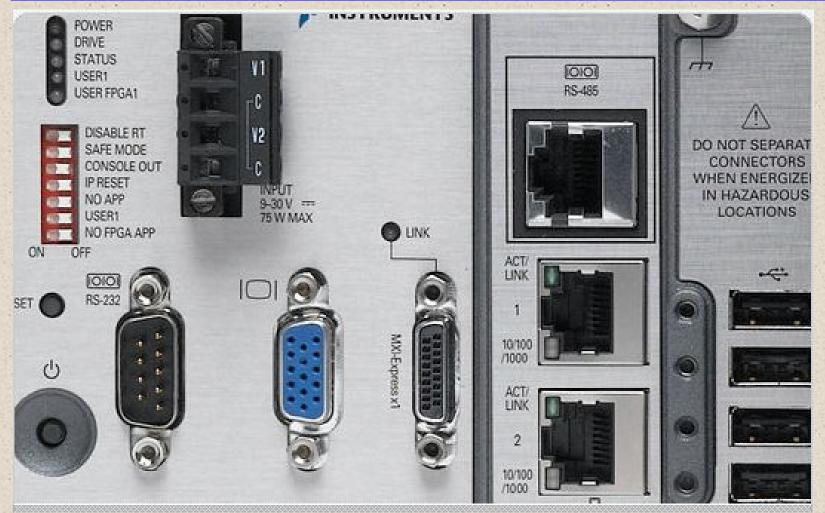

# NI cRIO-9081 and NI cRIO-9082 Peripherals