**PANDA LI Collaboration Meeting**

# Status of ASIC and TRB readout

Paweł Strzempek, Grzegorz Korcyl

Jagiellonian University

Krakow

9 December 2014

#### Remainder

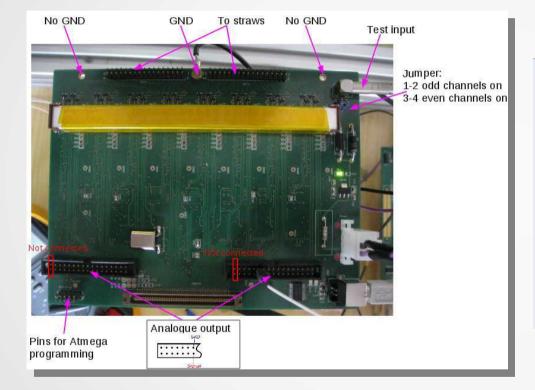

Boards with 8 chips (32 channels)

| Parameter                             | Range/Value       |  |  |

|---------------------------------------|-------------------|--|--|

| Charge gain [mV/fC]                   | 3 - 20            |  |  |

| Peaking time (for delta) [ns]         | 15-40             |  |  |

| Power consumption [mW] $\approx 1$    |                   |  |  |

| ENC [fC]                              | < 0.4             |  |  |

| 1 <sup>st</sup> TC time constant [ns] | 20 - 500          |  |  |

| 2 <sup>nd</sup> TC time constant [ns] | 3 - 40            |  |  |

| Input transistor para                 | meters            |  |  |

| Dimensions W/L                        | $2000\mu/0.35\mu$ |  |  |

| Transconductance [mS]                 | $\approx 26$      |  |  |

| Drain current [mA]                    | 2                 |  |  |

#### Currently used chip parameters

## Setup at Juelich

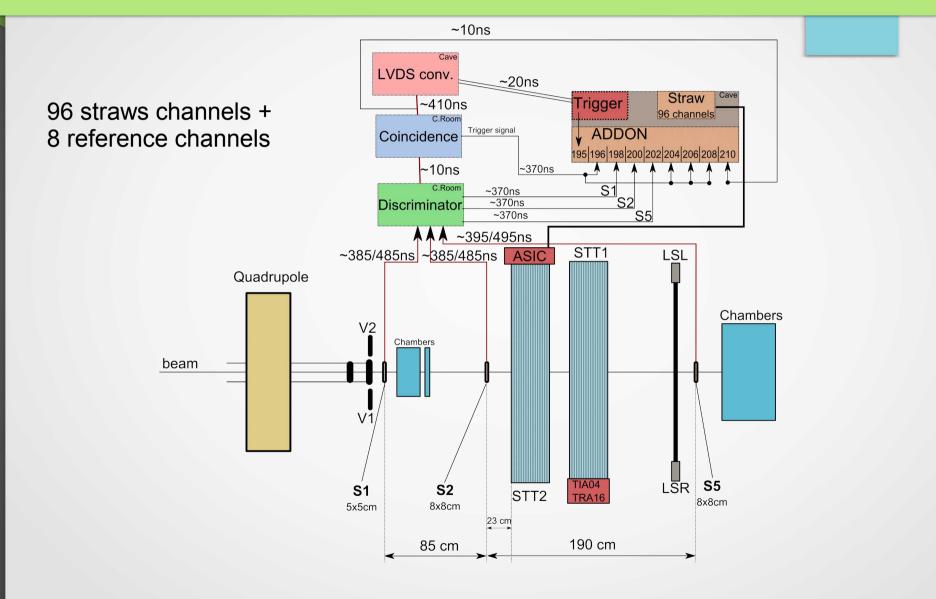

#### Beam set up

#### Read out

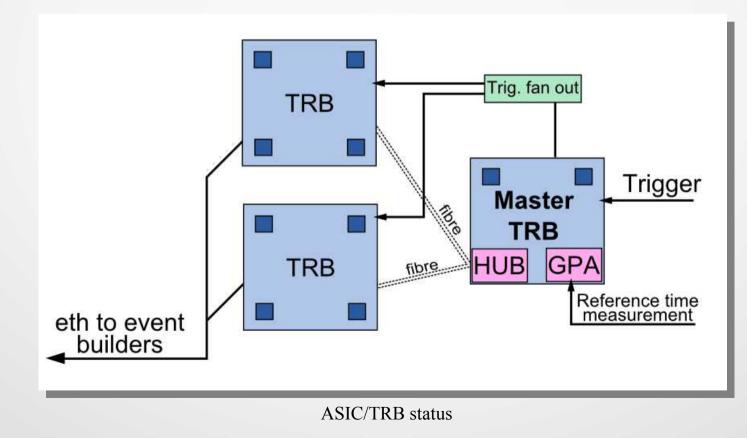

Read out is done with one TRB3. Each FEB is plugged to one TDC. Reference time (scintillators coincidence) is measured with Gpaddon.

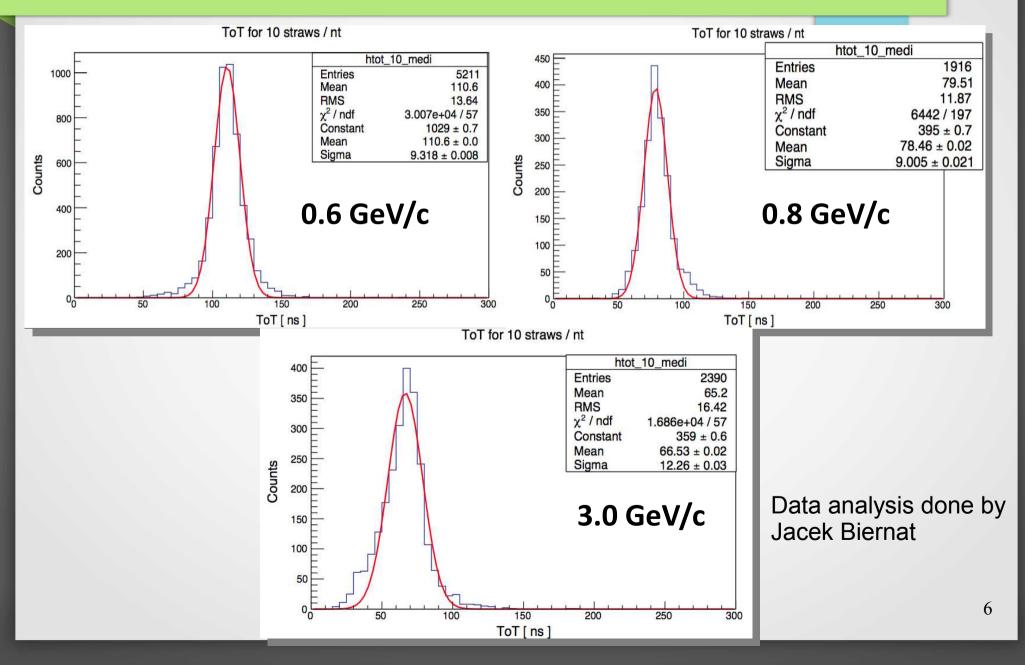

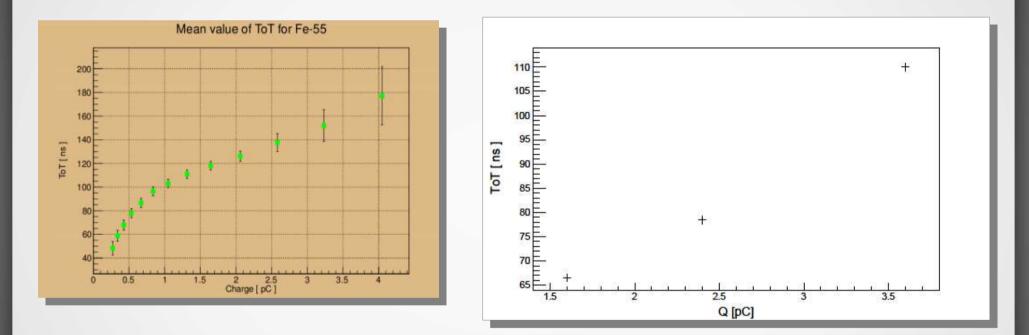

#### ToT momentum scan

### ToT vs charge

Fe-55 source

July 14 proton run

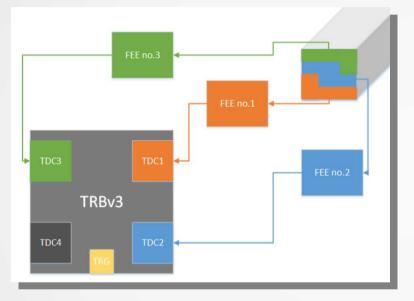

#### Read out upgrade

- TDC version 2.0 48 channels per one TDC + 1 reference signal channel, rising and falling edge detection.

- Multi TRB set-up to enable reading more than 196 channels.

#### Readout upgrade

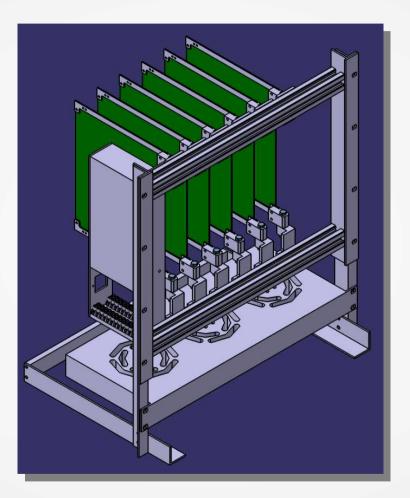

#### TRB crate – installable in a rack.

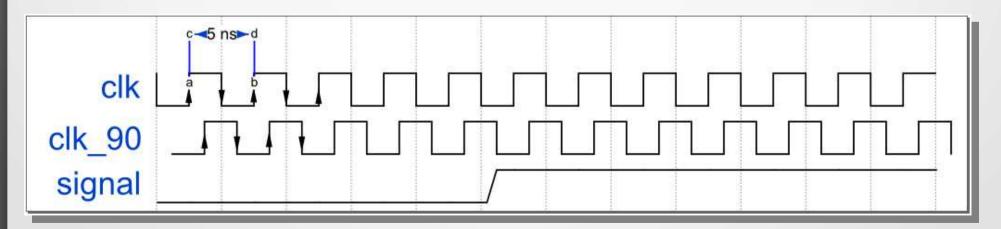

#### Low resolution TDC

- New concept of implementing TDC with resolution reaching 0.5-1ns.

- Incoming signal sampling takes place at rising and falling edge of 200 MHz clock as well as the same clock but phase shifted by 90 degree.

- Less complex logic equals higher channel density.

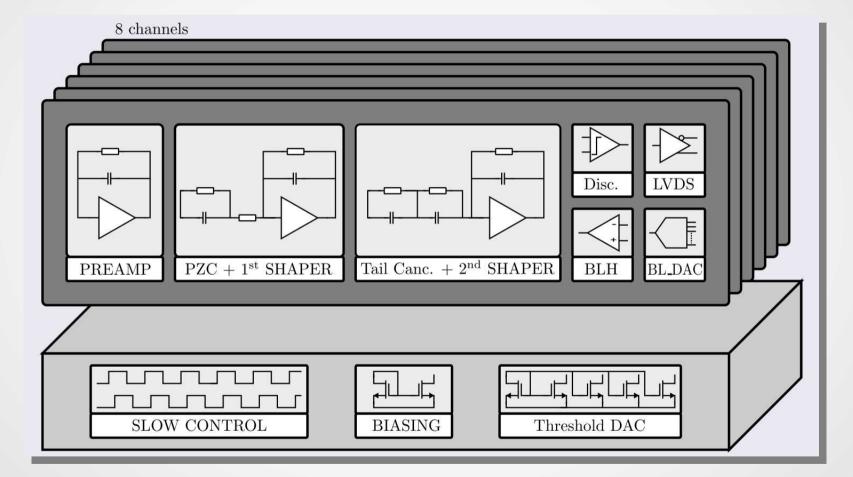

#### New ASIC – block diagram

Schematic view of new ASIC. On chip has 8 channels.

### New ASIC – properties

Properties and new features

- 8 channels, analog and digital (LVDS) outputs

- Variable preamp gain: 0.7; 1; 2 & 4 mV/fC

- Variable peaking time: 14, 18, 24, 38 ns faster than previous chip

- Variable tail cancellation

- 5 bits DACs for baseline level trimming (one per channel)

- 7 bits DAC for thresholds settings (global) till now external DAC used

- Improved baseline holder stability

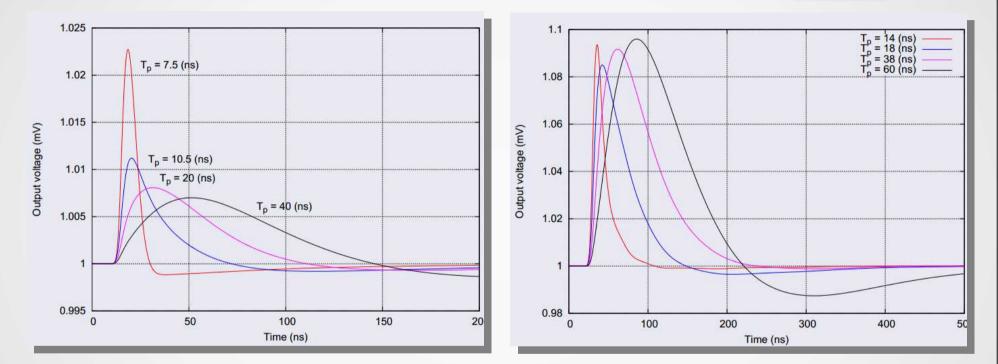

#### **ASIC** simulation

Response for 1fC delta pulses

Response for pions

Simulations done by Dominik Przyborowski – chip author.

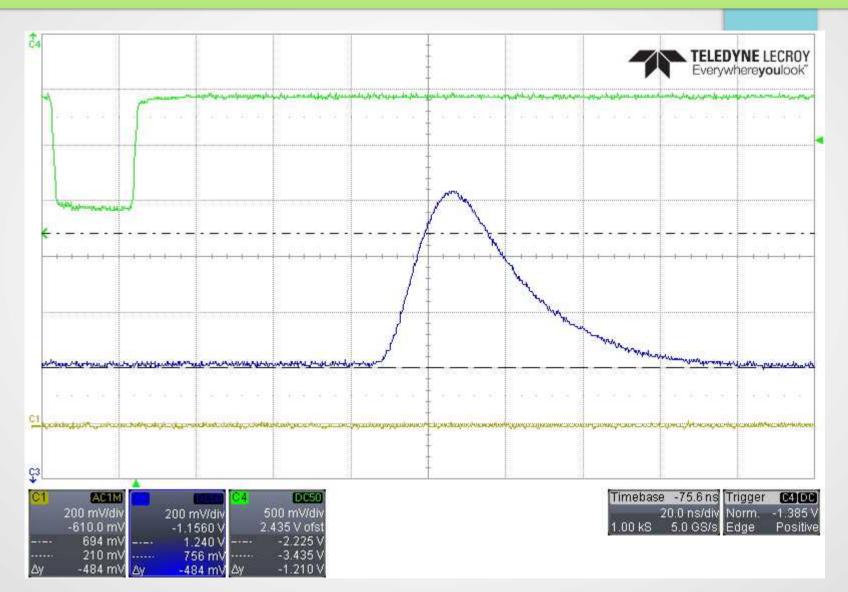

#### **Current status**

- FEB has been produced and initial test were done

- New firmware slow control almost ready

#### **Preliminary tests**

#### Slow control

- Slow control integrated with TRB system.

- Possibility to change individual ASIC settings, baseline for each channel and global threshold.

- Read/write ASIC registers

| Configuration                |              |                |                              |        |   |

|------------------------------|--------------|----------------|------------------------------|--------|---|

| Board e002                   |              |                |                              |        |   |

| losc płyt 1                  | create       |                |                              |        |   |

| Plyta-1                      |              |                |                              |        |   |

| Cable conn-1                 | Cable conn-2 | 🖸 Cable conn-3 | Cable conn-4                 |        |   |

| Asio-1 🗹 Asio-2              |              |                |                              |        |   |

| Plyta-1 Cable-1 Asic-1       | 1            |                | Plyta-1 Cable-1 Asic-2       |        |   |

| Amplification [mV/fC]        | 4 <b>v</b>   |                | Amplification [mV/fC]        | 4 🔻    |   |

| Peaking time [ns]            | 35 🔻         |                | Peaking time [ns]            | 35 🔻   |   |

| TC1C2-0 [pF]                 | 18.5 🔻       |                | TC1C2-0 [pF]                 | 16.5 🔻 |   |

| TC1R2-0 [kO]                 | 31 🔻         |                | TC1R2-0 [k0]                 | 31 🔻   |   |

| TC2C2+0 [pF]                 | 1.65 🔻       |                | TC2C2+0 (pF)                 | 1.65 🔻 |   |

| TC2R <sub>2-0</sub> [kΩ]     | 20 🔻         |                | TC2R <sub>2-0</sub> [kΩ]     | 28 🔻   |   |

| Threshold (Baseline          |              |                | Threshold (Baseline          |        |   |

| divide Baseline + 256<br>mV) | <            | •              | divide Baseline + 258<br>mV) | 4      | • |

| Base line channel 1          | <            | *              | Base line channel 1          | 3 III  | • |

| Base line channel 2          | * 100        |                | Base line channel 2          | 4      | * |

| Base line channel 3          |              | •              | Base line channel 3          | 4      | * |

| Base line channel 4          | 4            |                | Base line channel 4          | 4      | * |

| Base line channel 5          | 1 III        |                | Base line channel 5          | 4 1    | • |

| Base line channel ô          | 4            |                | Base line channel ô          | 4      |   |

| Base line channel 7          | 4            |                | Base line channel 7          | 4      | * |

| Base line channel 8          |              | 100            | Base line channel 8          |        |   |

### Outlook

- FEB test in Krakow

- Building new set up for beam test in 2015

#### Thank you for your attention!

#### pawel.strzempek@uj.edu.pl

Acknowledgments: Project is supported by NCN [DEC-2013/09/N/ST2/02180]