# Front-end Electronics for Straw Tube Tracker in PANDA Experiment

#### Dominik Przyborowski, Marek Idzik

AGH University of Science and Technology

PANDA STT Workshop 10 October 2013, Juelich

#### Outline

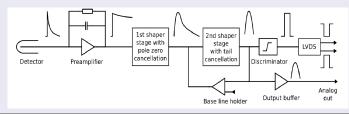

1 Front-end Specification and Architecture

- 2 Measurements of  $1^{\mathrm{st}}$  Prototype

- 4 Summary

## Specification

#### **Features**

- CSP with variable gain and time constant

- CR-RC<sup>2</sup> shaper with variable peaking time

- Ion tail cancellation circuit with trimming

- Baseline stabilized by BLH circuit

- Leading edge discriminator for time and ToT measurements

- Fast LVDS output

- Buffered analog output

### Architecture

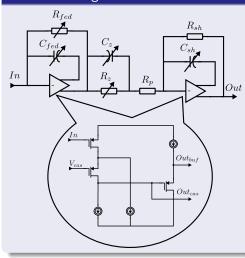

Preamplifier and Shaper

#### Schematic diagram

#### Features

- Variable charge gain: 0.5 – 4 mV/fC

- Variable preamp time constant:

- 25 800 ns

- PZC matched to various preamp settings

- $\bullet \ 1^{st} \ \text{shaper stage with} \ T_P \\ \text{in range} \ 10 40 \ \text{ns}$

#### Input transistor

- Drain current = 2 mA

- W/L =  $2000\mu/0.35\mu$

- Transconductance  $\approx 26 \text{ mS}$

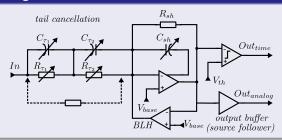

#### Architecture

Tail Cancellation and Output stages

#### Schematic diagram

#### Tail cancellation

- 4 modes of operation:

- $\tau_1 \& \tau_2$  TC, only  $\tau_1$  TC, only  $\tau_2$  TC, CR-RC<sup>2</sup> (no TC)

- Trimming time constants:

$$\tau_1 \in 3 - 43 \text{ ns (6 bits)}$$

$$\tau_2 \in 18 - 511 \text{ ns (6 bits)}$$

Architecture Measurements Design of 2<sup>nd</sup> Prototype Su

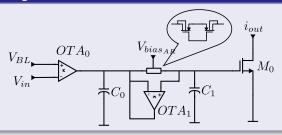

# Architecture Baseline Holder

#### Schematic diagram

#### Components

- Nonlinear buffer (slew rate limited  $OTA_0$  and  $C_0$ )

- High value tunable active resistor for low pass filter

(A. Tajalli, Y. Leblebici, E.J. Brauer, Implementing Ultra-High-Value Floating Tunable CMOS Resistors, Electronics Letters, 2008, pp. 349-350)

- Current sink controlling current in last stage feedback

#### Architecture

Leading Edge Discriminator

# Schematic diagram Voiase InVoiase Voiase Voiase

#### Stages

- Two low-gain preamplifing stages

- Latch stage with histeresis

- Self-biased amplifier

- Inverters

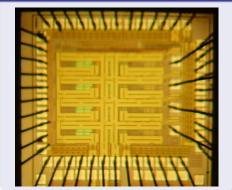

# Measurement results First prototype basic data

- AMS 0.35μm 2P–4M CMOS Process

- Four channels

- Channel size:  $200 \times 1130 \ \mu m^2$

- Power consumption:  $\sim$  15.5 mW/ch + LVDS  $\sim$  12 mW  $\approx$  28 mW/ch

- Peripherals not yet designed, biasing and thresholds setting externally

#### Chip size: $1.5 \times 1.2 \text{ mm}^2$

## Measurement results

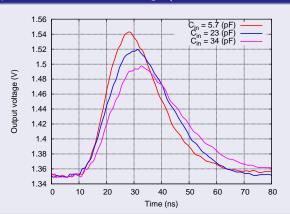

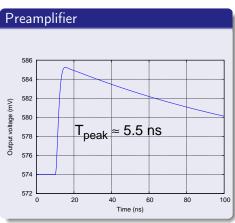

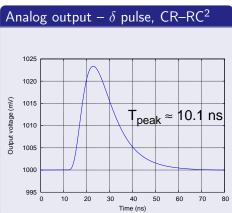

Pulse shapes

#### $\delta$ pulse response for 10ns $T_P$ settings (CR–RC<sup>2</sup> mode – no TC)

Response slower due to layout parasitics and output buffer performance

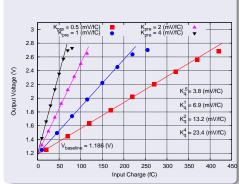

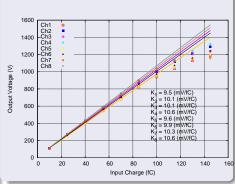

# Measurement results Linearity and Gain

# Channel modes (CR–RC<sup>2</sup> mode – no TC)

#### S-curves measurements

#### Channel uniformity (with TC)

#### Analog buffer output

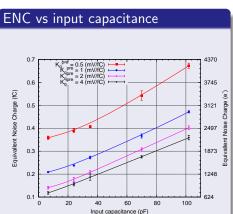

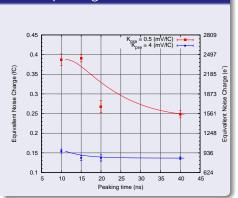

## Measurement results

#### ENC vs peaking time

ENC

$$\approx 1000$$

e<sup>-</sup> for default FE settings ( $K_{pre}=2mV/fC,~T_P=10ns$  and  $C_{in}=25 pF$ )

## Measurement results Tail cancellation

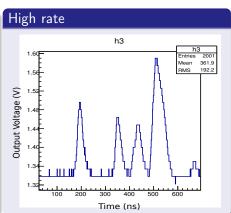

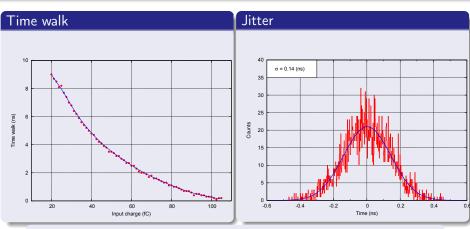

## Measurement results

Time resolution

1–2 ns time precision could be obtained by compensating time walk basing on amplitude information

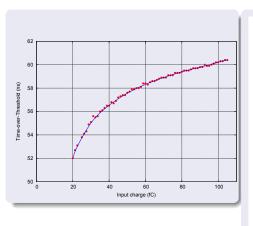

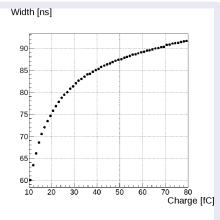

# Measurement results Time-over-Threshold

Results achieved for delta pulse and different FEE settings

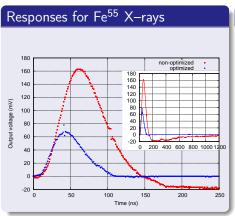

## Measurement results

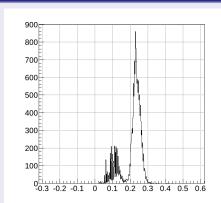

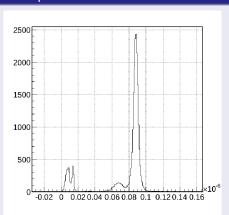

Fe<sup>55</sup> X–rays spectrums

#### Amplitude spectrum

#### ToT spectrum

Good separation of  $Fe^{55}$  K- $\alpha$  and escape peaks for both methods

Architecture Measurements Design of 2nd Prototype Su

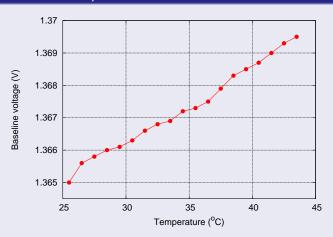

## Measurement results

Baseline

#### Baseline level vs temperature

Measure after output buffer –  $V_{gs}$  and  $\beta$  variations

- 1<sup>st</sup> prototype of STT front-end fully functional

- $\bullet$  Variable gain 3 24 mV/fC and peaking time  $\sim$  20 40 ns work well

- ENC  $\approx 1000$  e<sup>-</sup> for default conditions ( $K_{pre} = 2mV/fC$ ,  $T_P = 10$ ns and  $C_{in} = 25$ pF)

- Tail cancellation works and could be trimmed to various types of input signals

- Readout module with 8 ASICs (32 channels) successfully used in test-beam

- The front-end design and performance was presented at TWEPP-2013

## Design of 2<sup>nd</sup> Prototype

#### Features not implemented in 1st prototype

- Lack of DACs for baseline control (high baseline dispersion was expected)

- Longer  $T_P$  (18 ns) in post-layout simulations

#### Issues found during tests

- Saturation of preamplifier for large signals

- Analog buffer not addapted for high capacitive load

#### Planned improvements

- Implementation of 8 channels

- Redesign of preamp/shaper for higher speed ( $T_P=10$  ns)

- DAC addition and BLH modification for uniform baseline

- Improvement of analog buffer

- Elimination of saturation for large signals

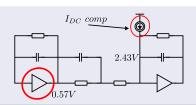

#### Planned Modifications

- Complementary architecture with pseudo Class AB Flipped Voltage Follower

- DC current compensation circuit

- Variable charge gain: 1, 2 and 4 mV/fC

- Response rise time  $\sim$  5 ns (3× faster)

#### Planned Modifications

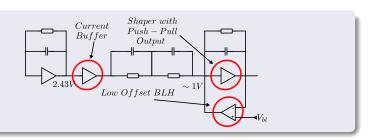

- Current buffer to separate 1<sup>st</sup> shaper stage and tail cancellation (to avoid  $T_p$  walking vs TC settings)

- Improvments of BLH to minimize offset ( $\sigma \approx 5 \text{ mV}$ )

- 2<sup>nd</sup> shaper stage with high performance Push-Pull buffer

#### Design of 2<sup>nd</sup> Prototype Simulation results

$T_P \approx 15 \text{ ns in } 1^{st} \text{ prototype}$

$T_P \approx 17 \text{ ns in } 1^{st} \text{ prototype}$

# Design of $2^{\mathrm{nd}}$ Prototype Simulation results

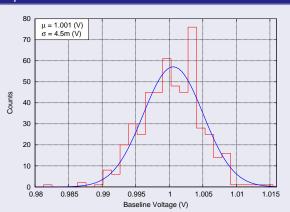

#### Baseline dispersion

- Baseline dispersion one order of magnitude less than in 1<sup>st</sup> prototype

- 4-bits DAC will be added for fine tunning

## Summary and plans

#### Front-end development status

- 1<sup>st</sup> prototype of STT front-end fully functional

- $\bullet$  Variable gain 3 24 mV/fC and peaking time  $\sim$  20 40 ns work well

- ENC  $\approx 1000 \text{ e}^-$  for default conditions ( $K_{pre} = 2mV/fC$ ,  $T_P = 10ns$  and  $C_{in} = 25pF$ )

- Tail cancellation works and could be trimmed to various types of input signals

- Readout module with 8 ASICs (32 channels) successfully used in test-beam

#### Future plans

- New improved front-end design in progress:

- 8 channels

- DACs for threshold and baseline settings

- Faster preamp/shaper

- Stronger output buffer

- Better performance for large signals

- Submission of new prototype planned at the end of this year (if founds available)