# RICH firmware / DAQ

Simon Reiter 21. October 2025

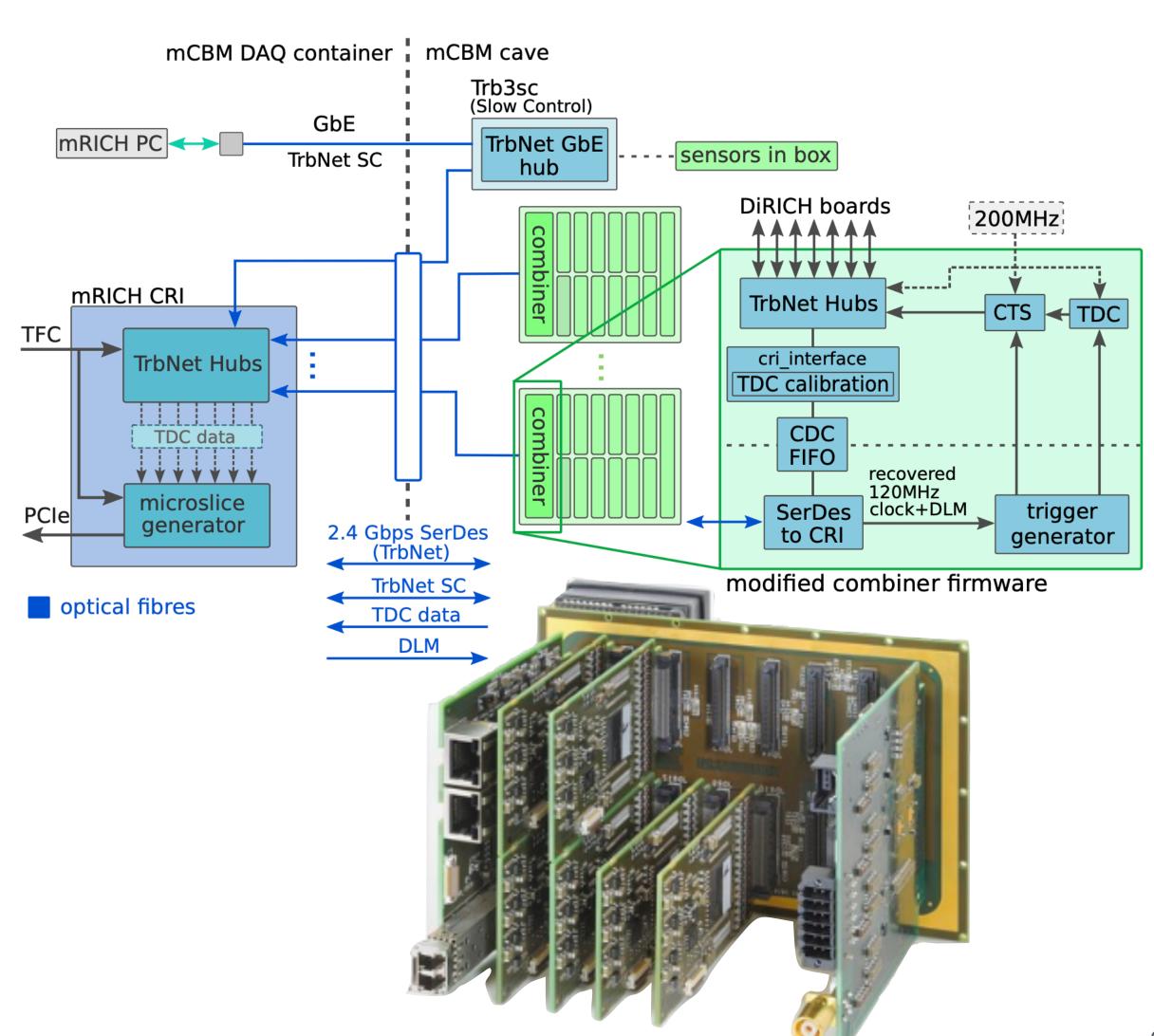

### Current Readout Scheme

- Adopted from HADES

- Based on TRBnet

- Quasi free streaming operation with high rate pulse trigger —> gapless readout

- CRI controls and receives data from concentrator boards acting as TRBnet hubs

- 200 DIRICH concentrators are handled by 6

CRI1 boards

#### Current Readout Limitations

- Designed and developed for triggered system

- Key feature: Receive data from all endpoints to create complete events before next trigger arrives

- Misbehaving endpoints may corrupt entire data acquisition

- Single Link for Data Transfer, Synchronization, Triggering and Slow Control

- Static Setup, where endpoints are scanned once and configuration is not supposed to change

#### Current Readout Limitations

- Less suitable for high radiation environments

- Single Event Upsets have high impact on entire DAQ chain

- Reintegration into DAQ is not foreseen

- —> full reboot with reinitialization is inevitable and already shown to be a design flaw in mCBM

- TRBnet not actively development anymore at GSI

### Future Readout Concept

- Successor for DIRICH modules in active development: **DOGMA**

- Based on (nearly) same hardware

- Focus on

- non-interruptible data taking

- Modular system, where endpoints restart and reintegrate automatically

- Utilize standard protocols for conventional tasks

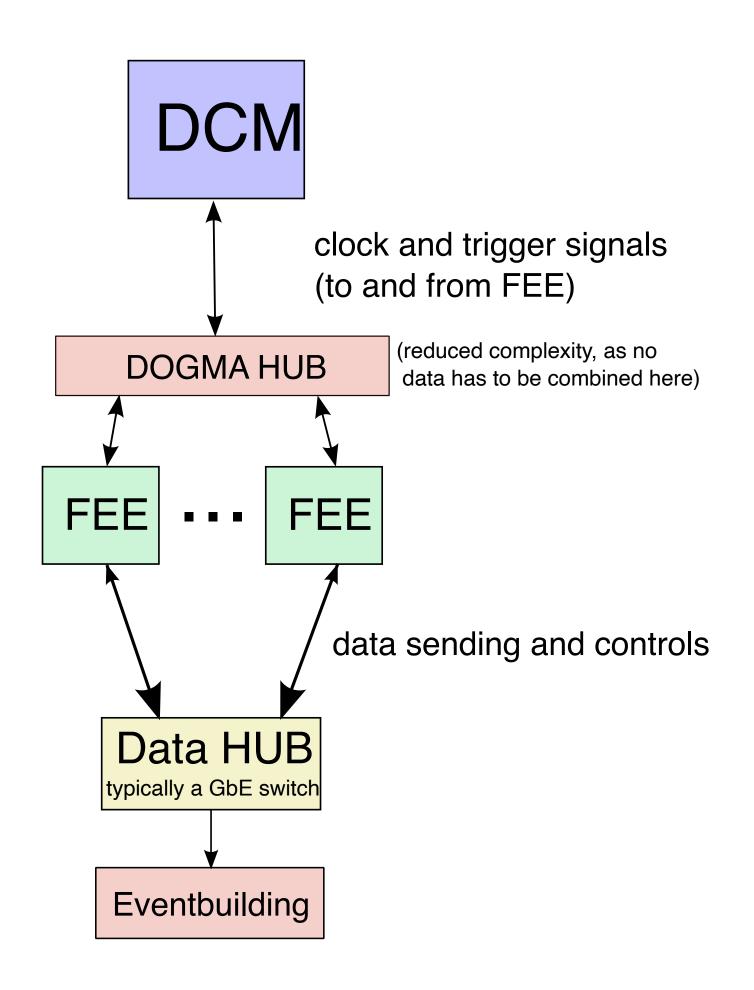

### Future Readout Concept

- DOGMA Control Module (DCM) fully synchronizes all endpoints

- Synchronization and Triggering via proprietary protocol, but fully separated from data link

- --> requires 2 optical links per DIRICH instead of 1

- Hubs are used for fanout and synchronization

- 10ps timing precision

- Deterministic latency

- Data Transfer and Slow Control use Ethernet UDP

- Hubs can be realized by commercial GbE switches

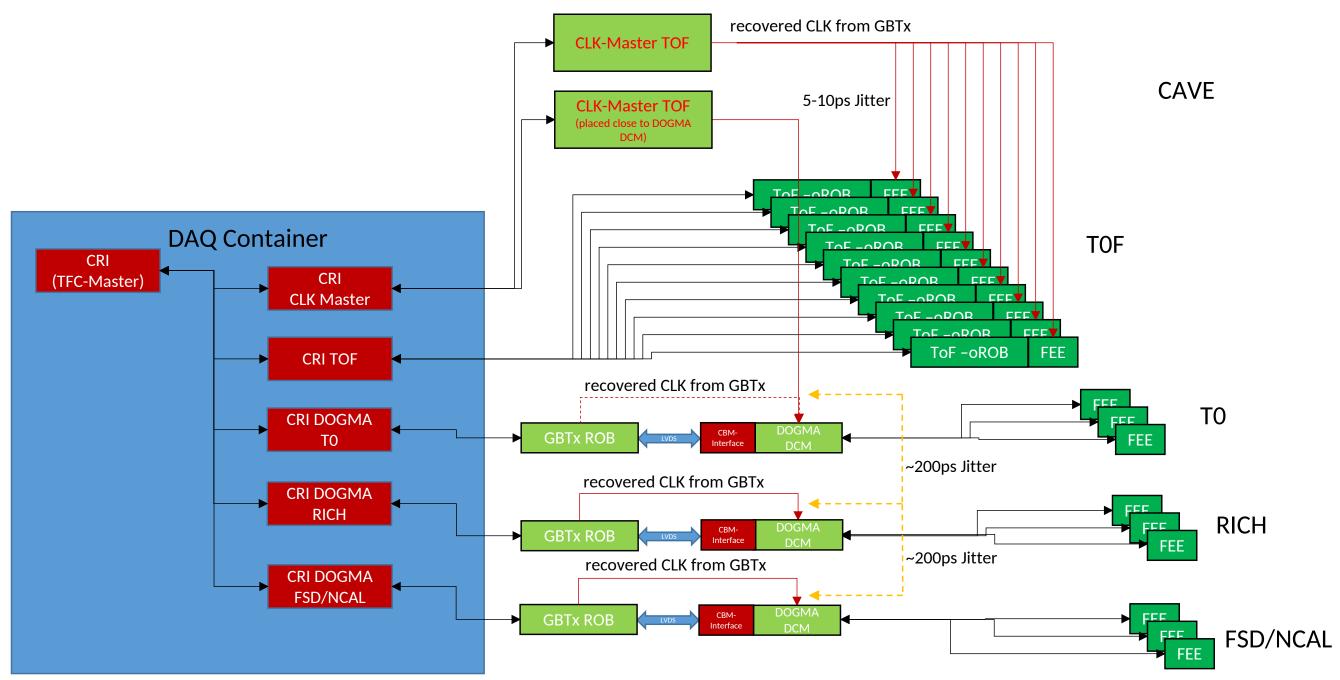

#### Future Readout in CBM

- DOGMA replaces TRBnet on DIRICH front-ends

- Media access interface and UDP data receiver will be integrated into CRI firmware (similar to TRBnet)

- DOGMA DCM receives system clock + micro slice ID + synchronization from CRI-based CBM DAQ, and forwards to endpoints

- Development of new concentrator board

- Act as Ethernet hub and dogma hub to reduce number of FE links

- Reuse existing DIRICH

- Anyhow necessary to increase data rate between front-end boards and CRI (current bottleneck)

#### Future Readout in CBM

- DOGMA DCM will be interconnected via existing iROB GBTx interface by TOF

- One CRI will do entire steering for RICH

- Other DIRICH-based sub-detectors showed interest in transition

• DIRICH and DOGMA as FPGA-based alternative to ASIC-based front-ends

## Ongoing Work

- Implementation of Ethernet interface on CRI

- Start from existing firmware design, where many parts can be reused (micro time slice building, ...)

- Ethernet support from DOGMA group

- Implementation of CRI —> iROB GBTx —> LVDS —> DOGMA CTS interface

- First steps already done by Esteban Rubio @ GSI test setup

- Support on final steps promised by GSI

# Ongoing Work

- Implementation of test setup on existing concentrator (single HS link available)

- H. Heggen / M. v. Bülow (GSI) working on DOGMA hub integration to prepare first full test setup soon, maybe even with mRICH

- Old ECP3 FPGA causes some troubles

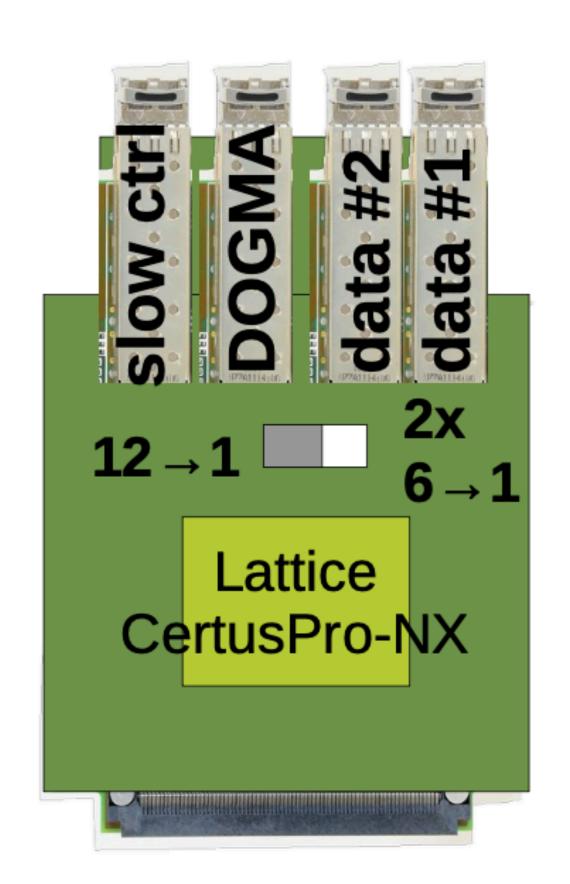

### Future Work

- Design new DOGMA Concentrator for RICH by M. Traxler, H. Heggen, et. al.

- Upgrade FPGA to Lattice CertusPro-NX for improved radiation hardness

- Upgrade single SERDES link on backplane to 1x SERDES + 1x LVDS link for data (Ethernet) and clock/sync

- Upgrade single 2.4 Gbps SFP optical link to 2x 10Gbps SFP optical link

+ 1x SFP clock/sync [ + 1x SFP slow control ]

### Summary

- Current readout protocol *TRBnet* has proven to work reliable in mRICH, but DAQ integrity is impacted in radiation environments

- New DOGMA protocol for existing hardware tackles this by allowing endpoints to be removed and reintegrated flexibly during data taking

- Firmware development for CRI on trigger and receiver side has started, targeting first test system by end of 2025