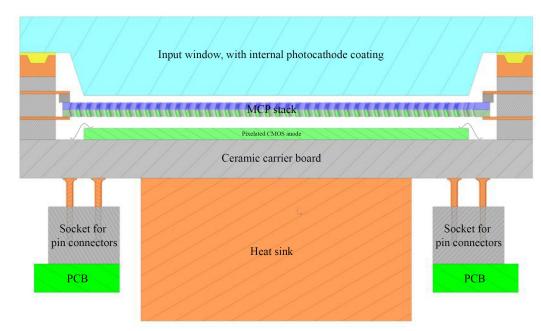

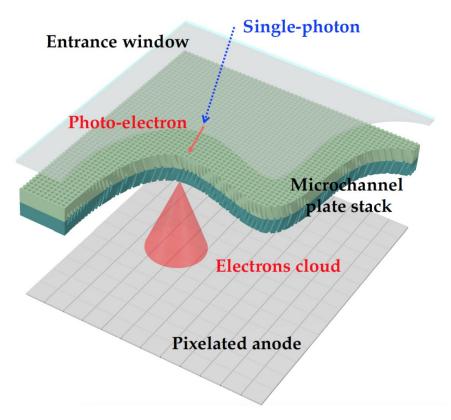

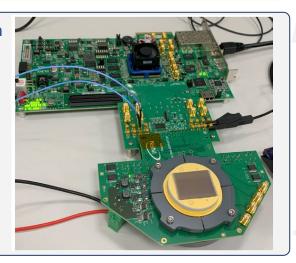

# Hybrid MCP-PMT concept

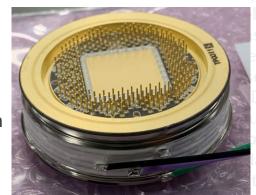

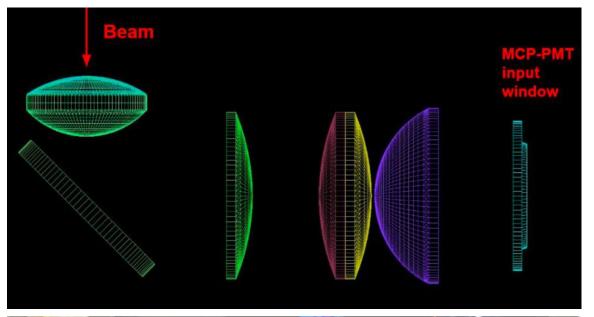

M. Fiorini et al, JINST 13 (2018) C12005

- Entrance window + photocathode

- MCP stack (Chevron or Z-stack configuration)

- Pixelated CMOS anode: Timepix4 ASIC

- Ceramic carrier board

- interface between inner/outer parts of the detector

- custom Pin Grid Array for I/O signals

- Heat sink (ASIC power 5 W)

- PCBs to connect the detector to a FPGA-based DAQ system

Previous projects demonstrated the use of a bare ASIC inside a vacuum tube with a microchannel plate (MCP)

- optical imaging tube based on Medipix2 ASIC [Proc. SPIE 7021 2008 (J .Vallerga, A. Tremsin et al.)]

- optical imaging tube with a quad Timepix readout [JINST 9 C05055 2014 (J. Vallerga, A. Tremsin et al.)]

# Hybrid MCP-PMT concept

### Detector operating principle

M. Fiorini et al, JINST 13 (2018) C12005

- A photon is converted into a photo-electron within a high Quantum Efficiency (QE) photocathode

- The photo-electron is guided by a drift electric field toward a microchannel plate (MCP) arranged in a Chevron configuration.

- The electron cloud generated by the MCP is then directed by another drift field onto the input pads of a bare Timepix4 ASIC, where it is detected as a charge pulse by the readout electronics.

- Inside the vacuum tube, the Timepix4 ASIC amplifies, discriminates, and digitizes the MCP signal.

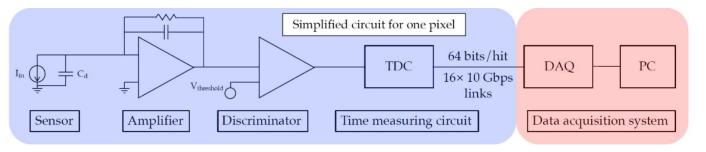

# Pixelated anode: Timepix4 ASIC

- Developed by Medipix4 collaboration

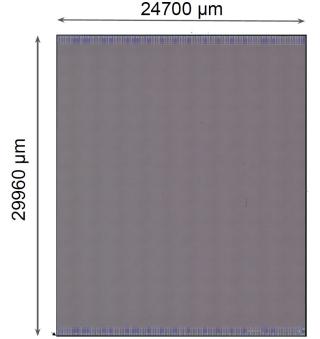

- **512**  $\times$  **448 pixels** (55 µm  $\times$  55 µm each)

- Large active area:  $7 cm^2$

- Bump pads used as anode

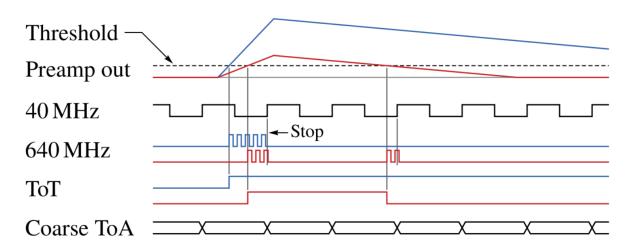

- Time-stamp provided by Time-to-Digital Converter (TDC) based on Voltage-Controlled Oscillator (VCO)

- 195 ps bin size (~ 56 ps r.m.s. resolution) for Time-of-Arrival (ToA) measurements

- 1.56 ns bin size for Time-over-Threshold (ToT) measurements

- High rate capability:

- maximum bandwidth: 160 Gb/s

- maximum hit rate: 2.5 Ghits/s

- Output:

- 64 bits of data per hit with 64b/66b encoding

- transmitted via 16 high-speed links up to 10.24 Gbps

https://iopscience.iop.org/article/10.1088/1748-0221/17/07/P07006

# Pixelated anode: Timepix4 ASIC

#### Pixel level:

- analog front-end:

- pixel enable

- input pad

- charge integration circuit

- local threshold

- local test pulse

- digital front-end:

- pixel mask

- TDC and time stamp

#### SP level:

- VCO

- pixels readout

#### SPG level:

Adjustable Delay Buffer, to correctly distribute the reference clock to the pixels across the double column

| Tecl              | nnology         |               | CMOS 65 nm                                |  |

|-------------------|-----------------|---------------|-------------------------------------------|--|

| Pixe              | el Size         |               | 55 μm × 55 μm                             |  |

| Pixe              | el arrangement  |               | 4-side buttable<br>512×448 (0.23 Mpixels) |  |

| Sensitive area    |                 |               | 6.94 cm <sup>2</sup> (2.82 cm × 2.46 cm)  |  |

| out<br>es         | Data driven     | Mode          | TOT and TOA                               |  |

| Read-out<br>Modes |                 | Event Packet  | 64-bit                                    |  |

| Re.<br>M          |                 | Max rate      | 358 Mhits/ cm²/ s                         |  |

| TDO               | C bin size      |               | 195 ps                                    |  |

| Rea               | dout bandwid    | th            | ≤163.84 Gbps (16× @10.24 Gbps)            |  |

| Equ               | ivalent noise c | harge         | 50-70 e⁻                                  |  |

| Targ              | get global mini | mum threshold | <500 e-                                   |  |

X. Llopart et al 2022 JINST 19 C01044

ASIC in 65 nm CMOS

**Electron cloud** spread over a number of pixels → **cluster**

Exploit **ToT** information (∝ charge in a pixel) to:

- Correct for time-walk effect in every pixel

- Improve position resolution by centroid algorithm

- from  $\frac{55}{\sqrt{12}}\mu m \sim 16 \mu m$  down to  $5-10 \mu m$  r.m.s. (MCP channels pitch)

- Improve timing resolution by multiple sampling

- Many timing measurements for the same photon  $\rightarrow$  **few 10**s **ps** r.m.s.

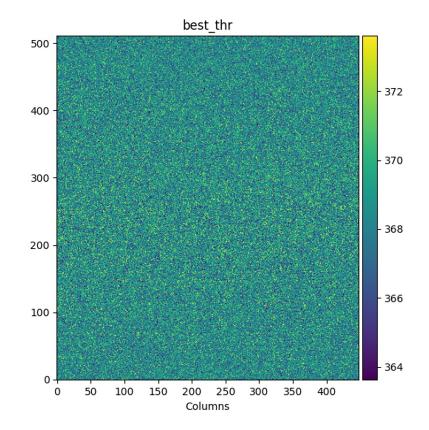

## **Equalization and Calibration**

- ✓ Threshold equalization

- Threshold fine tuning at pixel level

- Noisy pixels detection

- On the whole matrix (~230 k pixels)

X. Llopart XII Front-End Electronics Workshop

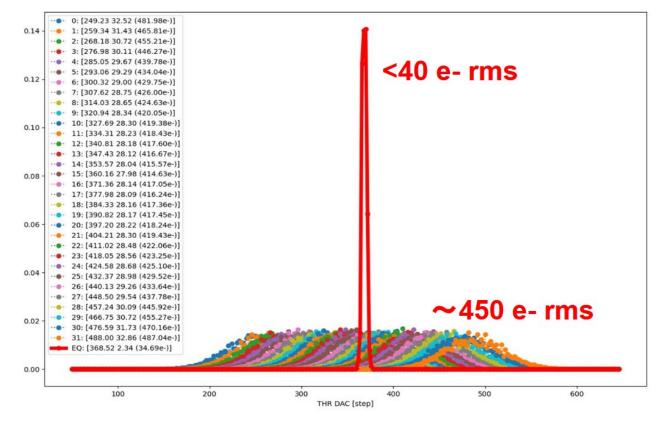

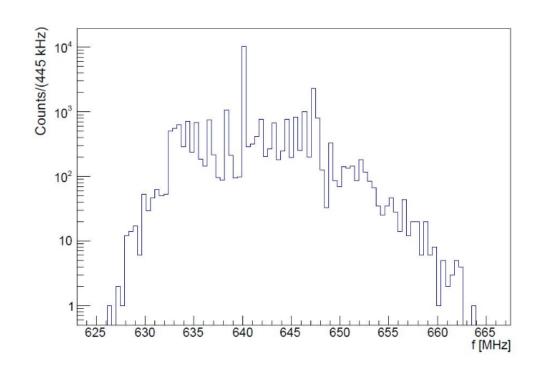

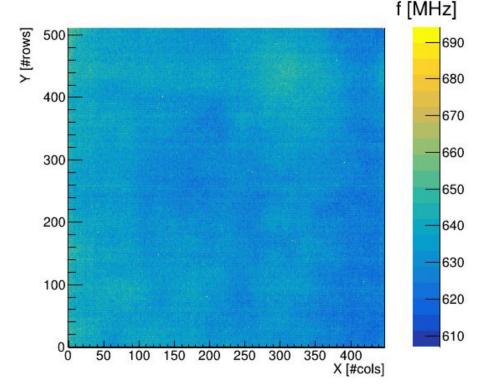

- √ VCO frequency calibration

- On pixel VCO oscillation frequency controlled by a PLL at the center of the chip (@ 640 MHz nominal)

- VCO design sensitivity of 1MHz/mV

- Spread of 40 MHz

- Noise measurements used to calibrate VCO frequencies for the whole matrix (~29 k VCOs)

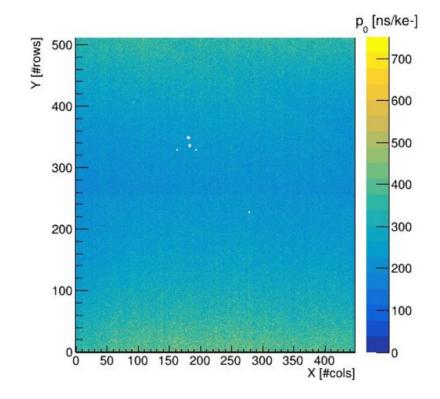

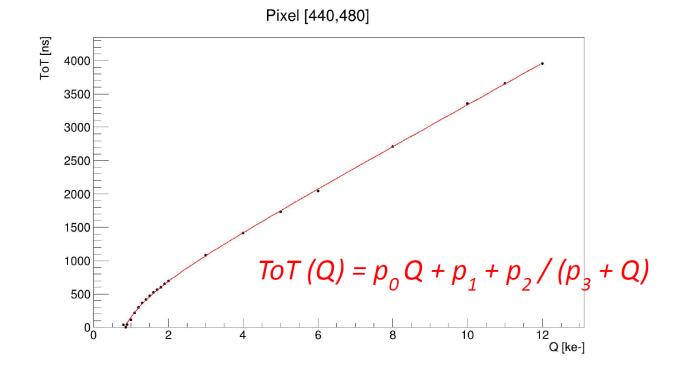

- ✓ ToT vs Q calibration with testpulse

- At fixed charge, large ToT spread across the matrix due to local gain differences

- Non-linear calibration performed with integrated test pulse tool

R. Bolzonella et al 2024 JINST 19 P07021

## **Equalization and Calibration**

- ✓ Threshold equalization

- Threshold fine tuning at pixel level

- Noisy pixels detection

- On the whole matrix (~230 k pixels)

X. Llopart XII Front-End Electronics Workshop

- ✓ VCO frequency calibration

- On pixel VCO oscillation frequency controlled by a PLL at the center of the chip (@ 640 MHz nominal)

- VCO design sensitivity of 1MHz/mV

- Spread of 40 MHz

- Noise measurements used to calibrate VCO frequencies for the whole matrix (~29 k VCOs)

- ✓ ToT vs Q calibration with testpulse

- At fixed charge, large ToT spread across the matrix due to local gain differences

- Non-linear calibration performed with integrated test pulse tool

R. Bolzonella et al 2024 JINST 19 P07021

# **Equalization and Calibration**

- ✓ Threshold equalization

- Threshold fine tuning at pixel level

- Noisy pixels detection

- On the whole matrix (~230 k pixels)

X. Llopart XII Front-End Electronics Workshop

- ✓ VCO frequency calibration

- On pixel VCO oscillation frequency controlled by a PLL at the center of the chip (@ 640 MHz nominal)

- VCO design sensitivity of 1MHz/mV

- Spread of 40 MHz

- Noise measurements used to calibrate VCO frequencies for the whole matrix (~29 k VCOs)

### ✓ ToT vs Q calibration with testpulse

- At fixed charge, large ToT spread across the matrix due to local gain differences

- Non-linear calibration performed with integrated test pulse tool

R. Bolzonella et al 2024 JINST 19 P07021

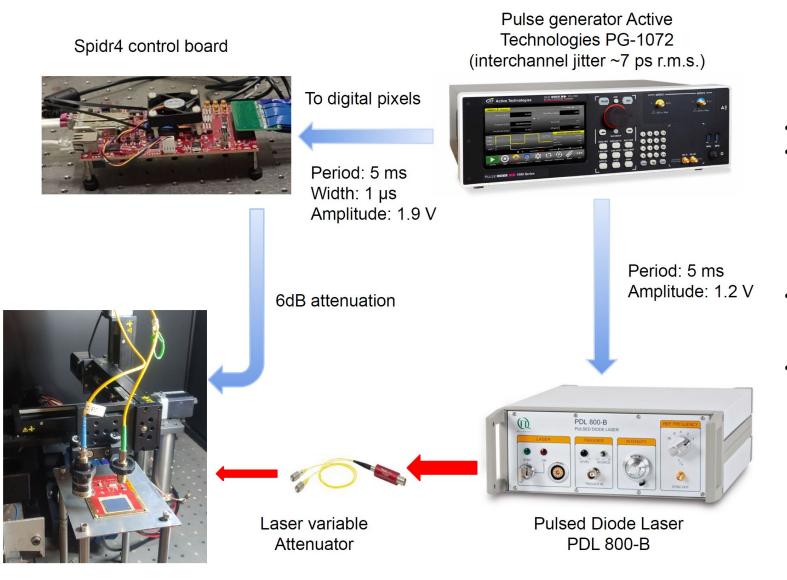

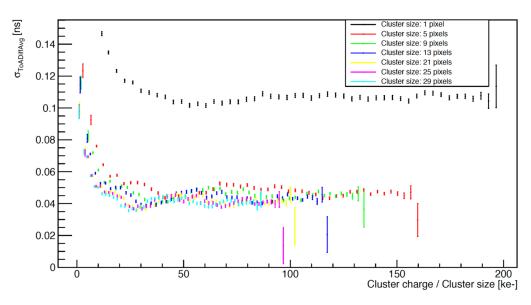

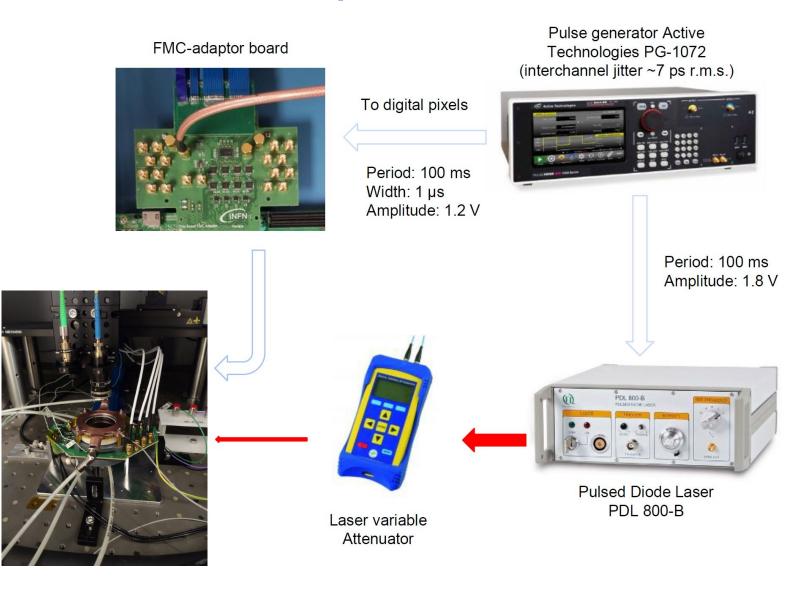

# Timing resolution measurements with Si sensor

- Spidr4 control board

- Timepix4:

- bonded to a 100 μm n-on-p Si sensor biased at -150 V

- metallization with holes pattern

- Courtesy of CERN and NIKHEF Medipix4/VELO groups

- Waveform generator

- input signal to digital pixels

- laser trigger

- Laser:

- 1060 nm

- variable attenuator

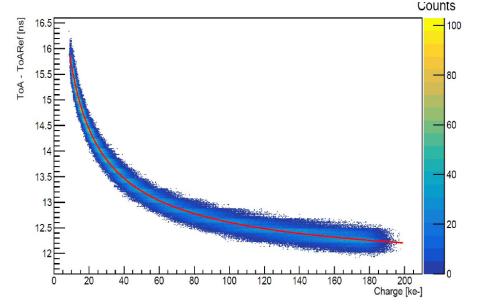

# Timing resolution measurements with Si sensor

- Laser focused using micro-collimator:

- spot size =  $77 \mu m$

- Laser spot in fixed position

- Measurements using variable laser attenuation, populating a wide charge range on each pixel

- Time walk corrected separately on each pixel

For each cluster (~30 pixels):

weighted average of ToA using charge as weights

cluster charge computed

Timing resolution after the reference signal contribution has been subtracted:

- $\sigma_t^{pixel} \sim 107 \pm 3 \ ps \ rms$   $\sigma_t^{cluster} \sim 33 \pm 3 \ ps \ rms$  (~ 30 pixels)

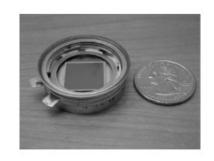

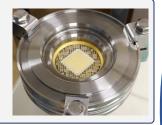

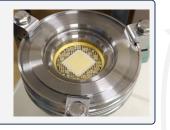

Ceramic carrier board designed by INFN and CERN and produced by Kyocera – first sample mid 2023

- Interface between inner/outer parts

- Custom Pin Grid Array (PGA) for I/O signals

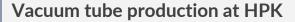

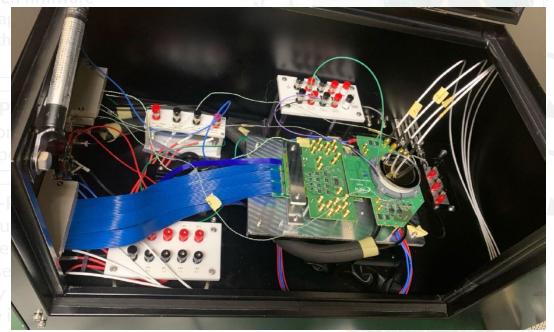

**Characterization of Timepix4 ceramic assemblies** at HPK with test setup build by INFN

October 2023

#### Vacuum tube production at HPK

- Multi-alkali S20 photocathode

- Microchannel plates

Jan-Feb 2024

Shipping of tubes from HPK to INFN for complete characterization

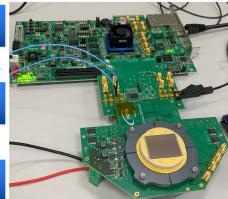

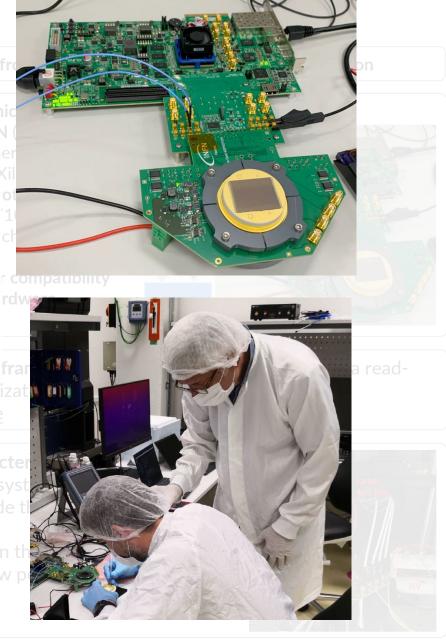

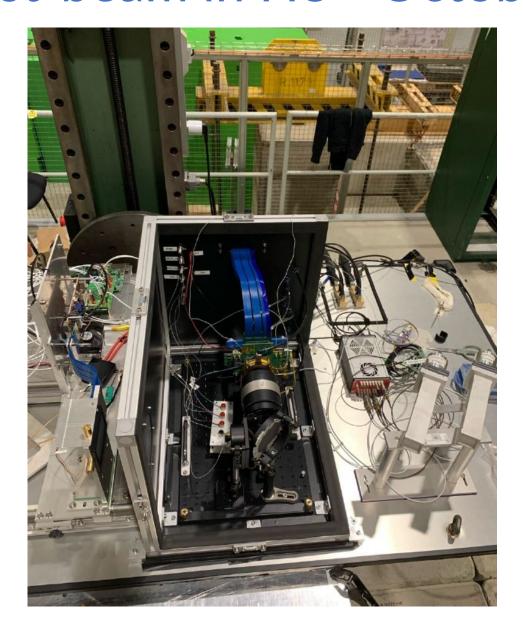

Complete electronics and DAQ system developed at INFN (IDAQ)

Based on commercial development kit AMD/Xilinx KCU105

Open firmware

**DataPix4**: a **C++ framework** for Timepix4 configuration, data readout, online visualization and analysis (developed at INFN)

Paper available

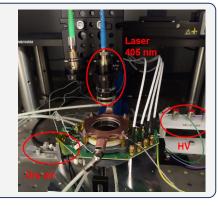

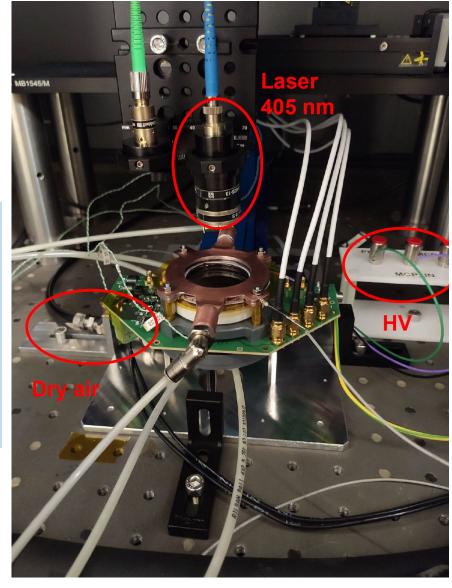

#### MCP-PMT characterization measurements

- Liquid cooling system to maintain stable temperature inside the tube

- Laser 405 nm

- Dry air fluxed in the dark box to decrease the internal dew point

Ceramic carrier board designed by INFN and CERN and produced by Kyocera – first sample mid 2023

- Interface between inner/outer parts

- Custom Pin Grid Array (PGA) for I/O signals

Shipping of tubes for

Complete electronic developed at INFN

Based on comme ment kit AMD/Xi

- Extensive tests performed at CERN and INFN labs

- Metrology, leak rate (EP-DT group), mechanical, thermal, Timepix4 planarity

- Timepix4 integration on ceramic carrier

- complete electrical of Timepix4 assembly on ceramic using IDAQ board

- Test-pulses measurements, to verify both test-pulse and data-readout

- High-speed links configuration

- Glueing and wire-bonding at CERN Bonding LabCeramic Lab

out, online visualizati

Paper <u>available</u>

MCP-PMT character

- Liquid cooling syst temperature inside the

- Laser 405 nm

- Dry air fluxed in t the internal dew r

Ceramic carrier board designed by INFN and CERN

- Multi-alkali S20 photocathode

- Peak QE >30% at 380 nm

- Microchannel plates

- 6 μm channel diameter (7.5 μm pitch)

- 50 mm diameter

- L/D = 50, typical open area ratio 60%

- Several variants for complete characterization

- 2-MCP stack and 3-MCP stack

- 1d 2d 3d end-spoiling

Commissioning of the complete tube test setup in January-February 2024 in Hamamatsu laboratories, with first tube sample

- Multi-alkali S20 photocathode

- Microchannel plates

Jan-Feb 2024

Shipping of tubes from HPK to INFN for complete characterizatio

### Complete electronics and DAQ system developed at INFN (IDAQ)

- Based on commercial development kit AMD/Xilinx KCU105

- Use standard protocols (UDP-IP over 1/10G eth)

- Open firmware

- Prompt availability and flexibility; works with both data-driven and frame-based modes

- Use standard protocols

- 1G ethernet for configuration data from controller

- 10G ethernet for detector data to storage

- Adapter card for compatibility with existing hardware, e.g. SPIDR4 system (Nikhef)

- Configuration based on IPbus

- Multi-board synchronization

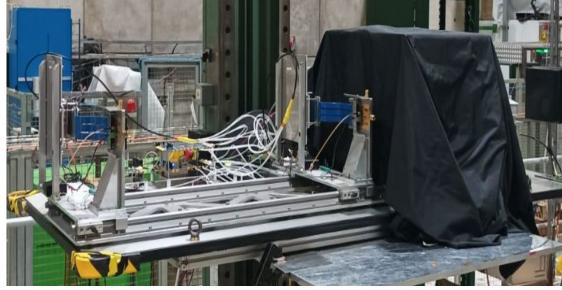

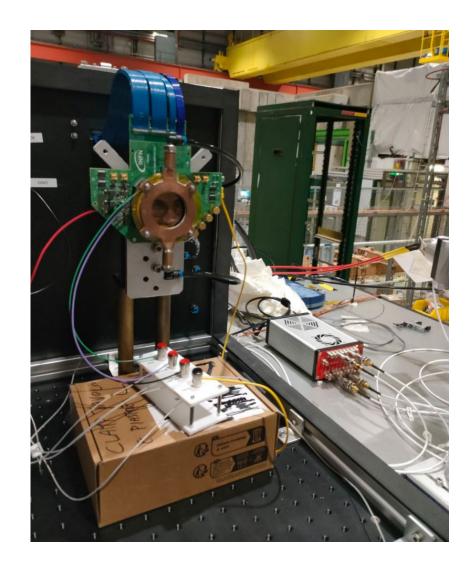

# Tube characterization setup

- Tube prototypes mounted on custom carrier board inside a lighttight box

- Liquid cooling system to maintain stable temperature inside the tube

- Copper cold finger (ceramic bottom part) plus copper ring (in contact with the quartz window)

- Tube temperature reaching about 0°C with cooling liquid temperature @ -10°C, and temperature increasing by 2°C when Tpx4 operating

- **Dry air** fluxed in the dark box to decrease the internal dew point

- DAQ system (IDAQ) outside the box with 1 m flat FMC cable connection

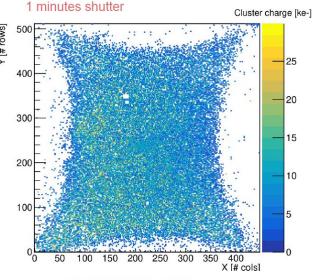

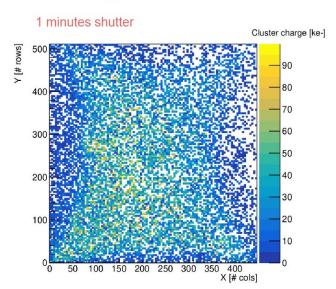

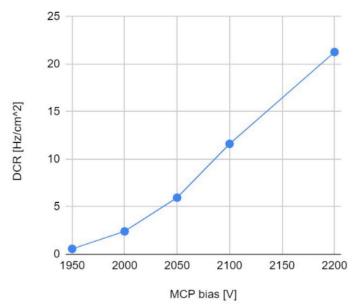

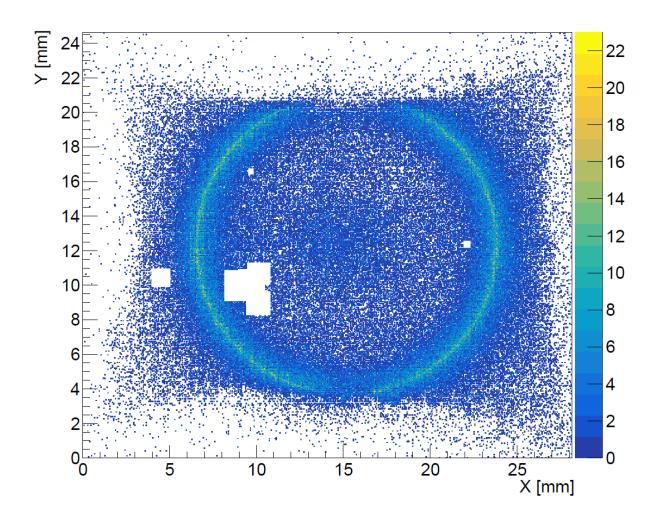

### DCR measurement

Dark Count Rate (DCR) and gain measurements performed on dark noise acquisitions

- Timepix4 threshold set at 1000 e-

- Several combinations of HV settings used for complete detector characterization

- Photocathode MCP\_in

- MCP\_in MCP\_out

- MCP\_out Timepix4

- Non-uniform dark count rate distribution

• Investigations ongoing (electric field distortion, gain differences and

MCP bending under study)

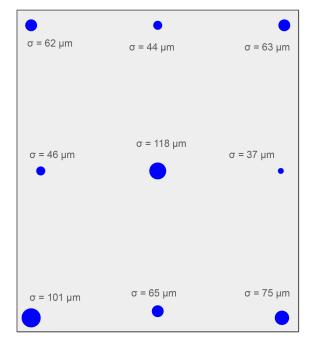

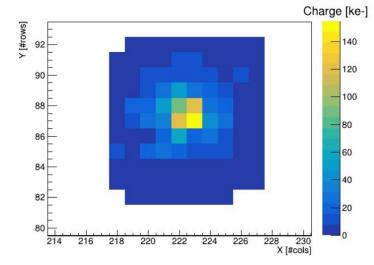

Dimension of laser clusters on different positions (with laser intensity fixed)

- Smaller clusters along sides: less gain leading to more pixels below threshold

- Position error lower than 50 μm → no field distortions

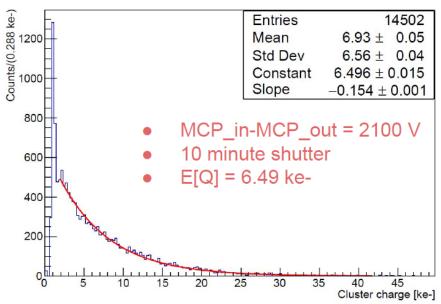

- PHK-MCP\_in = -75 V

- MCP\_in-MCP\_out = -2100 V

- MCP\_out-Tpx4 = -150 V

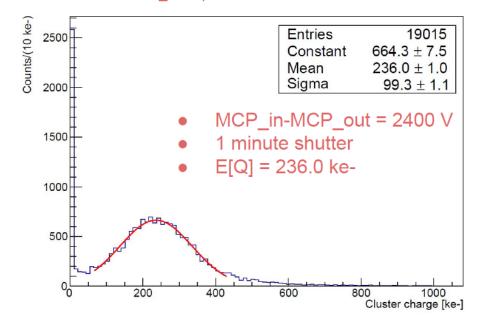

- PHK-MCP in = -75 V

- MCP\_in-MCP\_out = -2200 V

- MCP\_out-Tpx4 = -150 V

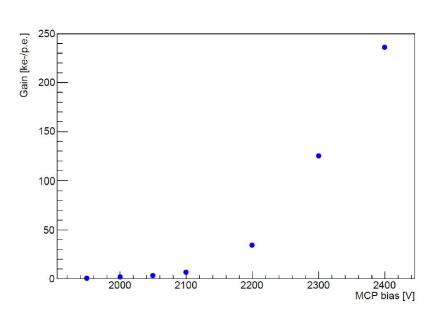

# Gain - cluster charge distribution

- Gain estimated by measuring cluster charge distribution in the central area of the matrix at different MCP voltages

- At low gain levels, exponential distribution: gain estimated as distribution average

- At high gain levels, peaks are expected to detach from the exponential distribution

- PHK-MCP\_in = -75 V

- MCP out-Tpx4 = -150 V

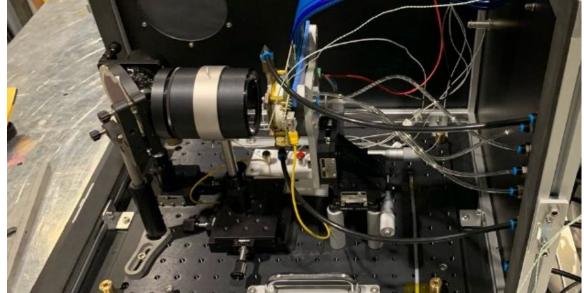

# Tube: timing resolution setup

Timepix4 controlled through either SPIDR4 or custom control board developed by INFN, located outside the box

#### Waveform generator

- input signal to digital pixels

- laser trigger

#### Collimated laser:

- 405 nm

- variable attenuator

#### Zaber motion setup

- 3D position regulation

- Few µm precision

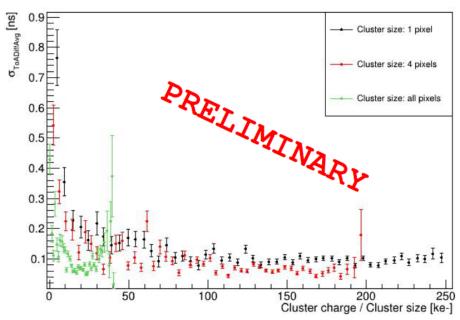

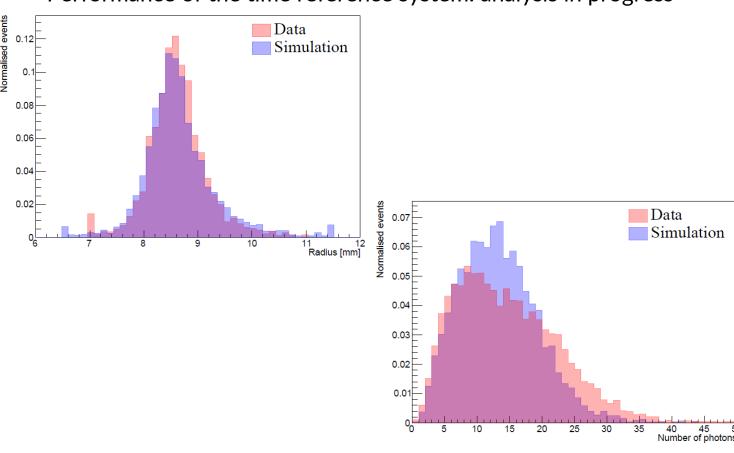

## Timing resolution - Single photon measurements

- High MCP gain and low electron cloud focusing:

- MCP\_in-MCP\_out = -2500 V

- MCP\_out-Tpx4 = -100 V

- Single photon regime ~ 1 single-photon event each 10 laser pulses

- Clusters with charge peaked in 3-4 pixels, with low charge halos

- Reference signal contribution estimated to be approximately 70 ps

- After subtraction of reference signal contribution, single pixel resolution reaches a plateau at 95 ps

- Resolution improving up to 65 ps considering clusters (4 pixels or more)

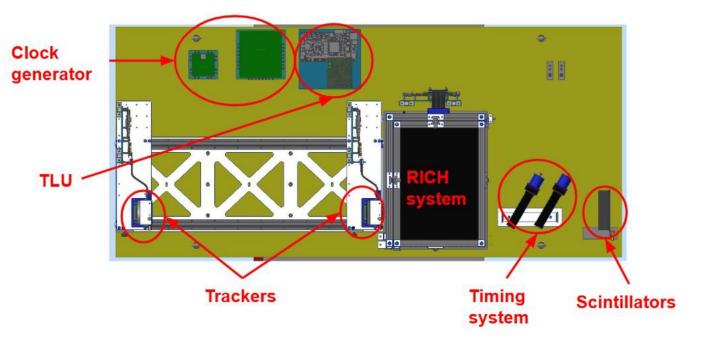

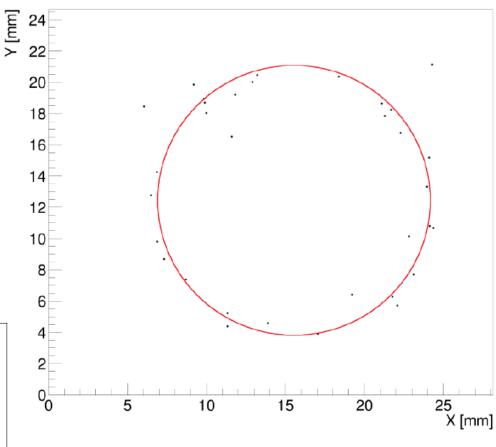

- Tracking system (2 Timepix4 b.b. to 300 μm thick p-on-n Si)

- RICH: solid Cherenkov radiator and optics setup focus ring on single tube

- Timing system: 2 Cherenkov detectors to provide timing reference (read-out by PicoTDC) + 2 scintillators for beam alignment

- Custom Trigger Logic Unit (TLU) to use the same spill extraction signal as shutter signal on the 3 Timepix4 + Common external reference clock

- Beam: ~80 % protons, ~20 % pions, ~1 % muons

- Cherenkov rings observed at different HV settings on the tube

- Track correlation between the tracking system and the tube

- Performance of the time reference system: analysis in progress

### Another test beam is scheduled in November 2025

- Optimized working points and new calibration measurements for the trackers and 4DPHOTON

- Implementation of timing reference in the analysis

- We aim to measure a timing resolution close to the values obtained in the laboratory < 100 ps</li>

### Conclusion

A novel single-photon detector has been designed, produced and tested

- Vacuum tube with MCP and Timepix4 CMOS ASIC as anode

- Complete integration of sensor and electronics, on-detector signal processing and digitization with large number of active channels (~230 k pixels),

- Produced by Hamamatsu Photonics

### Measurements on first prototypes

- Gain and average DCR ( $\sim 20~Hz/cm^2$ ) as expected

- Non-uniform DCR distribution under study

- <100 ps time resolution per single photon</li>

- Best result so far: 65 ps r.m.s. for single photons

- Position resolution <55 μm</li>

# Next steps and future plans

- Complete prototypes characterization and improve electronics read-out settings

- High rates of the detector impacted by ceramic package induced features (insertion losses, power filtering, heat dissipation): will investigate effect of adding decoupling capacitors

- New tubes being produced by Hamamatsu to mitigate non-uniformity

- First samples produced: will be delivered soon

- **Future improvements** for use in HEP harsh environments

- 1. Radiation hardness

- Use rad-hard-by-design ASIC (plus rad-hard serializers)

- 2. High-rate capability and detector lifetime

- Improve current MCP technology

- 3. Timing resolution

- Use ASIC with smaller TDC bin size and lower front-end jitter (e.g. LA-Picopix, rad-hard, 30-40 ps bin size, low jitter, high

This project has received funding from the European Research Council (ERC) under the European Union's Horizon 2020 research and innovation programme (Grant Agreement No. 819627, 4DPHOTON, P.I. M. Fiorini)

# **Spares**

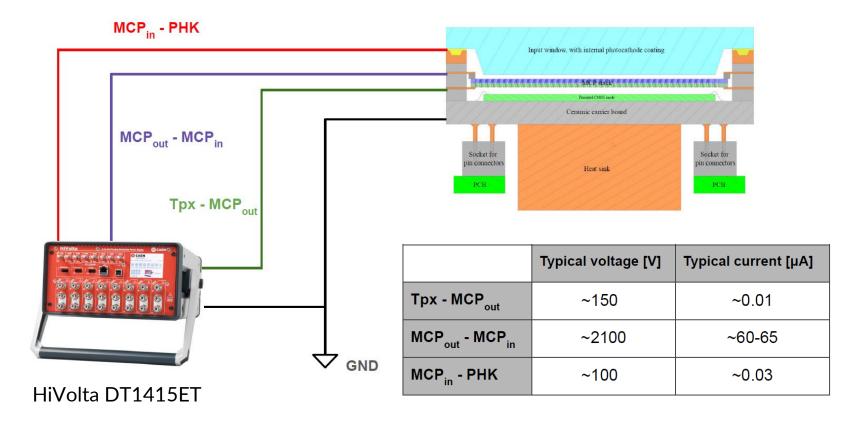

# Setup HV distribution

Several HV parameters set between the different elements during device characterization

|                                 |                           |                | Timepix3 (2013)                                 | Timepix4 (2019)                              |  |

|---------------------------------|---------------------------|----------------|-------------------------------------------------|----------------------------------------------|--|

| Technology                      |                           |                | 130nm – 8 metal                                 | 65nm – 10 metal                              |  |

| Pixel Size                      |                           |                | 55 x 55 μm                                      | 55 x 55 μm                                   |  |

| Pixel arrangement               |                           |                | 3-side buttable<br>256 x 256                    | 4-side buttable<br>512 x 448                 |  |

| Sensitive area                  |                           |                | 1.98 cm²                                        | 6.94 cm <sup>2</sup>                         |  |

| Readout Modes                   | Data driven<br>(Tracking) | Mode           | TOT and TOA                                     |                                              |  |

|                                 |                           | Event Packet   | 48-bit                                          | 64-bit                                       |  |

|                                 |                           | Max rate       | 0.43x10 <sup>6</sup> hits/mm <sup>2</sup> /s    | 3.58x10 <sup>6</sup> hits/mm <sup>2</sup> /s |  |

|                                 |                           | Max Pix rate   | 1.3 KHz/pixel                                   | 10.8 KHz/pixel                               |  |

|                                 | Frame based<br>(Imaging)  | Mode           | PC (10-bit) and iTOT (14-bit)                   | CRW: PC (8 or 16-bit)                        |  |

|                                 |                           | Frame          | Zero-suppressed (with pixel addr)               | Full Frame (without pixel addr)              |  |

|                                 |                           | Max count rate | ~0.82 x 10 <sup>9</sup> hits/mm <sup>2</sup> /s | ~5 x 10 <sup>9</sup> hits/mm²/s              |  |

| TOT energy resolution           |                           |                | < 2KeV                                          | < 1Kev                                       |  |

| TOA binning resolution          |                           |                | 1.56ns                                          | 195ps                                        |  |

| TOA dynamic range               |                           |                | 409.6 μs (14-bits @ 40MHz)                      | <b>1.6384 ms</b> (16-bits @ 40MHz)           |  |

| Readout bandwidth               |                           |                | ≤5.12Gb (8x SLVS@640 Mbps)                      | ≤ <b>163.84 Gbps</b> (16x @10.24 Gbps)       |  |

| Target global minimum threshold |                           |                | <500 e <sup>-</sup>                             | <500 e⁻                                      |  |

# PicoPix specifications

https://indico.cern.ch/event/1456663/contributions/6184370/attachments/2954032/5193546/PicoPix\_DRD4.pdf

| Technology                                |                                             |          | 28nm – 10 metal                                                                                               |  |

|-------------------------------------------|---------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------|--|

| Pixel Size                                |                                             |          | 49.5μm (tbc)                                                                                                  |  |

| Pixel arrangement                         |                                             |          | 3-side buttable 256 x 256                                                                                     |  |

| Sensitive area                            |                                             |          | 1.606 cm <sup>2</sup> (tbc)                                                                                   |  |

|                                           | Mode                                        |          | TOT and TOA on Master only                                                                                    |  |

|                                           | Event Packet                                | Sorted   | 24-bit, 34-bit or 72-bit                                                                                      |  |

| Data driven<br>(Tracking)                 | Event Packet                                | Unsorted | 72-bit RAW, 72-bit fine time, Jumbo RAW, Jumbo fine time                                                      |  |

| (114611118)                               | Max rate @ pixel matrix                     |          | 5.12x10 <sup>9</sup> events/chip                                                                              |  |

|                                           | Max average pixel rate                      |          | <78 KHz                                                                                                       |  |

|                                           | Max single pixel rate                       |          | <20 MHz/pixel                                                                                                 |  |

|                                           | On-pixel clustering                         |          | Master + surrounding 8-bit hitmap for 3x3 events                                                              |  |

|                                           | On-pixel large cluster filter               |          | Asynchronous filtering for events larger 3x3                                                                  |  |

|                                           | On-pixel sub-pixel resolution               |          | 256x256 → 512x512                                                                                             |  |

| Pixel clustering mode (can be turned off) | On-pixel TDC                                |          | Shared for 4 pixels. TOA + TOT of Master only DCO autocalibration on-chip →~40ps bin(~11.5ps <sub>rms</sub> ) |  |

|                                           | Periphery cluster sorting and framing       |          | YES                                                                                                           |  |

|                                           | SuperPixel Counter                          |          | 4x12-bit counters → TOT on all pixels or photon counting                                                      |  |

|                                           | Periphery absolute on-chip time calibration |          | YES                                                                                                           |  |

| Frame-based                               |                                             |          | YES zero-suppressed. 12-bit pixel counters (PC or iTOT) 72-bit PC or iTOT                                     |  |

| Readout bandwidth                         |                                             |          | Up to 4x @12.8 or 25.6 Gbps (tbd)                                                                             |  |

| Radiation tolerance                       |                                             |          | YES. TMR design                                                                                               |  |

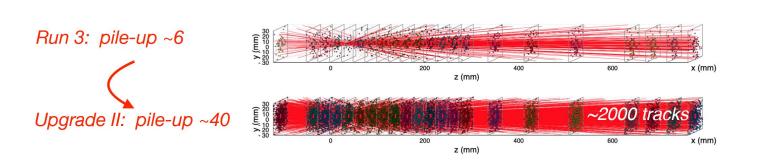

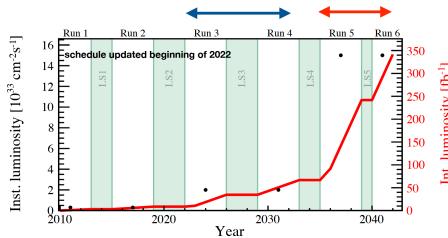

# LHCb Upgrade II

The LHCb experiment is planning a high-luminosity upgrade, targeting a luminosity of  $1-2 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>

The RICH detector faces significant challenges, as it must achieve performance comparable to (or better than) that of Run 2-3 PID, but under much harsher conditions

#### **Key Requirements:**

- Single-photon sensitivity with high quantum efficiency (QE), particularly in the green/red-shifted spectrum

- Photon hit density reaching approximately 10 MHz/mm<sup>2</sup>, assuming the current detector geometry and scaling with luminosity

- High granularity, ensuring channel occupancy <25%, with pixel sizes around 1×1 mm<sup>2</sup>

- Excellent time resolution, with a target of <100 ps r.m.s. per single photon

- Radiation hardness, requiring tolerance up to ~2 Mrad TID, ~3×10<sup>31</sup> 1 MeV neq/cm<sup>2</sup>, and ~1×10<sup>13</sup> HEH/cm<sup>2</sup>

- No straightforward solution currently available for RICH photodetectors.

State-of-the-art photodetectors do not fully meet the requirements for long-term operation at the RICH detector plane, considering the full experiment lifetime (equivalent to 300 fb<sup>-1</sup> integrated luminosity) under the present detector geometry

Upgrade I

Upgrade II

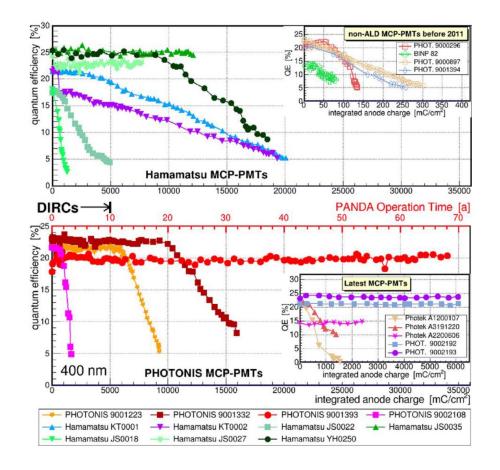

### **MCP-PMT limitations**

- MCP-PMT lifetime limited by the integrated anode charge, which leads to a strong QE reduction

- From 0.2 C/cm^2 to >30 C/cm^2 in recent years thanks to ALD

- With the expected photon hit rate (~10 MHz/mm2), assuming a 10^4 gain (very conservative), and an operation of 10 years with 25% duty cycle we have:

- Total IAC ~120 C/cm^2

- Anode current density ~2 μA/cm<sup>2</sup>

- ALD coating is based on the deposition of resistive and/or secondary emissive layers (could tune MCP properties)

- Reported adverse effects on saturation current on some model with ALD

https://www.sciencedirect.com/science/article/pii/S016890022 3000372?via%3Dihub