# The AdvCam project: Designing the future cameras for the Large-Sized Telescopes of the Cherenkov Telescope Array Observatory

C. Arcaro on behalf of the CTAO-LST project Istituto Nazionale di Fisica Nucleare (INFN), Padua, Italy

#### **ABSTRACT**

An international collaboration composed of Italian, Japanese, Spanish and Swiss institutes, is developing the advanced camera (AdvCam), the next-generation camera for Imaging Atmospheric Cherenkov Telescopes (IACTs), designed specifically for the Large-Sized Telescopes (LSTs) of the Cherenkov Telescope Array Observatory (CTAO). AdvCam incorporates cutting-edge Silicon photomultipliers and a fully digital readout system, setting new standards for performance and efficiency.

The AdvCam will feature four times more channels than the existing PMT-based camera installed at LST-1. Covering the same field of view, this upgraded camera design enables finer image resolution and significantly improves the angular precision and background noise rejection. To cope with the increase in number of channels, many technological challenges are being tackled, from low-power and high-speed integrated chip design to real-time data processing on hardware accelerators.

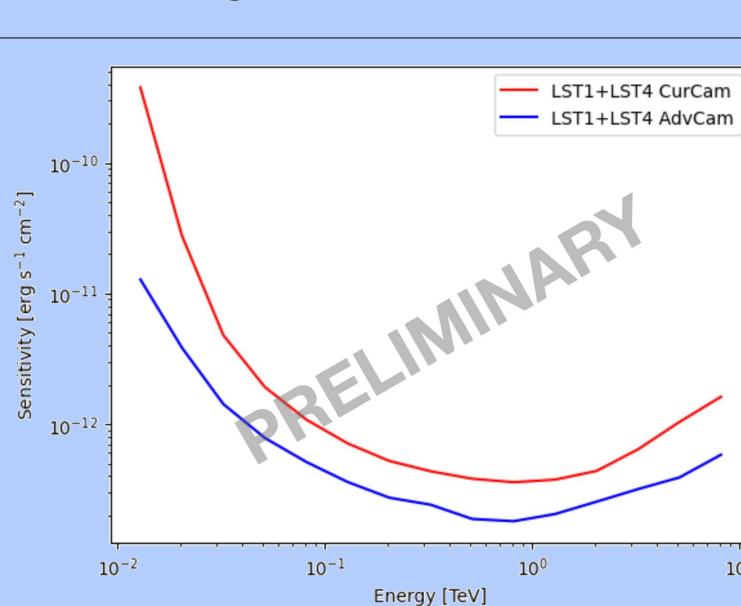

This technological leap will lower the energy threshold by allowing telescopes to operate at a lower minimum signal level and providing brighter images. The increase in effective area, angular resolution and energy resolution of this new-generation of IACTs will enhance CTAO's sensitivity, unlocking new potential for gamma-ray astronomy. In this work, we present the performance of the AdvCam's core building blocks and its innovative architecture capable of enabling unprecedented triggering capabilities. We also showcase the latest performance results based on Monte Carlo simulations that have been tuned to reflect the latest stages of the on-going technological developments, highlighting the transformative capabilities of this next-generation IACT camera.

### 1) ADVANCED SIPM CAMERA

- ★ SiPM pixels

- ☐ Higher sensitivity over larger wavelength range

- ☐ Smaller pixels (from 0.1° to 0.05°)

- ☐ Higher Resolution

★ Fully digital readout

- Digital trigger

- ☐ Real-time processing capabilities

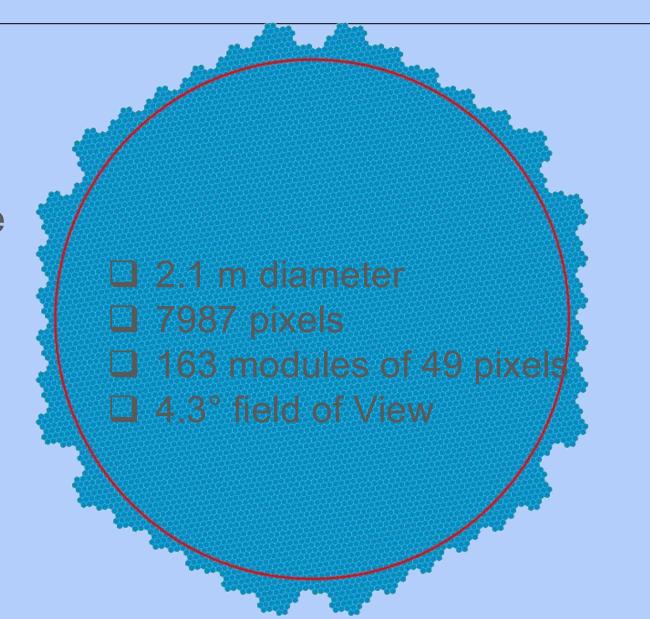

Fig.1: Scheme of the camera-pixel layout.

## 2) CAMERA PIXELS

- ★ Hexagonal SiPMs equipped with hollow light guides

- ★ Arranged as flowers with six neighboring and one central pixel

- ★ Regrouped to superflowers (7 flowers)

- ★ S13360-3050/75CN-UVE technology

- ☐ Fast response

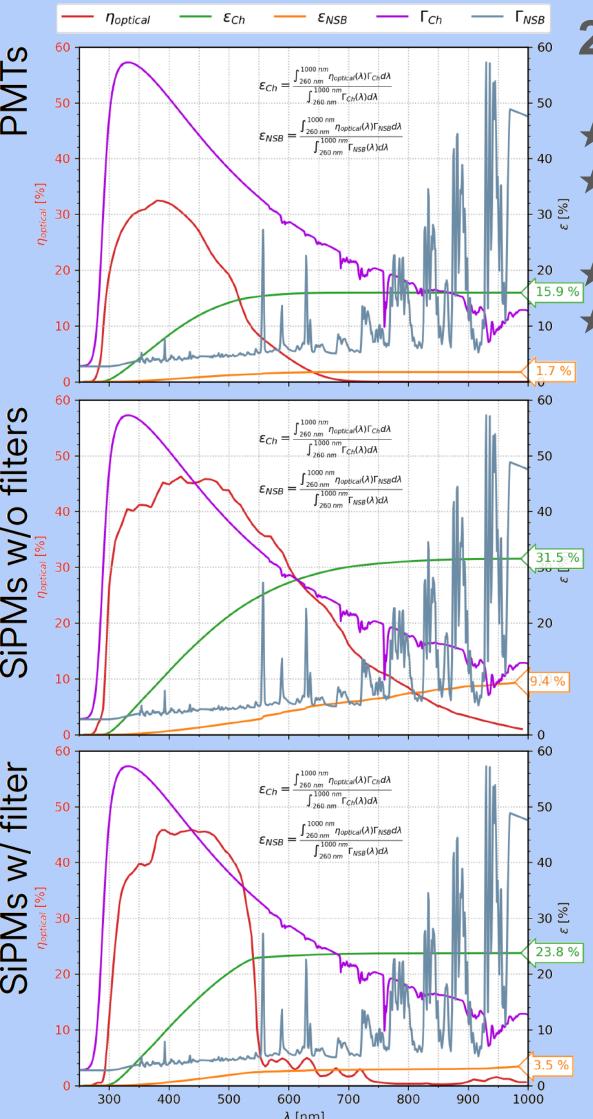

- ☐ 2 times more sensitive to Cherenkov light than PMTs

- ☐ 5.5 times more sensitive to NSB than PMTs

- ☐ Filtering coating applied to sensor surface to reduce sensitivity to NSB at longer wavelengths

Fig.2: Optical efficiency (red) of PMTs (top) and SiPMs without (center) and with (bottom) to Cherenkov light (purple) and NSB (blue). The detection efficiencies for Cherenkov light (green) and NSB (orange) are also shown.

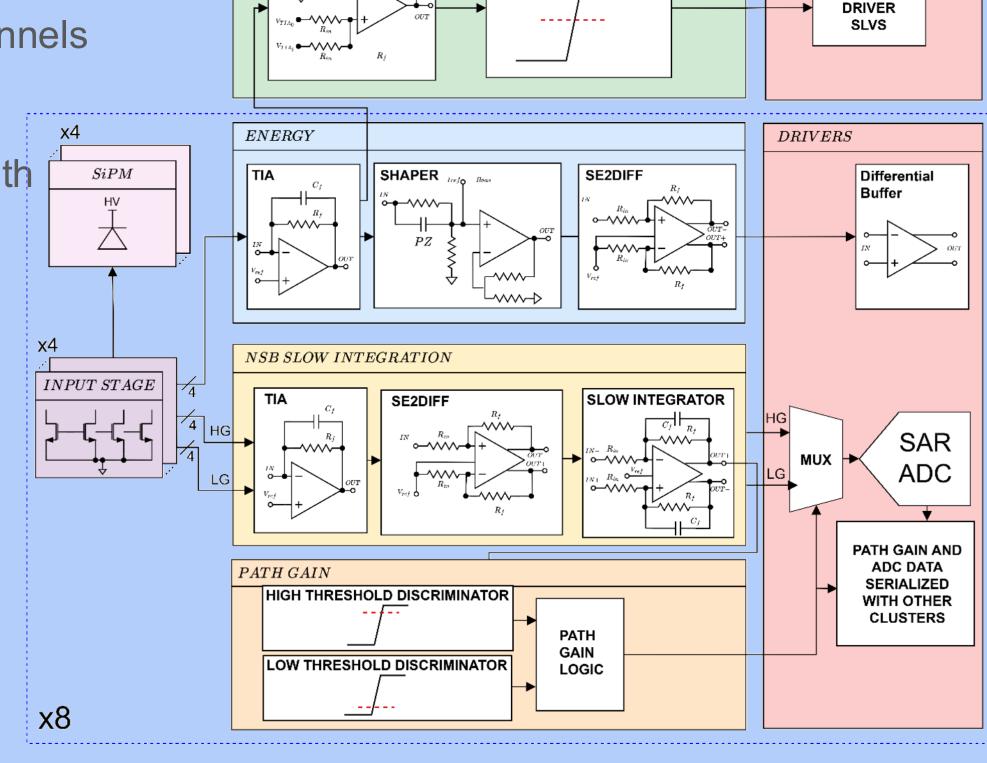

### 3) PRE-AMPLIFYING ASIC

- ★ Active summation of 4 input channels

- ★ Single photo-electron resolution

- **★** SNR > 5

- ★ Dynamic range up to 250 p.e. with < 5% linearity

- ★ Pulse FWHM < 5 ns

- **★** NSB rate monitoring

- ★ Summation trigger of 7-pixel flower

**VOLTAGE COMPARATOR**

Fig.4: Architecture of the PRESSEC ASIC

DRIVER TRIGGER

# 4) FRONT-END BOARD

- ★ Fully digital architecture

- ★ Goal is to minimize data transfer inside camera

- ★ Customized FADC ASIC with goal to improve power consumption

- ★ FPGA (KU11P)

- ☐ L1 Trigger algorithm

- Data storage

- ☐ 10 GbE RDMA DAQ

- **★** White rabbit

- ☐ Timing synchronization

- ★ Neighbor's connections ★ Small FPGA (AU7P)

- Services

# Fig.5: Scheme of the FEB.

# 5) PERFORMANCE

★ LST1-4 stereo reconstruction comparison

☐ Improvement in sensitiviy with the AdvCam thanks to replacement of the PMTs by SiPMs, which increase the sensitivity to Cherenkov light, but also by the higher image granularity.

Fig. 6: Preliminary results of sensitivity comparison.

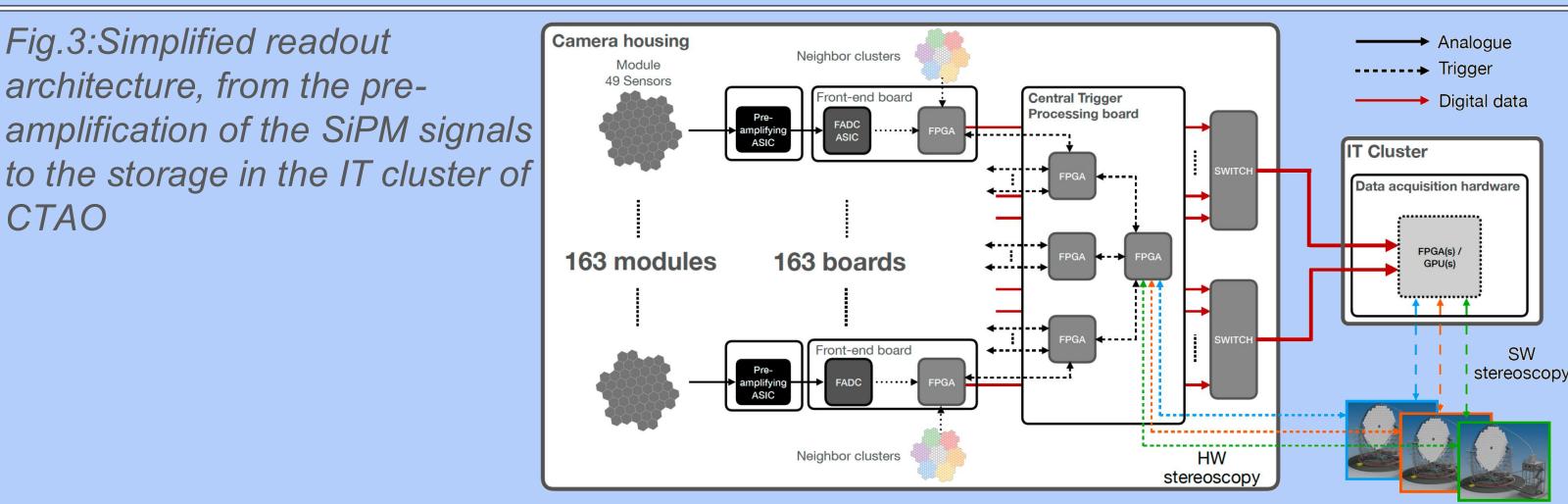

## 3) READOUT ARCHITECTURE

★ Pre-amplifying ASIC

Fig.3:Simplified readout

architecture, from the pre-

- ★ Front-end board

- ☐ Condition, amplify and digitize the sensor signals

- ☐ L1 trigger based on digital sum and threshold performed via FPGA

- ★ Central Trigger processing (CTP) board

- ☐ Manage internal (local) and external (L2 stereoscopic) trigger signals based on threshold

- NSB/shower discrimination

- **★** DAQ

CTAO

- Event building

- ☐ Provide software stereo trigger and event tagging

### REFERENCES

- [1] Heller et al., ICRC (2025)

- [3] Heller et al., ICRC (2023)

- [2] L. Burmistrov et al., ICRC (2025)

- [4] Marini et al., IEEE Trans. Nucl. Sci., (2025)

### **ACKNOWLEDGEMENTS**

https://www.lst1.iac.es/acknowledgements.html