# SODA, the Time Distribution System for PANDA

M. Kavatsyuk KVI, University of Groningen

for the PANDA collaboration

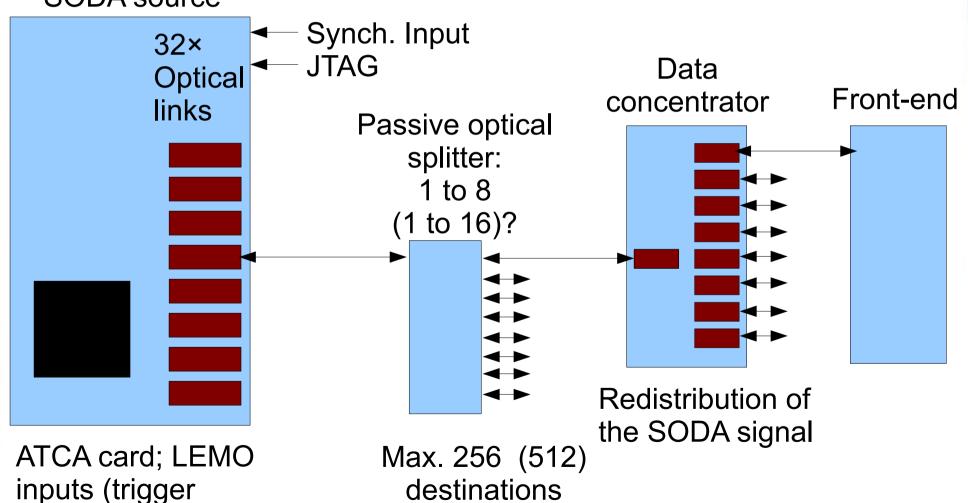

## **SODA Architecture**

Original idea: Igor Konorov [1. Konorov et al., NSS/MIC Conf. Rec., 2009 IEEE, DOI 10.1109/NSSMIC.2009.5402172]

**SODA** source

signal for tests)

2

## SODA Functionality SODA Source

- Distribution of the clock and synchronisation signals (burst start/end)

- Synchronisation with triggered DAQs for test experiments (trigger input to the SODA source, however, not trigger output)

- Distribution of a slow-control information; JTAG interface to data concentrators

- Receive slow-control data from the data-concentrators

## **SODA Functionality**

## Passive optical splitter

## **Functionality:**

Redistribution of the SODA signal to 8 (16, untested?) destinations.

## **Advantages:**

- Low jitter

- Low cost

## <u>Disadvantages:</u>

- Complicated communication protocol (time-division multiplexing)

- Large latency of the slow-control feedback (due to the timedivision multiplexing)

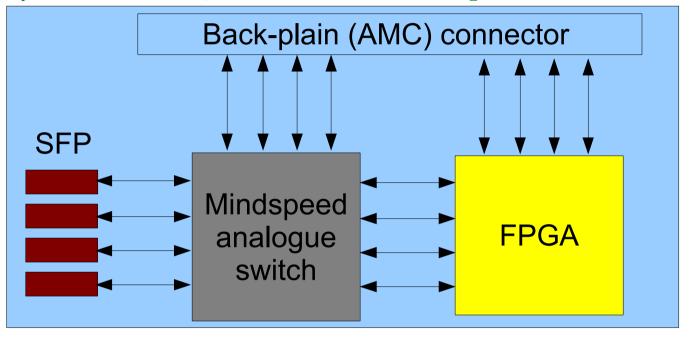

## Concept of a Data-Concentrator

Original idea: Igor Konorov [A. Mann et al., NSS/MIC Conf. Rec., 2010 IEEE, DOI 10.1109/RTC.2010.5750387]

- Analogue switch allows to broadcast SODA signal from one input SFP to all output SFPs, connected to a front-end. SODA signal can be broadcasted via back-plain to SFPs, located in the other modules.

- Advantage: Scalable system with low extra jitter

- Disadvantage: impossible to add extra slow-control information at the level of data-concentrator: All slow-control information has to be broadcasted by the SODA source (not possible to realize local watchdogs for the monitoring/reconfiguring FPGA-based front-end)

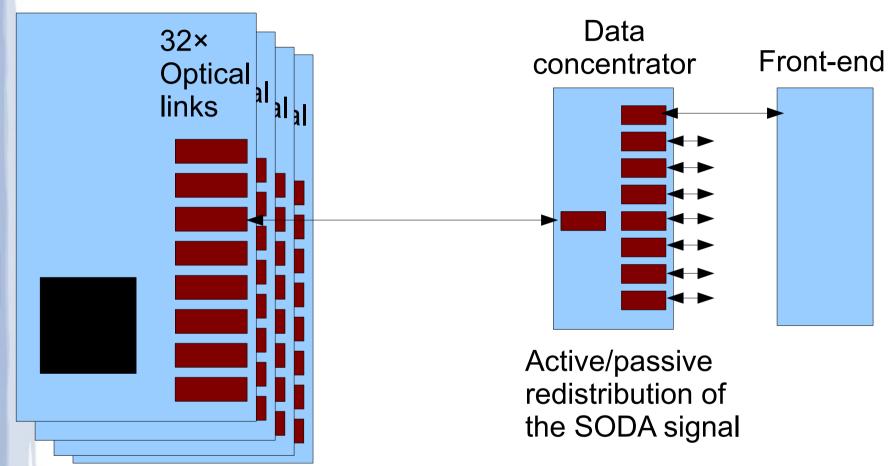

## **VI** Possible SODA Architecture

**SODA** source

#### **ATCA** cards:

- Master card (source)

- Redistribution cards

Redistribution done using back-plain (and analogue switches)

#### SODA receiver interface:

- Piggyback board

- Integrated into FEE

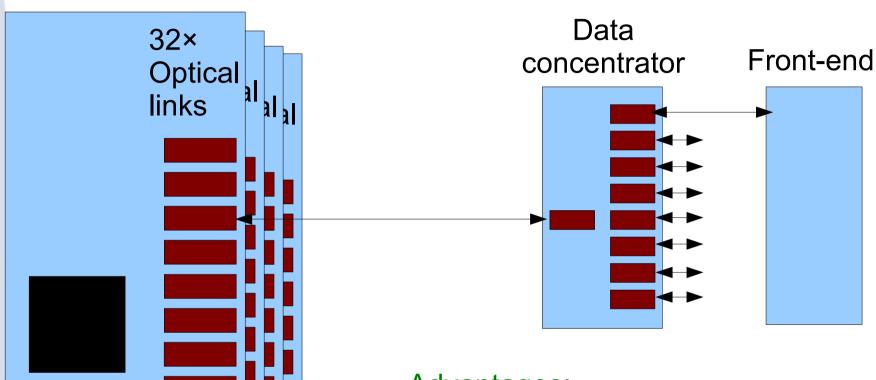

## (VI Possible SODA Architecture

**SODA** source

#### **ATCA** cards:

- Master card (source)

- Redistribution cards

Redistribution done using back-plain (and analogue switches)

#### Advantages:

- Simplified communication protocol

- High bandwidths and low latency available for a slow-control

- Larger resources available to implement slow control of the complete FEE

#### Disadvantages:

- Possibly higher jitter

- More expansive

## SODA, Open Questions

To optimize SODA architecture, we have to define:

- SODA protocol

- Unidirectional (source → FEE)

- Bidirectional (source ↔ FEE)

- Passive signal splitting (optical splitters)

- Active signal splitting (using Mindspeed switches)

- Measurement of the propagation time?

- Flow of a slow-control information

- Is the SODA the only network for a slow-control of the front-end

- Is it crucial to have a possibility of a local slow-control loops (at the level of FEE

← data-concentrator)

## Required input:

- Maximum tolerated jitter of the SODA signal for each subsystem

- Rough number of data-concentrators (directly connected to the SODA source) for each subsystem