## KO waveforms and microspill structure

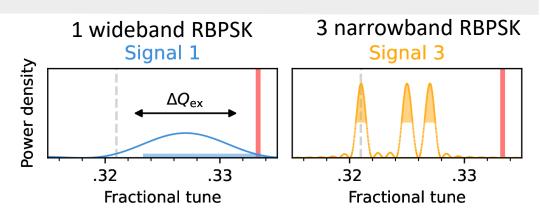

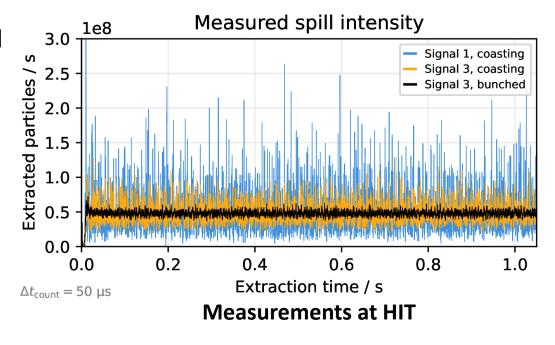

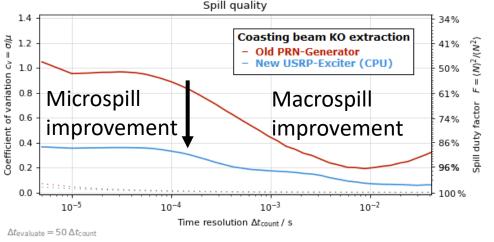

- The choice of excitation signal in KO extraction has a huge implication for the spill microstructure. Every facility has investigated this topic and came out with some optimal excitation signal. At GSI SIS-18, single RBPSK is used.

- PhD project (P. Niedermayer) started two years ago, one of the goal is finding the optimal waveform for microspill quality.

- With large scale particle simulations along with experiments at HIT and COSY, an answer was found → fixed frequency sinusoids are the best waveforms for microspill. Need to be mixed with noise waveform for a good extraction efficiency (Noise ++ excitation).

- Developments in the past year:

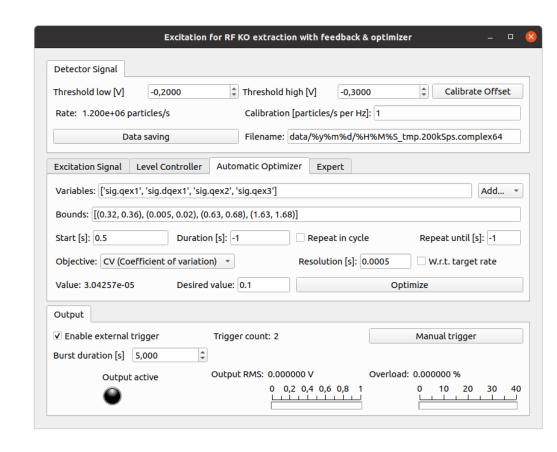

- Slow extraction is a sensitive non linear dynamics process, thus finding the optimal frequencies for sinusoids is dependent on precise extraction settings. Optimization routine built into excitation waveform generator

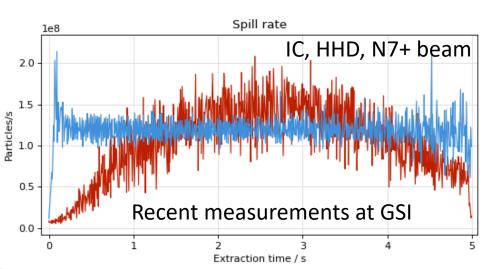

- The waveforms suitable for microspill often create undesired macrospill structure. Macrospill feedback

- 3. Noise ++ KO signal amplitude levels required is significantly higher compared to RBPSK. **Higher excitation power needed**

Microspill Optimization Rahul Singh 19.12.2023

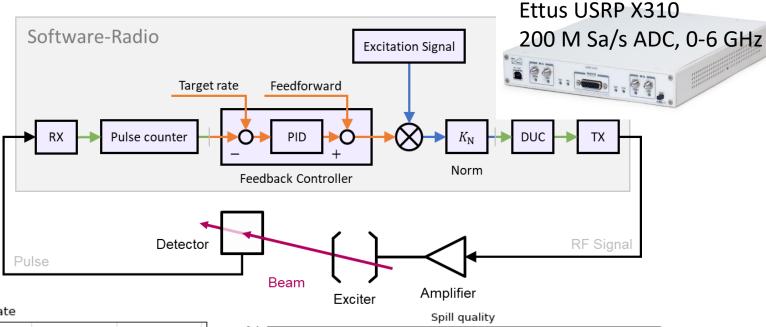

# Slow macrospill feedback using generic transceiver+CPU

- Pulse counter implemented in the FPGA.

Feedback logic and excitation signal generation implemented in the CPU. Loop latency minimized to ~ 1 ms

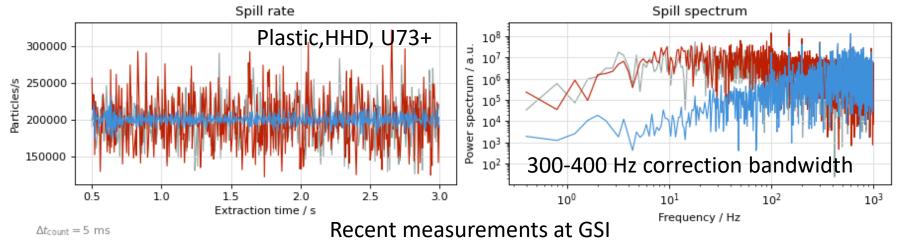

- Amplitude of excitation signal is controlled by a feedback loop for a flat macrospill (10 Hz).

### Detectors tested with so far:

- LGAD (HADES) Detector (at COSY)

- Ionisation Chamber (IC)

- SEM Grid

- Plastic Scintillator

- BLM at E-Septum

Microspill Optimization Rahul Singh 19.12.2023

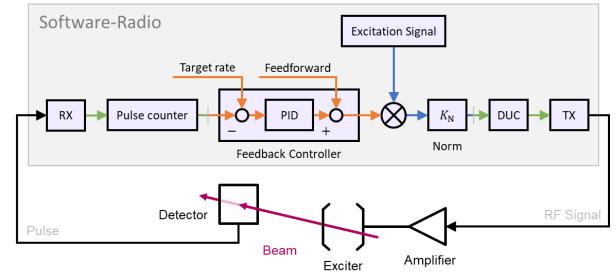

# Fast macrospill feedback with RFNoC (FPGA)

- FPGA-based feedback for low loop latency

- Project with support from COSY/HESR

- Intense exchange with experts (GRCon23)

- Optimized parameters (buffers, package sizes, ...) ~ 30 μs latency achieved

- → Pre-recorded signal played back from FPGA (replay block)

#### CPU based Feedback

FPGA Feedback with high latency control parameters

FPGA feedback with low latency control parameters

Microspill Optimization Rahul Singh 19.12.2023

## Summary

- A spill optimization system is developed → improvement of spill quality by generating optimal excitation waveforms. An integrated optimizer routine assists with this procedure.

- Two feedbacks (CPU and FPGA based) are implemented to tackle macrospill shape. They control the excitation signal amplitude based on a variety of particle intensity detectors. Many detectors have been tested.

- The power required for new waveform (Noise ++) is higher than RBPSK signal. Requires knock out (KO) power amplifier upgrade for usage with highest rigidity beam.

- System is available for usage

THANK YOU to many GSI, COSY and HIT colleagues!

Microspill Optimization Rahul Singh 19.12.2023 5