# **SPADIC**

2.2B: Test Results

3.0: ADC

Dr. Michael Ritzert

2023-11-08 CBM-TRD Retreat

# **SPADIC 2.2B Testing**

(2<sup>nd</sup> Round of Testing)

#### **Test Procedure**

- Test procedure:

- 1) Establish link to SPADIC.

- 2) Inject a sine curve in all channels in parallel.

- 3) Read out and analyze.

- ~ 45 seconds / chip

- Criteria for a "good" channel:

- Good fit to a sine curve

- Good gain

- Criteria for a good chip: ≥ 30 good channels.

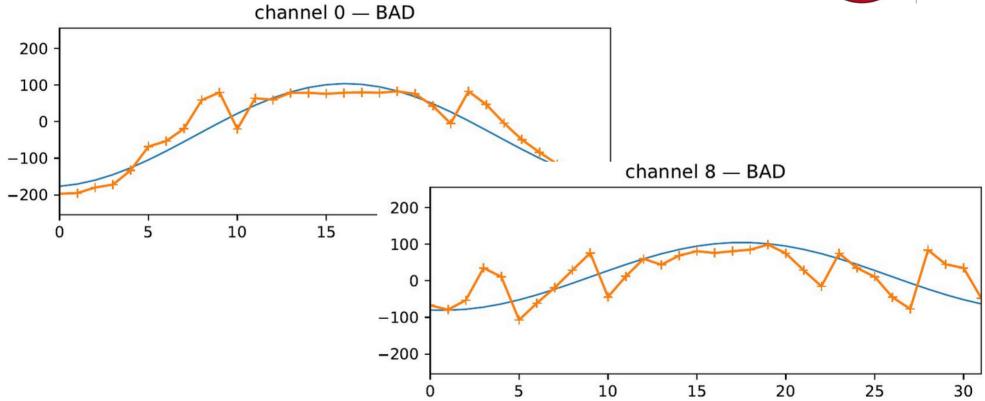

#### **Very Bad Sine Curves**

SPADIC

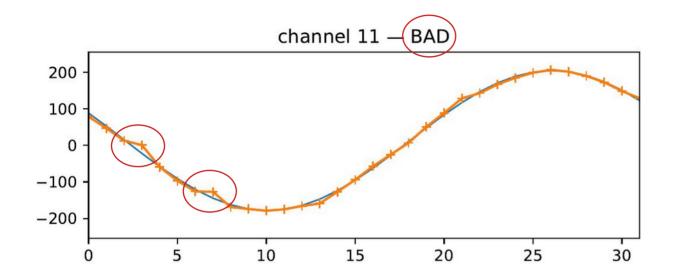

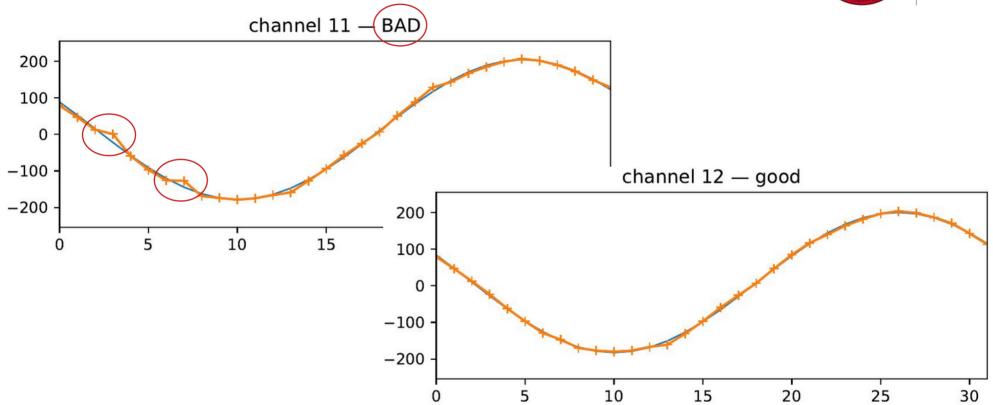

#### **Good / Bad Sine Curve**

5 / 23

#### **Good / Bad Sine Curve**

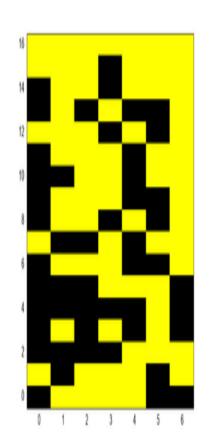

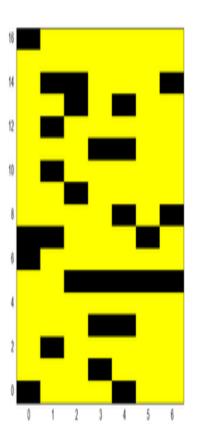

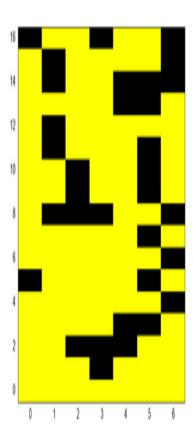

# **Results by Tray**

- by position in tray.yellow: good

- 3 trays with 7×17 chips each= 357 chip tested.

- 2<sup>nd</sup> and 3<sup>rd</sup> tray: better yield.

- ⇒ I learned when it's worth to re-try a chip.

Many "bad" chips are good on the second attempt.

- ⇒ The test setup is not super stable.

- Test results per chip available.

2023-11-08

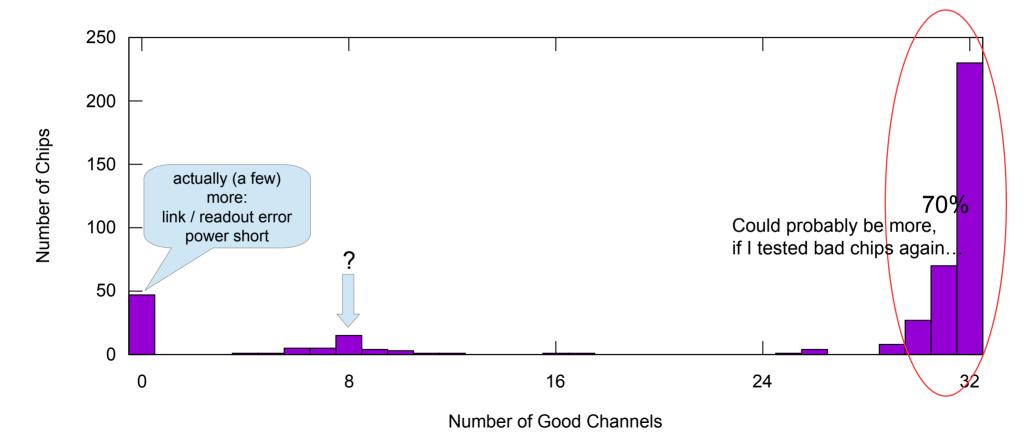

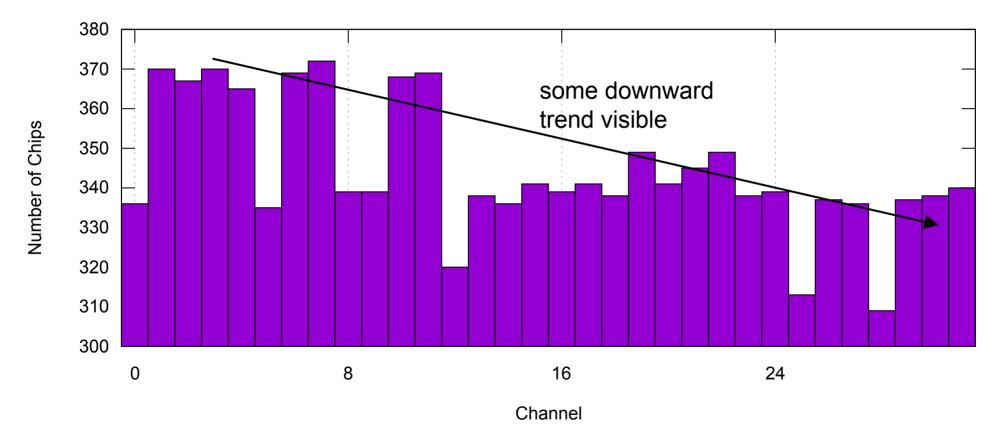

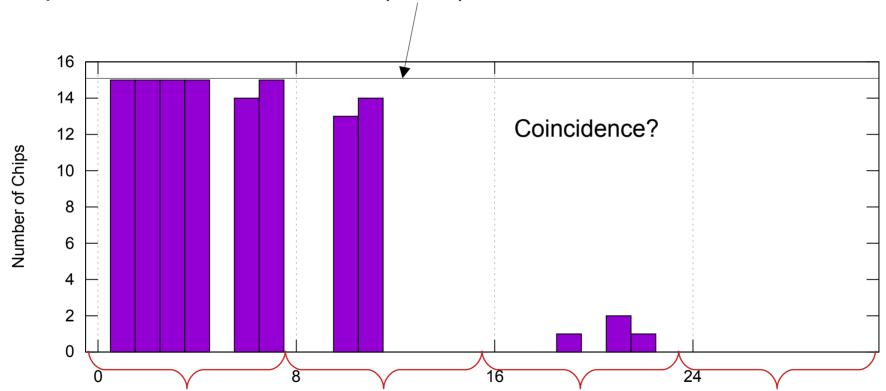

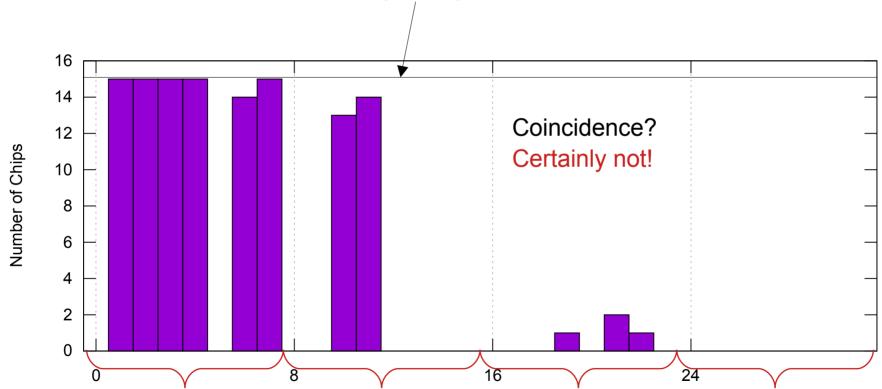

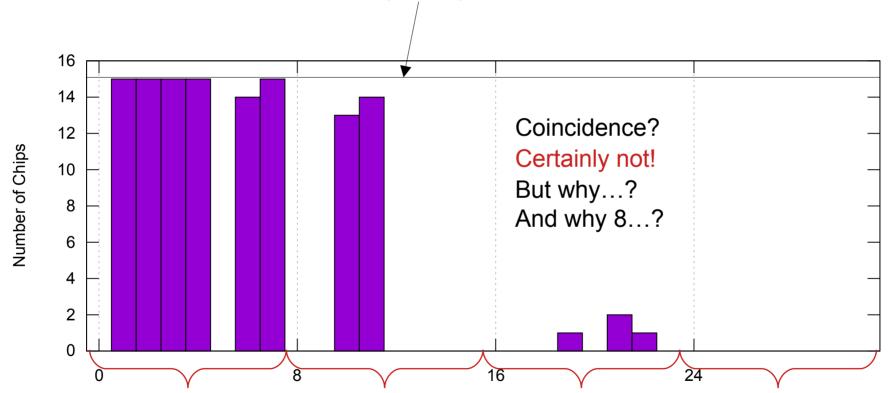

#### **Number of Good Channels / Chip**

**SPADIC**

8 / 23

For Chips with 8 Good Channels (*n*=15)

analog: 4 identical blocks of 8 channels

2023-11-08

UNIVERSITÄT **HEIDELBERG SEIT 1386**

For Chips with 8 Good Channels (*n*=15)

analog: 4 identical blocks of 8 channels

For Chips with 8 Good Channels (*n*=15)

analog: 4 identical blocks of 8 channels

# **SPADIC 3 Design**

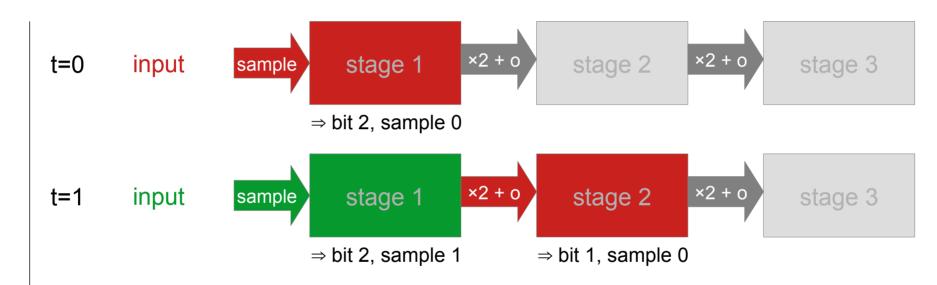

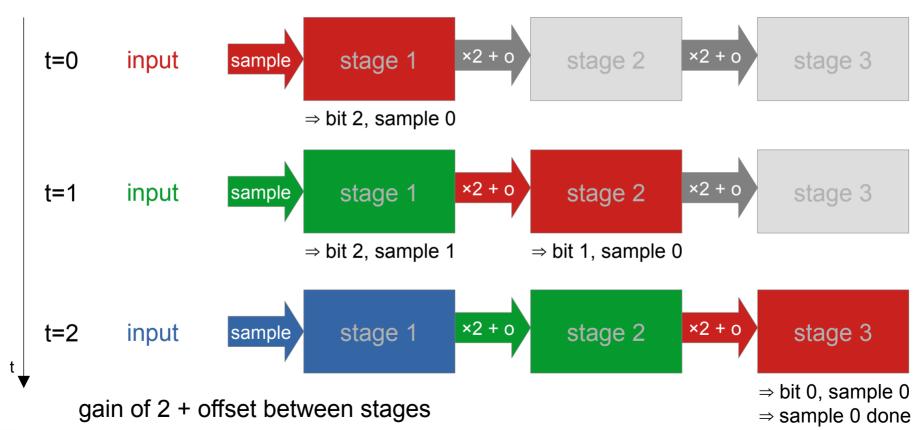

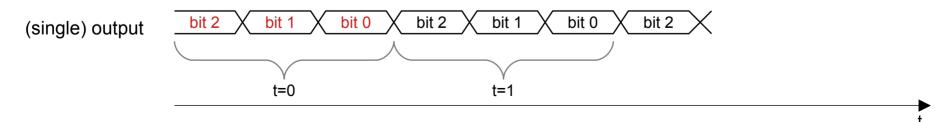

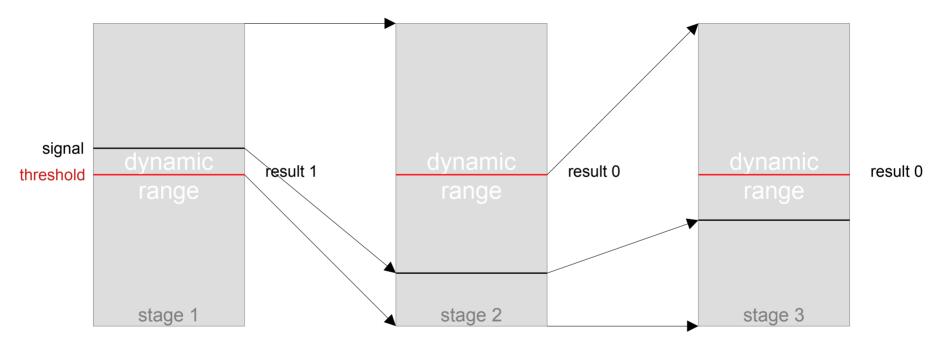

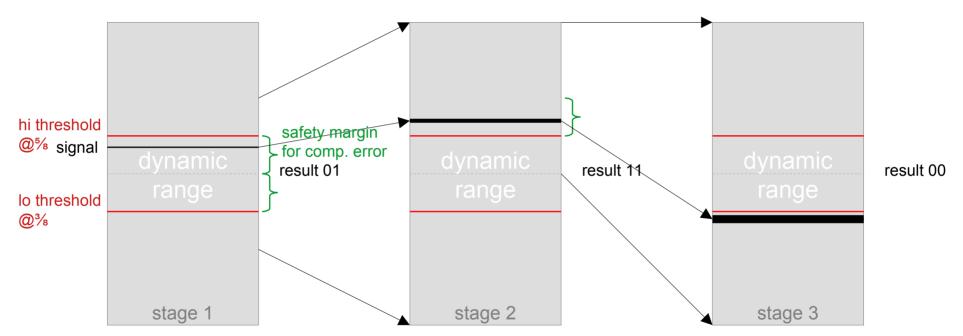

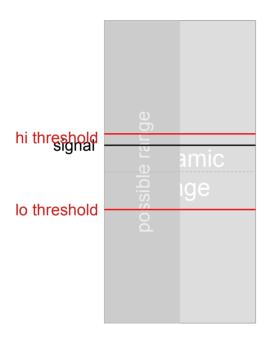

#### **Pipeline Principle**

gain of 2 + offset between stages

### **Pipeline Principle**

gain of 2 + offset between stages

#### **Pipeline Principle**

**SPADIC**

# Pipelined vs. Single-Stage

| analog input   | sample t=1      | X       | sample t=2  | X | sample t=3 | X |  |

|----------------|-----------------|---------|-------------|---|------------|---|--|

| Pipelined Algo | rithmic ADC (SP | ADIC 2. | x)          |   |            |   |  |

| stage 1 out    | bit 2, t=0      |         | bit 2, t=1  |   | bit 2, t=2 |   |  |

| stage 2 out    | bit 1, t=-1     |         | bit 1, t=0  |   | bit 1, t=1 |   |  |

| stage 3 out    | bit 0, t=-2     |         | bit 0, t=-1 |   | bit 0, t=0 |   |  |

#### UNIVERSITÄT HEIDELBERG ZUKUNFT SEIT 1386

# Pipelined vs. Single-Stage

|              | 1 ( )       | \ / | \          | \ /         |            |   |

|--------------|-------------|-----|------------|-------------|------------|---|

| analog innut | sample t=1  | X   | sample t=2 | X           | sample t=3 | X |

| anaiog input | Sample (- i | /   | Sample (-2 | $^{\prime}$ | Jampic t-0 | ^ |

| <b>J</b> 1   |             | , , |            | , ,         |            |   |

#### Pipelined Algorithmic ADC (SPADIC 2.x)

| stage 1 out | bit 2, t=0  |        | bit 2, t=1  |        | bit 2, t=2 |               |   |

|-------------|-------------|--------|-------------|--------|------------|---------------|---|

| stage 2 out | bit 1, t=-1 |        | bit 1, t=0  |        | bit 1, t=1 |               | _ |

| stage 3 out | bit 0, t=-2 | $\sim$ | bit 0, t=-1 | $\sim$ | bit 0, t=0 | $\overline{}$ |   |

#### Non-Pipelined SAR ADC

### Pipelined vs. Single-Stage II

- The pipelined version has a very relaxed timing (at least 9 times slower in SPADIC).

- But the input signal has to be transfered between the stages, mulitplied, shifted, ...

- ⇒ sources of errors

- For SPADIC, the sampling rate is 16 MHz  $\Rightarrow$  62.5 ns per sample.

- A pipelined ADC has the entire 62.5 ns for each bit: Comparison + transfer to the next stage.

- A non-pipelined ADC has 6.25 ns per bit: Comparison + threshold adjustment.

We think this is tight, but do-able.

(Dynamic range ~ 750 mV ⇒ LSB = 1.47 mV)

08 SPADIC

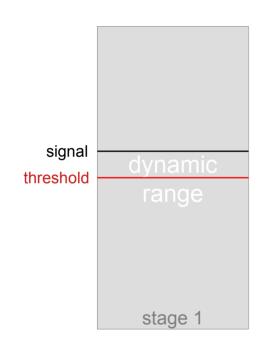

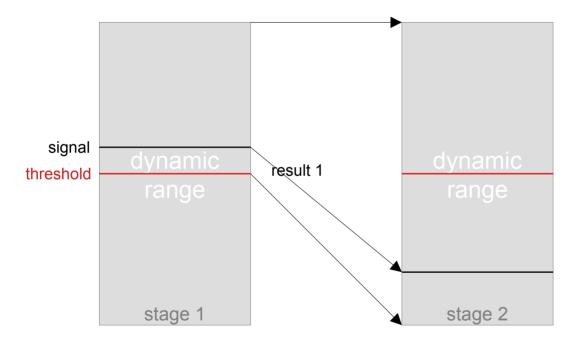

# Pipelined Non-Redundant Algorithmic ADC

ziti"

2023-11-08 SPADIC 14 / 23

# Pipelined Non-Redundant Algorithmic ADC

2023-11-08 SPADIC 14 / 23

# Pipelined Non-Redundant Algorithmic ADC

After three stages: The result is  $100_b + 00_b + 0_b = 100_b$ .

Very sensitive to comparator noise: Any error will never be recovered.

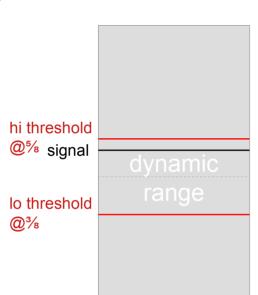

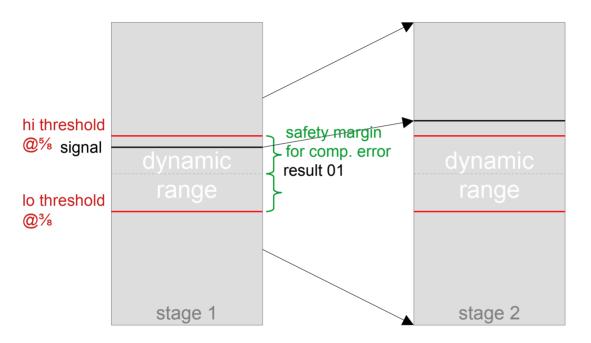

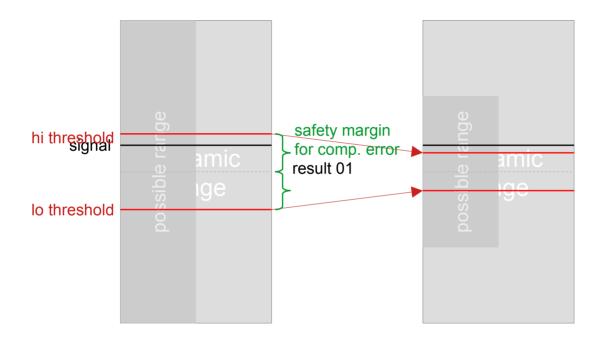

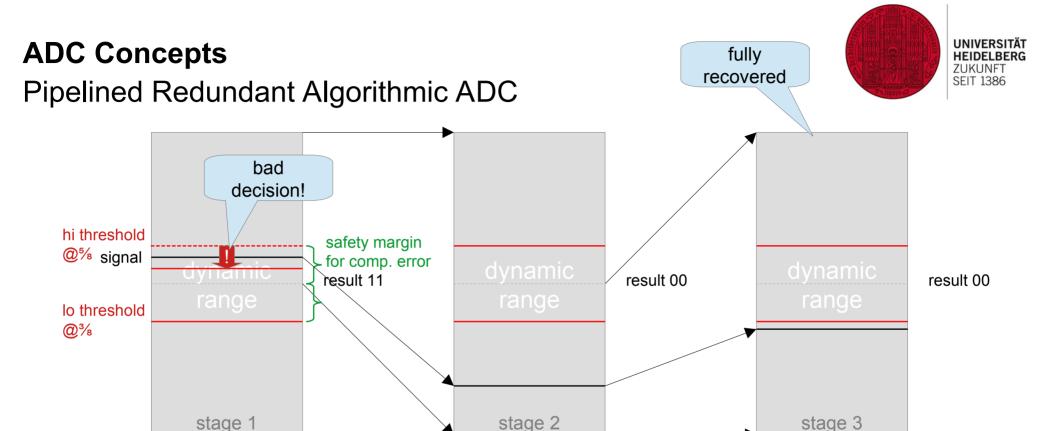

# Pipelined Redundant Algorithmic ADC

ziti"

2023-11-08

SPADIC

stage 1

# Pipelined Redundant Algorithmic ADC

2023-11-08 SPADIC 15 / 23

# Pipelined Redundant Algorithmic ADC

After three stages: The result is  $000b + 100_b + 10b + 10_b + 0b + 0_b = 1000_b$

(the two comparator result have equal weights)

Note: One more bit than comparisons(!)

2023-11-08

#### UNIVERSITÄT HEIDELBERG ZUKUNFT SEIT 1386

#### Pipelined Redundant Algorithmic ADC

After three stages: The result is  $000b + 100_b + 10b + 10_b + 0b + 0_b = 1000_b$

(the two comparator result have equal weights)

Note: One more bit than comparisons(!)

Used in all SPADICs so far. Implemented by multiplying + shifting the input signal between stages.

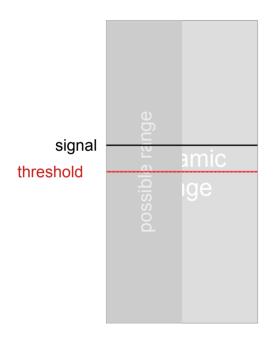

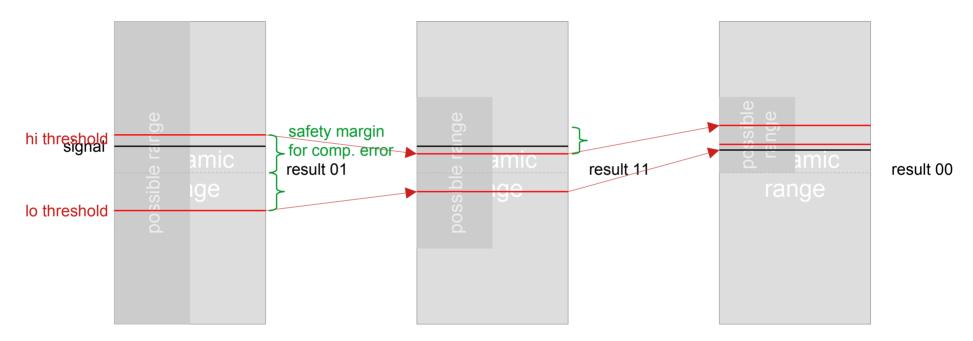

#### Non-Redundant SAR ADC

2023-11-08 SPADIC 16 / 23

#### Non-Redundant SAR ADC

2023-11-08 SPADIC 16 / 23

#### Non-Redundant SAR ADC

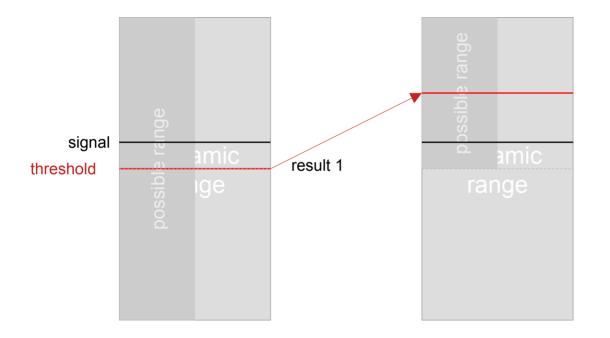

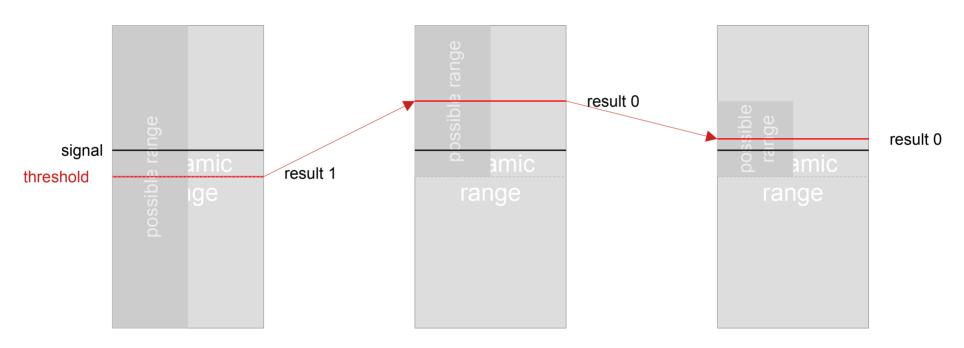

# **ADC Concepts**Redundant SAR ADC

2023-11-08 SPADIC 17 / 23

#### Redundant SAR ADC

2023-11-08 SPADIC 17 / 23

#### Redundant SAR ADC

If we cannot adjust the input signal, we have to <u>adjust the comparator threshold</u> for the same effect. The possible range is halved in each step. The thresholds are at 3/8 and 5/8 of this range.

2023-11-08

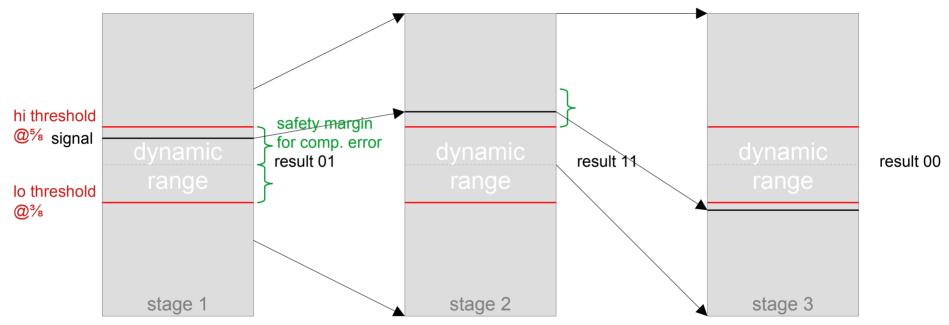

#### Pipelined Redundant vs. Single-Stage Redundant

#### **Redundant Pipelined (SPADIC 2.x)**

- + The comparator is never an issue;

The safety margin is the same in each stage:

½ ¾ = ½ of the dynamic range

△ ~100 mV

(the SPADIC2 implementation compares currents, but "a lot" remains "a lot").

- The transfer of the signal between stages has to be precise.

Errors propagate and multiply.

#### **Redundant SAR (SPADIC 3.0)**

- Comparator noise becomes a problem in later stages.

- Safety margin  $1/(8 \times 2^{n-1})$  after *n* comparisons

- $\Rightarrow$  1/1024  $\triangleq$  0.7 mV for the last comparison

- ⇒ precise DAC + comparator required

+ The signal is stable all the time.

1-08 SPADIC

#### Pipelined Redundant vs. Single-Stage Redundant

#### **Redundant Pipelined (SPADIC 2.x)**

- + The comparator is never an issue; The safety margin is the same in each stage:  $\frac{1}{2} - \frac{3}{8} = \frac{1}{8}$  of the dynamic range ≙ ~100 mV (the SPADIC2 implementation compares currents, but "a lot" remains "a lot").

- The transfer of the signal between stages has to be precise.

Errors propagate and multiply.

#### **Redundant SAR (SPADIC 3.0)**

- Comparator noise becomes a problem in later stages.

- Safety margin  $1/(8 \times 2^{n-1})$  after *n* comparisons

- $\Rightarrow$  1/1024  $\triangleq$  0.7 mV for the last comparison

- ⇒ precise DAC + comparator required

- + The signal is stable all the time.

- ⇒ lots of effects: mismatch, biasing, noise, ...

**SPADIC** 2023-11-08

#### Redundant SAR ADC

#### In the Case of SPADIC

- Analysis of the algorithm:

- The thresholds have to be provided by DACs (pipelined: static).

- At the beginning, the DAC has to make larger steps.

- ⇒ Longer settling time. But also larger safety margins!

- We want a 9 bit result ⇒ 8 comparisons. Fits perfectly with the ×10 clock available:

- 1 Clock Sample & Hold

- 8 Clocks Comparisons

- 1 Clock Reset

This is a major change ⇒ working title "SPADIC 3.0"

2023-11-08 SPADIC 19 / 23

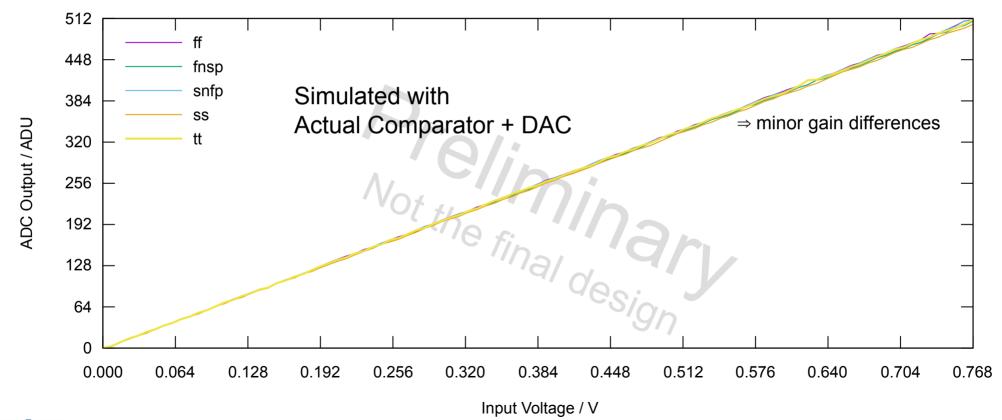

#### **First Simulation Results**

# Linearity & Stability over Process Corners

2023-11-08

#### **First Simulation Results**

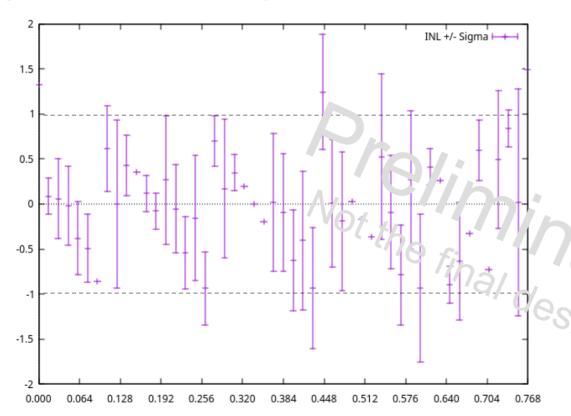

# Integrated Non-Linerarity & Noise

50 Transient Simulations with Noise.

$\Rightarrow$  INL + Noise in the order of 1 LSB.

Thank you!

After three stages: The result is  $100_b + 100_b + 00_b + 00_b + 0_b + 0_b = 1000_b$

$\Rightarrow$  same conversion result, same state in stage 3  $\checkmark$ .

2023-11-08

SPADIC