Characterization and commissioning of the front-end electronics for the Silicon Tracking System of the CBM experiment

> Dissertation zur Erlangung des Doktorgrades der Naturwissenschaften

vorgelegt beim Fachbereich Physik der Johann Wolfgang Goethe-Universität in Frankfurt am Main

> von Osnan Maragoto Rodríguez aus Pinar del Río, Kuba

Frankfurt am Main (2023) (D 30)

vom Fachbereich Physik der Johann Wolfgang Goethe-Universität als Dissertation angenommen.

Dekan:

Prof. Dr. Roger Erb

Gutachter:

Prof. Dr. Alberica Toia Prof. Dr. Christoph Blume

Betreuer:

Dr. Jörg Lehnert

Datum der Disputation:

"The best that most of us can hope to achieve in physics is simply to misunderstand at a deeper level"

Wolfgang Pauli

To my family

# Contents

| Abstract 1 |               |                                                                                                                                                                                    |           |  |  |  |  |  |

|------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|

| K          | Kurzfassung 4 |                                                                                                                                                                                    |           |  |  |  |  |  |

| 1          | Intr          | roduction                                                                                                                                                                          | 7         |  |  |  |  |  |

|            | 1.1           | The QCD phase diagram                                                                                                                                                              | 8         |  |  |  |  |  |

|            | 1.2           | QCD at high baryon densities: neutron stars                                                                                                                                        | 0         |  |  |  |  |  |

|            |               | 1.2.1 Equation of state $\ldots$                                                                  | 12        |  |  |  |  |  |

|            | 1.3           | Heavy ion collisions                                                                                                                                                               | 13        |  |  |  |  |  |

|            | 1.4           | The FAIR facility                                                                                                                                                                  | <b>14</b> |  |  |  |  |  |

|            | 1.5           | The physics program of the CBM experiment                                                                                                                                          | 15        |  |  |  |  |  |

|            |               | 1.5.1 Event by event fluctuations                                                                                                                                                  | 16        |  |  |  |  |  |

|            |               | 1.5.2 Collective flow                                                                                                                                                              | 17        |  |  |  |  |  |

|            |               | 1.5.3 Lepton pairs                                                                                                                                                                 | 18        |  |  |  |  |  |

|            |               | 1.5.4 Strangeness and hypernuclei                                                                                                                                                  | 19        |  |  |  |  |  |

|            |               | 1.5.5 Open and hidden charm                                                                                                                                                        | 20        |  |  |  |  |  |

|            | 1.6           | The CBM experimental setup                                                                                                                                                         | 21        |  |  |  |  |  |

|            | 1.7           | The Silicon Tracking System                                                                                                                                                        | 25        |  |  |  |  |  |

|            |               | 1.7.1 The STS detector module                                                                                                                                                      | 26        |  |  |  |  |  |

|            |               | 1.7.2 Silicon micro-strip sensor                                                                                                                                                   | 27        |  |  |  |  |  |

|            |               | 1.7.3 Al-polyimide low mass microcables                                                                                                                                            | 28        |  |  |  |  |  |

|            | 1.8           | The STS readout chain                                                                                                                                                              | 29        |  |  |  |  |  |

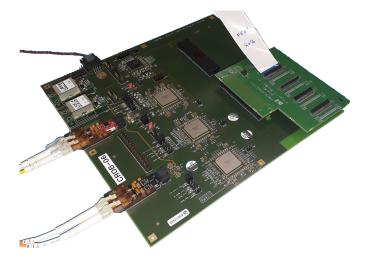

|            |               | 1.8.1 Front-end board                                                                                                                                                              | 30        |  |  |  |  |  |

|            |               | 1.8.2 Readout board                                                                                                                                                                | 31        |  |  |  |  |  |

|            |               | 1.8.3 Common readout interface                                                                                                                                                     | 32        |  |  |  |  |  |

| <b>2</b>   | Test          | t and characterization of the STS-XYTER v2.2                                                                                                                                       | 3         |  |  |  |  |  |

|            | 2.1           | General description of the STS-XYTER v2.2 ASIC                                                                                                                                     | 33        |  |  |  |  |  |

|            |               | 2.1.1 Hit generation mechanism                                                                                                                                                     | 34        |  |  |  |  |  |

|            |               | 2.1.2 Overview of the changes implemented in the STS-XYTER v2.1                                                                                                                    | 35        |  |  |  |  |  |

|            | 2.2           | STS-XYTER v2.2 operation setup                                                                                                                                                     | 36        |  |  |  |  |  |

|            | 2.3           | Characterization of the analog front-end                                                                                                                                           | 36        |  |  |  |  |  |

|            |               | 2.3.1 Gain estimation for the shapers                                                                                                                                              | 37        |  |  |  |  |  |

|            |               | 2.3.2 CSA discharge time constant estimation                                                                                                                                       | 38        |  |  |  |  |  |

|            |               | 2.3.3 Charge sensitive amplifier fast reset                                                                                                                                        | 38        |  |  |  |  |  |

|            |               | 2.3.4 Ballistic deficit estimation                                                                                                                                                 | 39        |  |  |  |  |  |

|            |               |                                                                                                                                                                                    | 10        |  |  |  |  |  |

|            | 2.4           |                                                                                                                                                                                    | 11        |  |  |  |  |  |

|            | 2.5           | Linearity of the $VRef_T$ transfer function $\ldots \ldots \ldots$ | 13        |  |  |  |  |  |

|          | 2.6            | Summary of noise measurements                                           |      |

|----------|----------------|-------------------------------------------------------------------------|------|

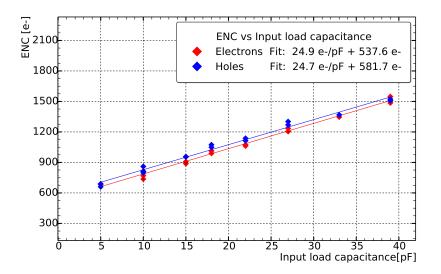

|          |                | 2.6.1 Noise dependence on input load capacitance                        |      |

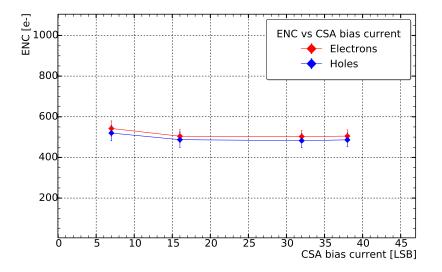

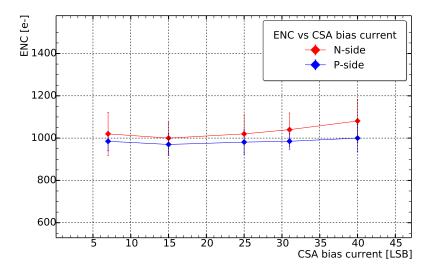

|          |                | 2.6.2 Noise dependence on CSA bias current                              |      |

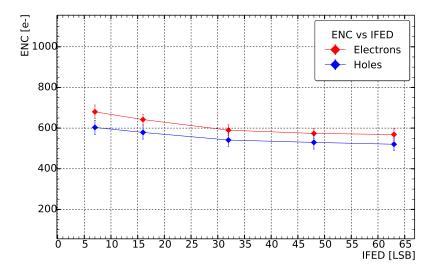

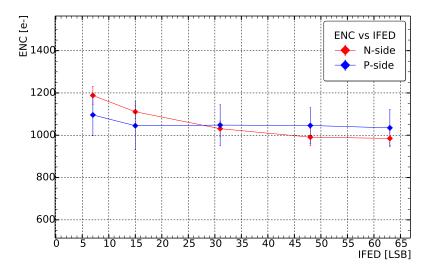

|          |                | 2.6.3 Noise dependence on the IFED resistor values                      |      |

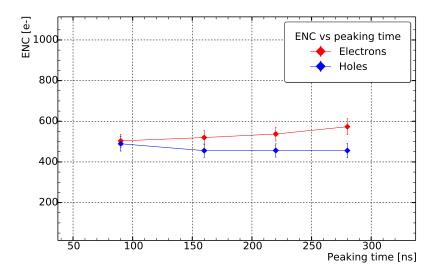

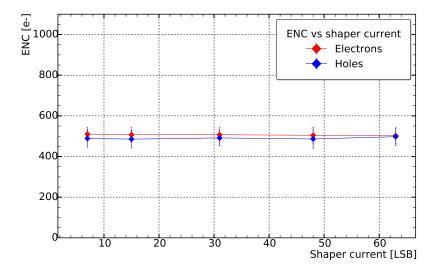

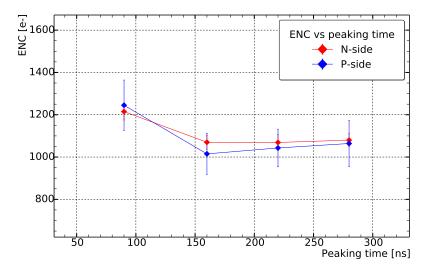

|          |                | 2.6.4 Noise dependence on shaping times and shaper current              |      |

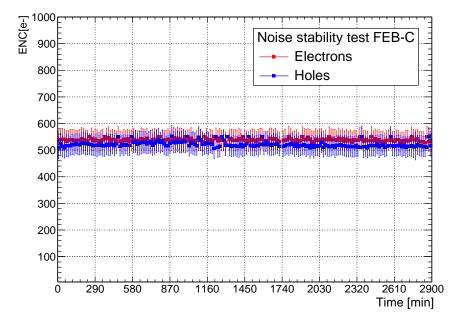

|          |                | 2.6.5 Noise stability tests                                             | . 50 |

|          | 2.7            | Summary                                                                 | . 51 |

| 3        | Dev            | velopment of procedures and software tools for the ASIC quality control | 53   |

|          | 3.1            | Basics considerations                                                   | . 53 |

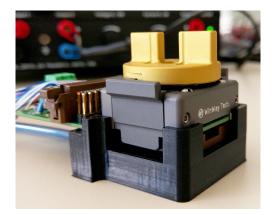

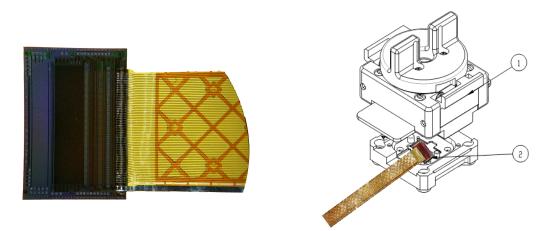

|          | 3.2            | The STS-XYTER pogo prober interface                                     |      |

|          | 3.3            | Experimental setup                                                      |      |

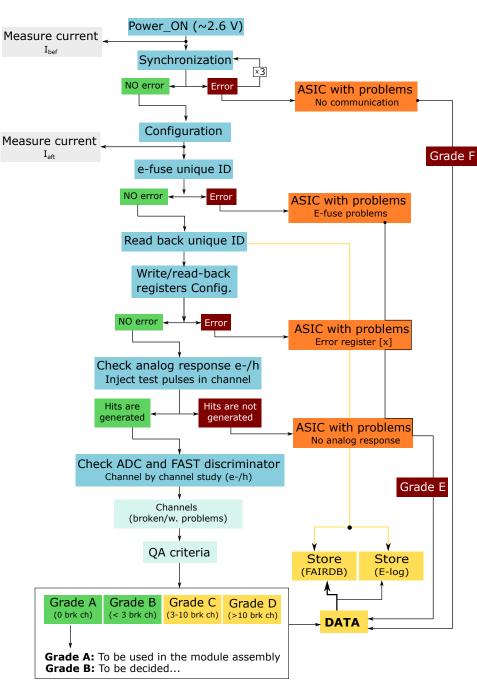

|          | 3.4            | ASIC testing protocol                                                   |      |

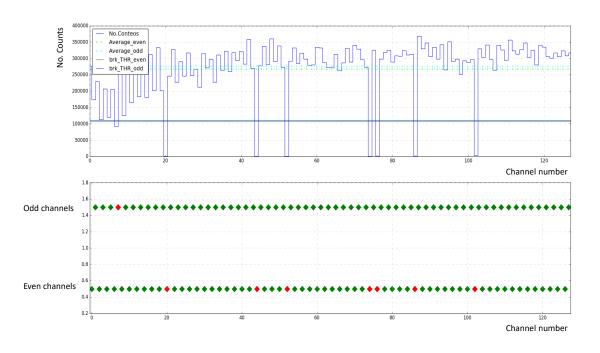

|          |                | 3.4.1 Evaluation of the ASIC quality                                    |      |

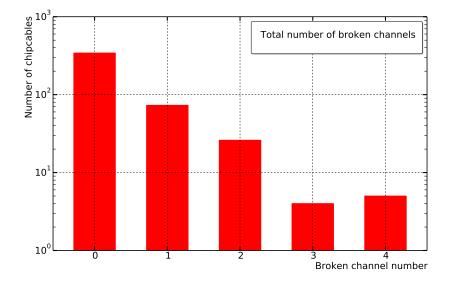

|          |                | 3.4.2 Evaluation of the chipcable quality                               |      |

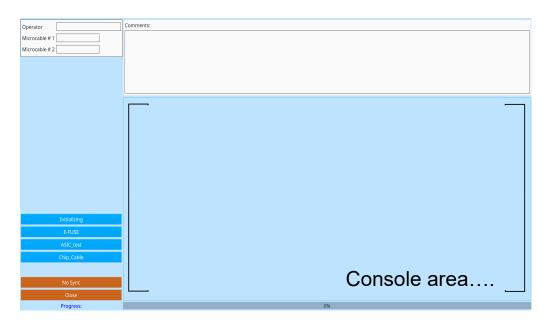

|          | 3.5            | Software developments and GUI implementation                            |      |

|          | 0.0            | 3.5.1 GUI characterization                                              |      |

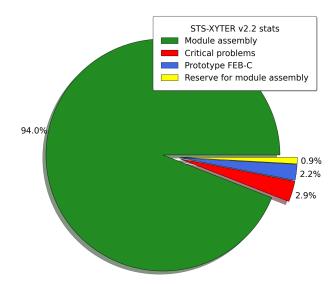

|          | 3.6            | Results and statistics                                                  |      |

|          | 3.7            | Summary                                                                 |      |

|          |                |                                                                         |      |

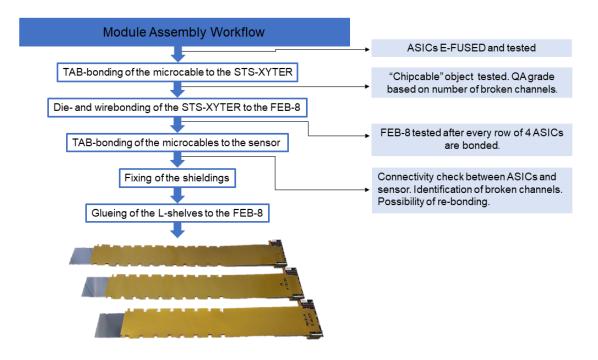

| 4        |                | formance of STS fully assembled modules                                 | 67   |

|          | 4.1            | Introduction to the STS module as main building block                   |      |

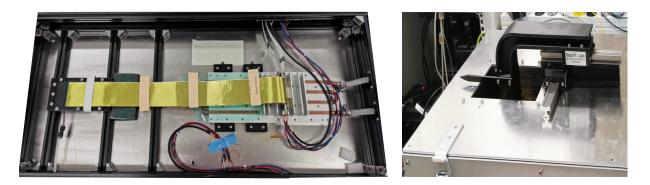

|          | 4.2            | Experimental setup                                                      |      |

|          | 4.3            | Test and characterization of fully assembled modules                    |      |

|          |                | 4.3.1 Calibration procedures for modules testing                        |      |

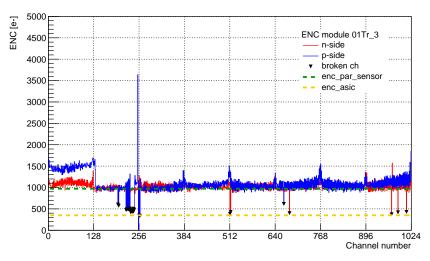

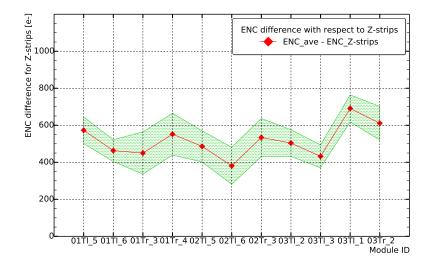

|          |                | 4.3.2 ENC investigations                                                |      |

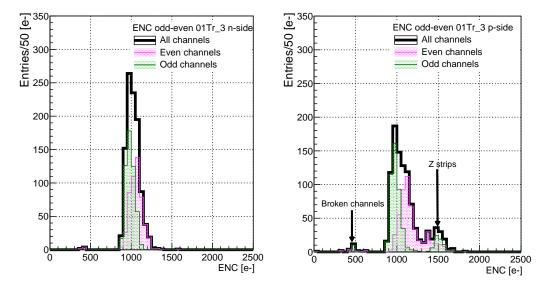

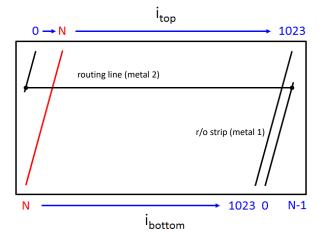

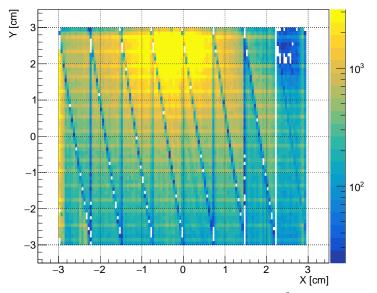

|          |                | 4.3.3 Z-strips studies                                                  |      |

|          | 4.4            | Study of the STS-XYTER v2.2 settings in the module readout              |      |

|          | 4.5            | Measurement of the response to a gamma source                           |      |

|          |                | 4.5.1 Response function of the ADC threshold                            |      |

|          | 4.6            | High voltage scan and stability tests                                   |      |

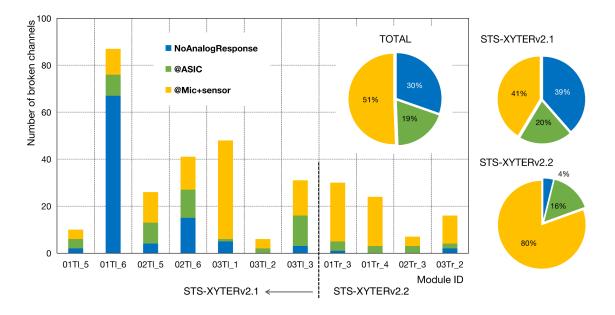

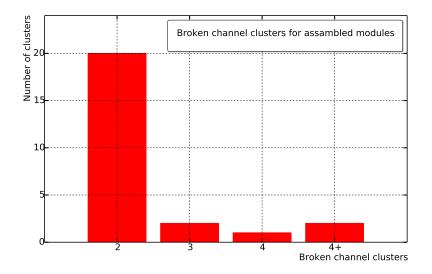

|          | 4.7            | Statistics on module tests                                              | . 82 |

|          | 4.8            | Summary                                                                 | . 84 |

| <b>5</b> | $\mathbf{Ass}$ | embly, test, operation and performance of the mSTS                      | 86   |

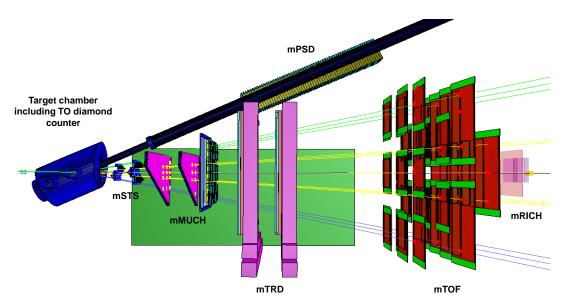

|          | 5.1            | The mCBM experiment                                                     | . 86 |

|          |                | 5.1.1 mSTS as part of mCBM                                              |      |

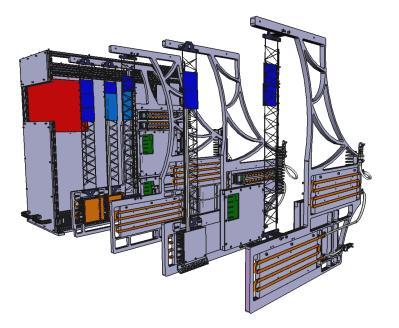

|          | 5.2            | Assembling and installation                                             |      |

|          | 5.3            | Commissioning and operation                                             | . 89 |

|          | 5.4            | Data analysis                                                           |      |

|          |                | 5.4.1 Reconstruction chain                                              |      |

|          |                | 5.4.2 Beam characterization                                             |      |

|          |                | 5.4.3 Time resolution                                                   |      |

|          |                | 5.4.4 Charge distribution                                               |      |

|          |                | 5.4.5 Calibrated charge distribution                                    |      |

|          | 5.5            | Summary                                                                 |      |

| _        |                |                                                                         |      |

| 6        | Sun            | nmary and conclusions                                                   | 100  |

| Zι       | ısam           | menfassung                                                              | 103  |

### ii

| A The prototype FEB-C                                                    | 110 |  |

|--------------------------------------------------------------------------|-----|--|

| B Waveforms of the STS-XYTER v2.2 shapers for electron polarity          | 111 |  |

| C ADC calibration                                                        | 112 |  |

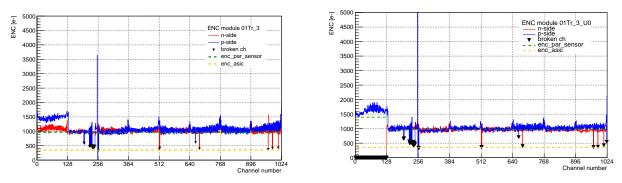

| D Noise comparison for module $01$ Tr <sub>-</sub> 3 in different setups | 114 |  |

| List of Acronyms                                                         |     |  |

| References                                                               |     |  |

| Acknowledgements                                                         |     |  |

| Curriculum Vitae                                                         |     |  |

## Abstract

The Compressed Baryonic Matter (CBM) experiment is a fixed-target heavy-ion physics experiment at the Facility for Antiproton and Ion Research (FAIR) in Darmstadt, Germany. The CBM physics program aims at exploring the QCD phase diagram at very high net-baryon densities, where a first-order phase transition from hadronic to partonic matter and a chiral phase transition is expected to occur. For high-statistics measurements of rare probes, CBM is designed to cope with very high interaction rates up to 10 MHz. Therefore, the experiment will be equipped with fast and radiation hard detectors employing free-streaming readout electronics.

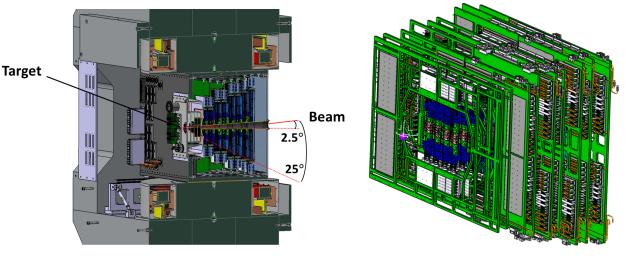

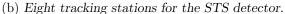

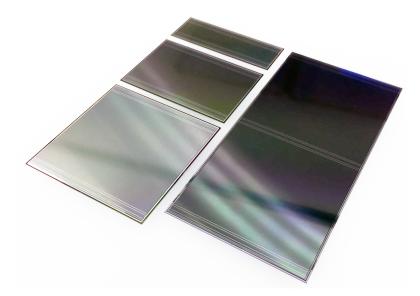

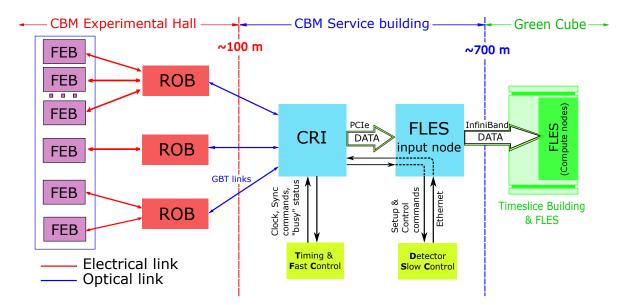

The central detector for determining the momentum of charged particle in the CBM experiment is the Silicon Tracking System (STS). It is designed to measure up to 1000 charged particles per event in nucleus-nucleus collisions at interaction rates between 0.1 and 10 MHz. The detector system consists of 876 double-sided silicon micro-strip sensors arranged in 8 tracking stations covering a physics aperture of  $2.5^{\circ} \leq \Theta \leq 25^{\circ}$ . It is placed between 30 cm and 100 cm downstream the target, inside 1 Tm dipole magnetic field. The experimental conditions pose demanding requirements in terms of channel density and readout bandwidth to be met by the front-end electronics.

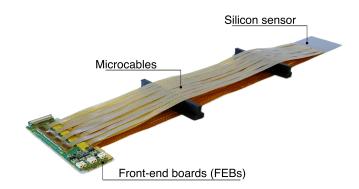

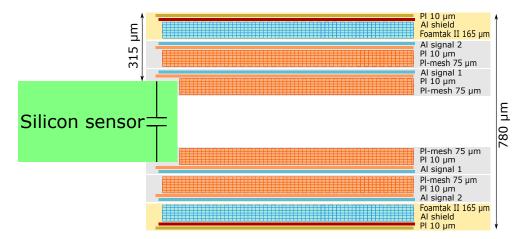

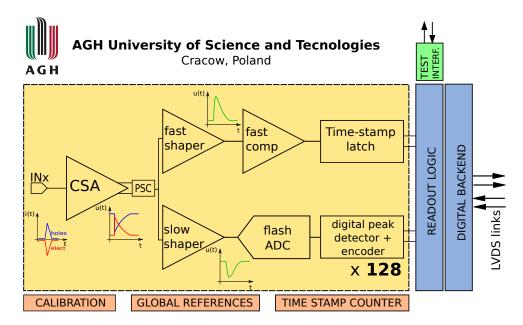

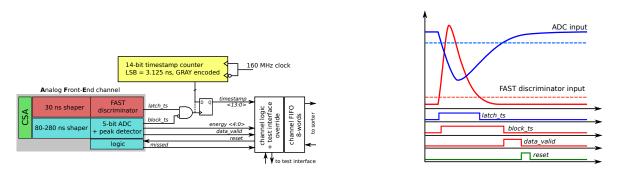

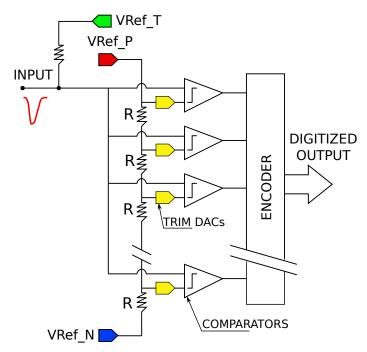

The detector's functional building block is the module, consisting of a double-sided, doublemetal silicon microstrip sensor, microcables and two front-end electronics boards. An essential component is the STS-XYTER, a dedicated ASIC for the readout of the double-sided silicon microstrip sensors. It is a low power, self-triggering ASIC with 128 channels, 5-bit ADC charge and 14-bit timing information.

The STS-XYTER v2.2 is the latest and final revision of the chip, therefore, its characterization is one of the major steps before its operation in the full readout chain. During this work, the STS-XYTER v2.2 have been extensively characterized and a set of procedures and software tools, used in the ASIC characterization, have been implemented and optimized.

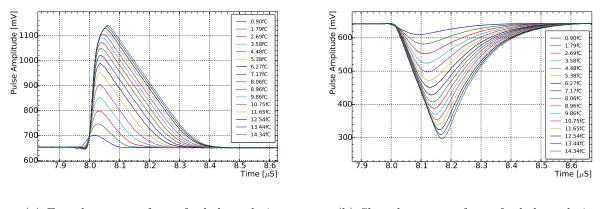

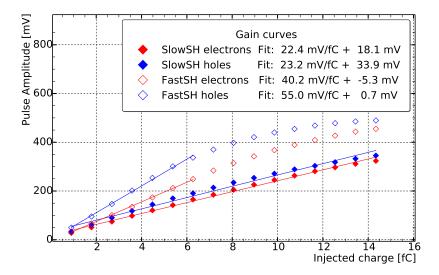

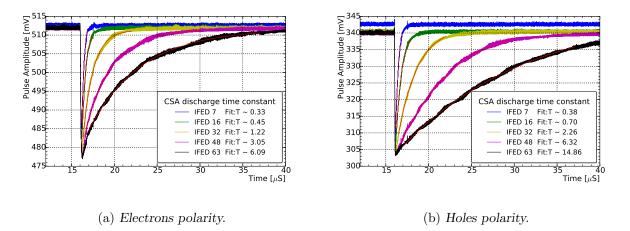

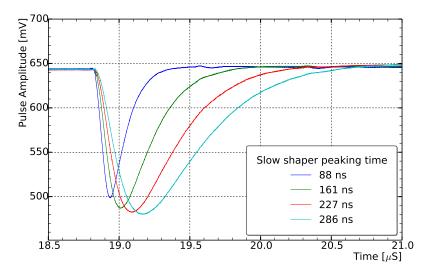

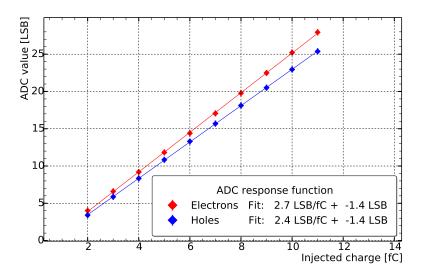

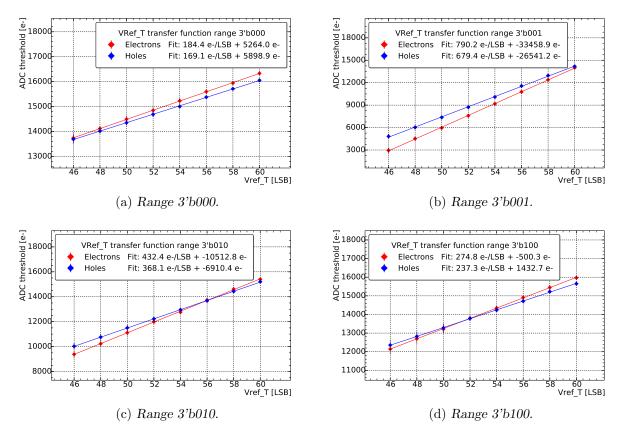

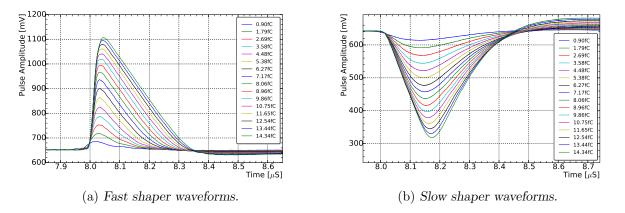

The collection and analysis of the analog waveforms, where gain values were extracted for the slow and fast shaper, represent one of the first tested functionalities. The slow shaper peaking time was estimated for all possible values. The discharge time constant was calculated, obtaining larger values for holes polarity compared to electrons polarity. The ADC global threshold response was measured and its linearity evaluated for all possible ranges.

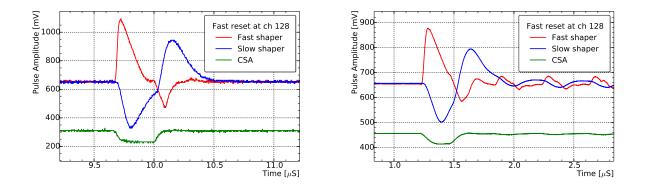

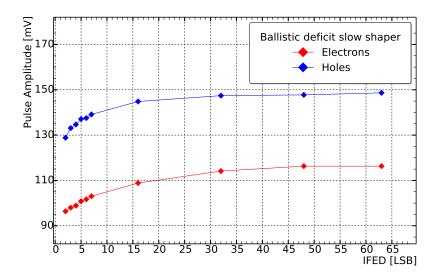

In the last version of the ASIC (v2.2) it was found out that, since the inclusion of the diode-based ESD protection circuit, the CSA fast reset is not working as expected. However, it is possible to operate the chip at high rate without the fast reset feature, by reducing the discharge time constant of the CSA. It has been demonstrated that the ASIC can be operated without the fast reset feature, non compromising the performance in terms of ballistic deficit or noise levels.

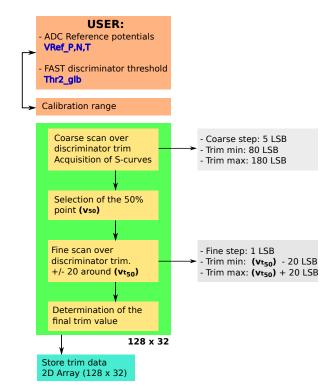

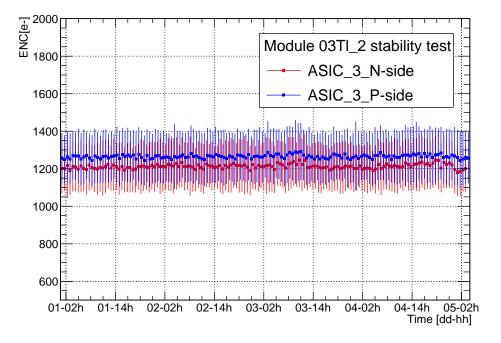

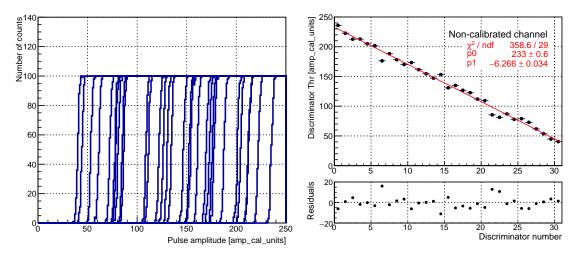

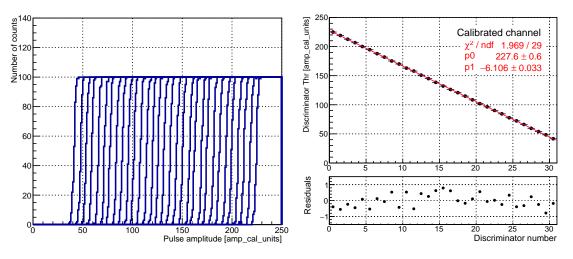

Among the multiple operation requirements of the STS-XYTER v2.2 ASIC, the noise performance is one of the most important. The noise performance of the ASIC has been evaluated as a function of different parameters such as: input capacitance, CSA bias current, IFED resistor, shaping time, shaping current and stability tests. These results have demonstrated a stable and reliable performance with no significant deterioration of the noise levels for a large range of studied settings. A prerequisite for the assembly of functional detector modules, in any experiment, is a rigorous Quality Assurance (QA) of the components. A dedicated setup has been used, based on a custom designed pogo-pin station where a big sample of ASICs and chipcables were tested. QA protocols have been designed and optimized in order to improve the testing procedures. A quality grade for every ASIC and chipcable, based on the gained experience from testing previous versions of the chip, have been proposed. A GUI has been developed in PyQt version 4.0 for making the testing process as user friendly as possible. The implemented software for testing the chips and chipcables has been used since 2021, improving significantly the detector modules assembly aiming to the STS production.

The test and characterization of fully assembled modules is fundamental for proving assembly concepts for the final STS detector. Across the last years, the CBM-STS project has achieved important milestones related to the assembly and successful operation of the first modules. The systematic testing of fully assembled STS modules allowed to verify the performance of the latest version of the front-end ASIC functionalities and the electrical properties of the modules. Several parameters such as ASIC communication and control functionalities have been monitored across all checks. The results of the charge calibration have shown a good and homogeneous response for all produced modules. These results are independent of the overall dimensions of the modules or the version of the front-end electronics in use.

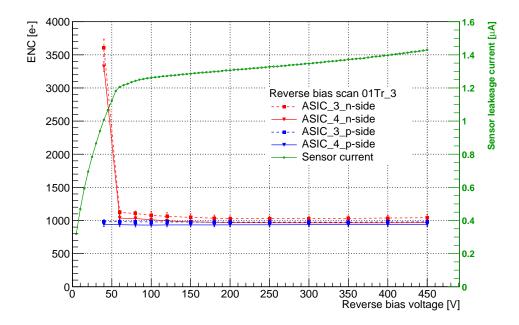

The noise measurements demonstrated that an overall level of approximately 1000 e- ENC is an achievable goal for most of the largest produced modules. The scans of the CSA bias current have exposed a large and stable plateau, at which the modules can be operated without deteriorating the system noise. The noise levels for different shaping times showed the dominance of the voltage noise component at smaller shaping time (90 ns).

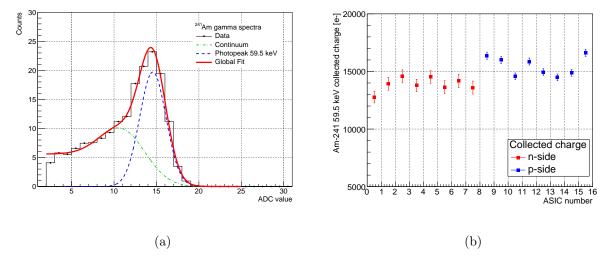

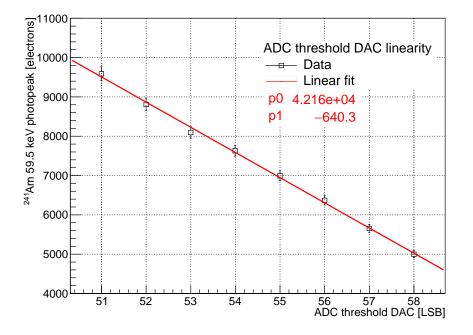

For a selected module, signal readouts have been studied using an <sup>241</sup>Am gamma source. This allowed to verify the calibration procedure and assess the transfer function of the ADC threshold register in the chip. The measured charge collection efficiency was estimated to approximately 96% for the selected module. An average signal to noise ratio (SNR) above 13 was calculated for both polarities.

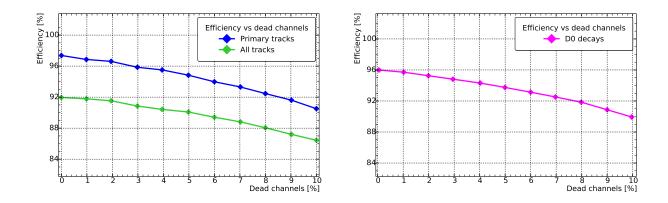

The iterative testing of STS modules is, in general, an essential step for developing a reliable quality control procedure and establishing classification criteria towards series production. These studies brought important insights regarding the fraction of broken and non-operational channels in the modules, and consequently assembly yield.

A small scale prototype of the full detector, named mini-STS (mSTS), has been built as part of the CBM Phase 0 activities. The setup was operated during July 2021 campaign with O + Ni at 2 AGeV at the Heavy Ion Synchrotron SIS18 in GSI, Darmstadt. For the first time, a setup comprising of two tracking stations and a total of 11 modules have been built and operated in a realistic environment.

Periodic structures were observed in the time distribution of all modules. These replica hits are generated due to significant noise in the MHz range in the fast discriminator. This behavior is well understood and consistent with the ASIC design. The replica effect can be significantly reduced by setting the fast discriminator threshold as low as possible without affecting the time resolution of the system and by reducing the noise in the relevant frequency range to the largest possible extent.

A successful time calibration have been implemented. The system time resolution was estimated to be 5.9 ns, which indicates a good time resolution achieved by the detectors. The noise contribution from the fast shaper ( $\sigma_n$ ) was calculated. The charge distributions of reconstructed hits have been presented for different strip clusters and showed a clear separation between noise and MIP position. The average SNR was evaluated for 1 strip-cluster signals for some modules, resulting in a value of approximately 21. This result is an important milestone for the STS detector since the mSTS modules are some of the largest, and therefore, higher capacitance objects in our detector system. The operation of mSTS in a common, high-speed, free-streaming readout chain at intensities up to  $10^9$  ions/s, helps to prove the STS concept in conditions close to the final operation.

## Kurzfassung

Das Compressed Baryonic Matter (CBM) Experiment ist ein Experiment der Schwerionenphysik mit festem Target an der "Facility for Antiproton and Ion Research" (FAIR) in Darmstadt, Deutschland. Das CBM-Physikprogramm zielt auf die Erforschung des QCD-Phasendiagramms bei sehr hohen Netto-Baryonendichten, wo ein Phasenübergang erster Ordnung von hadronischer zu partonischer Materie und ein chiraler Phasenübergang erwartet werden. Zur Messung seltener Sonden mit hoher Statistik ist CBM für hohe Wechselwirkungsraten von bis zu 10 MHz ausgelegt. Daher wird das Experiment mit schnellen und strahlungsharten Detektoren und einer Free-Streaming-Ausleseelektronik ausgestattet sein.

Der zentrale Detektor zur Bestimmung der Impulse geladener Teilchen im CBM-Experiment ist das Silicon Tracking System (STS). Es ist ausgelegt, die Spuren von bis zu 1000 geladenen Teilchen pro Ereignis in Kern-Kern-Kollisionen bei Wechselwirkungsraten zwischen 0.1 und 10 MHz zu messen. Das Detektorsystem besteht aus 876 doppelseitigen Silizium-Mikrostreifensensoren, die in 8 Tracking-Stationen angeordnet sind und eine physikalische Apertur von  $2.5^{\circ} \leq \Theta \leq 25^{\circ}$  abdecken. Das STS ist zwischen 30 cm und 100 cm hinter dem Target innerhalb eines Dipolmagnetfeldes von 1 Tm installiert. Die experimentellen Bedingungen stellen hohe Anforderungen an die Kanaldichte und die Auslesebandbreite, die von der Front-End-Elektronik erfüllt werden müssen.

Das wichtigste Element des Detektors ist das sogenannte "Modul", das aus einem doppelseitigen, Doppel-Metall-Silizium-Mikrostreifensensor, 32 Mikrokabeln und zwei Front-End-Elektronikplatinen besteht. Eine wesentliche Komponente ist der STS-XYTER, ein spezieller ASIC für die Auslese der doppelseitigen Silizium-Mikrostreifensensoren. Es handelt sich um einen stromsparenden, selbsttriggernden ASIC mit 128 Kanälen, der pro Treffer 5-Bit-ADC-Ladungs- und 14-Bit Timing-Information zur Verfügung stellt.

Der STS-XYTER v2.2 ist die neueste und letzte Version des Chips, daher ist seine Charakterisierung ein wesentlicher Schritt vor seinem Einsatz in der finalen Auslesekette. Im Rahmen der vorliegenden Arbeit wurde der STS-XYTER v2.2 ausgiebig getestet sowie eine Reihe von Verfahren und Software-Tools, die bei der ASIC-Charakterisierung verwendet werden, entwickelt, implementiert und optimiert.

Die Messung und Analyse der analogen Signalformen, aus denen die Verstärkungsfaktoren für den langsamen und schnellen Shaper extrahiert wurden, war einer der ersten Charakterisierungsschritte. Die Peaking-Zeit des langsamen Shapers wurde für alle möglichen Konfigurationen bestimmt. Die Entladungszeitkonstanten wurden berechnet, wobei größere Werte für die Polarität der Löcher im Vergleich zur Polarität der Elektronen ermittelt wurden. Das Verhalten der globalen ADC-Schwellenwertsetzung wurde gemessen und ihre Linearität für alle möglichen Messbereiche verifiziert.

In der neuesten Version des ASIC (v2.2) wurde festgestellt, dass seit dem Einbau der Diodenbasierten ESD-Schutzschaltung das schnelle Rücksetzen des ladungsempfindlichen Vorverstärkers (CSA) nicht wie erwartet funktioniert. Es ist jedoch möglich, den Chip auch ohne die schnelle Rücksetzfunktion mit hoher Rate zu betreiben, indem man die Entladezeitkonstante des CSA geeignet reduziert. Es wurde gezeigt, dass der ASIC auf diese Weise betrieben werden kann, ohne Eigenschaften wie das ballistische Defizit oder den Rauschpegel zu beeinträchtigen.

Unter den vielfältigen Betriebsanforderungen des STS-XYTER v2.2 ASIC ist gutes Rauschverhalten eine der wichtigsten. Das Rauschverhalten des ASIC wurde als Funktion verschiedener Parameter wie Eingangskapazität, CSA-Bias-Strom, CSA-Rückkopplungs-Widerstand (IFED), Shaping-Zeit, Shaping-Strom sowie Langzeitstabilität charakterisiert. Die Ergebnisse zeigen einen stabilen und zuverlässigen Betrieb des ASIC ohne signifikante Verschlechterung des Rauschpegels über einen großen Bereich möglicher Einstellungen.

Eine Voraussetzung für den Bau funktionsfähiger Detektoreinheiten in jedem Experiment ist eine strenge Qualitätssicherung (QA) der Komponenten. Für die Tests einzelner ASICs wurde ein spezieller Aufbau verwendet, der auf einer speziellen Pogo-Pin-Station basiert, in der eine große Anzahl von ASICs und Chipkabeln getestet wurde. QA-Protokolle wurden entwickelt und optimiert, um die Testverfahren zu verbessern. Für jeden ASIC und jedes Chipkabel wurde, basierend auf den Erfahrungen, die beim Testen früherer Versionen des Chips gesammelt worden waren, eine Qualitätsstufe ermittelt. Es wurde eine grafische Benutzeroberfläche in PyQt Version 4.0 entwickelt, um den Testprozess so benutzerfreundlich wie möglich zu gestalten. Die implementierte Software zum Testen von Chips und Chipkabeln wird seit 2021 verwendet, wodurch erhebliche Verbesserungen bei der Montage der Detektormodule im Hinblick auf die STS-Serienproduktion erreicht wurden.

Der Test und die Charakterisierung vollständig montierter Module ist von grundlegender Bedeutung für die Verifizierung der Montagekonzepte für den endgültigen STS-Detektor. In den letzten Jahren hat das CBM-STS-Projekt wichtige Meilensteine in Bezug auf den Zusammenbau und den erfolgreichen Betrieb der ersten Module erreicht. Systematische Tests der vollständig montierten STS-Module ermöglichten die Überprüfung der Leistung der neuesten Version der Front-End-ASIC-Funktionen und die elektrischen Eigenschaften der Module. Parameter wie z.B. die ASIC-Kommunikation und die Kontroll-Funktionalität wurden bei allen Messungen durchgehend überwacht. Die Ergebnisse der Ladungskalibrierung zeigten ein gutes und homogenes Verhalten für alle produzierten Module. Die Resultate sind unabhängig von den Gesamtabmessungen (Kabelund Sensorlänge) der Module bzw. der verwendeten Version der Front-End-Elektronik.

Die Rauschmessungen haben gezeigt, dass ein Gesamtpegel von etwa 1000 e<sup>-</sup> ENC für die meisten der größten produzierten Module ein erreichbares Ziel ist. Die Scans des CSA-Bias-Stroms haben ein großes und stabiles Plateau aufgezeigt, in dem die Module betrieben werden können, ohne dass sich das Systemrauschen verschlechtert. Die Messungen der Rauschpegel für verschiedene Shaping-Zeiten zeigen die Dominanz der Spannungs-Rauschkomponente bei kleinen Shaping-Zeiten (90 ns).

An einem ausgewählten Modul wurde die Signalauslese mit einer <sup>241</sup>Am-Gammaquelle untersucht. Dies ermöglichte die Verifizierung des Kalibrierungsverfahrens und die Bewertung der Übertragungsfunktion des ADC-Schwellenwertregisters auf dem Chip. Die Ladungssammel-Effizienz wurde für dieses ausgewählte Modul mit einem Wert von etwa 96% abgeschätzt. Es wurde ein durchschnittliches Signal-Rausch-Verhältnis von über 13 für beide Polaritäten bestimmt.

Das iterative Testen von STS-Modulen ist ein wesentlicher Schritt zur Entwicklung eines zuverlässigen Qualitätskontrollverfahren und zur Festlegung von Klassifizierungskriterien für die Serienproduktion. Diese Studien brachten wichtige Erkenntnisse über den Anteil nicht verbundener oder anderweitig nicht funktionierender Kanäle in den Modulen und folglich für die Fertigungsausbeute bei der Montage.

Im Rahmen der CBM-Phase 0 wurde ein kleiner Prototyp des vollständigen Detektors, der so genannte Mini-STS (mSTS), gebaut. Dieser Aufbau war während der Strahlzeit-Kampagne im Juli 2021 mit O + Ni bei 2 AGeV am Schwerionensynchrotron SIS18 an der GSI Darmstadt in Betrieb. Zum ersten Mal wurde ein Aufbau mit zwei Tracking-Stationen und insgesamt 11 Modulen gebaut und in einer realistischen Experimentumgebung betrieben. In der zeitlichen Verteilung der Daten aller mSTS-Module wurden periodische Strukturen beobachtet. Diese sogenannten Replika-Treffer werden durch ein starkes Rauschen im MHz-Bereich im schnellen Diskriminator verursacht. Es ist möglich, dieses Verhalten aus den Eigenschaften des ASIC-Designs zu verstehen. Der Replika-Effekt kann deutlich reduziert werden, indem der Schwellenwert des schnellen Diskriminators so niedrig wie möglich eingestellt wird, ohne die Zeitauflösung des Systems zu beeinträchtigen, und indem externe Rauschquellen im relevanten Frequenzbereich so weit wie möglich reduziert werden.

Für die mSTS-Daten wurde erfolgreich eine Zeitkalibrierung durchgeführt. Die Zeitauflösung des Systems wurde zu 5.9 ns abgeschätzt, was auf eine gute Zeitauflösung der Detektoren schliessen lässt. Der Rauschbeitrag des schnellen Shapers ( $\sigma_n$ ) wurde berechnet. Die Ladungsverteilungen der rekonstruierten Treffer wurden für Cluster verschiedener Streifenanzahl ermittelt und zeigen eine klare Trennung zwischen Rauschverteilung und MIP-Signal. Das durchschnittliche SNR wurde für 1-Streifen-Cluster-Signale für einige Module ausgewertet und ergibt einen Wert von etwa 21. Dieses Ergebnis ist ein wichtiger Meilenstein für den STS-Detektor, da die in mSTS verwendeten Module zu den größten mit höchster Eingangskapazität und damit stärkstem Rauschen in STS gehören. Der Betrieb von mSTS in einer gemeinsamen mCBM-Auslesekette bei Strahlintensitäten von bis zu  $10^9$  ions/s hilft, das STS-Konzept unter Bedingungen zu verifizieren, die dem endgültigen Betrieb nahekommen.

## Chapter 1

## Introduction

The understanding of the universe, and more specifically its evolution, have been some of the most important questions to be answered for the scientific community. With the progress in technology during the last centuries and the development of more sophisticated devices, the theories and discoveries of thousands of physicists have resulted in a remarkable insight into the fundamental structure of matter. Everything in the universe is found to be made from a few basic building blocks called fundamental particles, governed by four fundamental forces: gravity, electromagnetism, strong and weak interactions. Putting aside the gravitational force, which is described by Einstein's general relativity theory, the other three forces can be described by the Standard Model [1].

The Standard Model was developed in stages throughout the end of 20th century, taking into account the work of many scientists worldwide. The current formulation has been developed in the early 1970s, providing a uniform framework for understanding the electromagnetic, weak, and strong interactions. Although the Standard Model is believed to be theoretically self-consistent and it is the most successful theory of elementary particles and their interactions, it falls short of being a complete theory of fundamental interactions.

While the theory describing week interactions is called quantum flavourdynamics (QFD), the weak force is better understood by the electroweak theory (EWT) [2]. The electroweak theory inherits the phenomenological successes of the four-fermion low-energy description of weak interactions, and provides a well-defined and consistent theoretical framework including weak interactions and quantum electrodynamics in a unified picture. The underlying fundamental theory for strong nuclear interaction is called Quantum Chromodynamics (QCD) [3].

There are two key fundamental phenomena associated with QCD. The first one is *asymptotic freedom*, which states that quarks interact weakly at large energies (or equivalently at short distances). As the distance between quarks in hadrons increases, their interaction energy increases as well, which prevents the quarks from hadrons to be separated. The second fundamental property of QCD is *confinement*, which refers to the experimental observation that quarks and antiquarks can not be found isolated in nature. Namely, quarks and antiquarks are found only confined in hadrons, the composite objects they form. This is a consequence of the constant force between the color charges, as they are separated, resulting from the self interaction of gluons, as they also carry charge. Analytically, confinement is unproven, however, Lattice QCD calculations have predicted, that at certain conditions the confinement of quarks in hadrons vanishes, forming a new state of matter, the quark-gluon plasma (QGP) [4], where the quarks and gluons can move freely in the region where a QGP exists, on the scales larger than the size of hadrons (about  $10^{-15}$  m). The nuclear matter under such extreme conditions may exist also in the interior of compact stellar objects like neutron stars.

As every field theory of particle physics, QCD is based on certain symmetries of nature, deduced by observation. Chiral symmetry exists as an exact symmetry only in the limit of vanishing quark masses. However, the actual quark masses, and the strong interaction of quarks and gluons cause the explicit and spontaneous breaking of chiral symmetry, responsible for the generation of hadron masses. Chiral symmetry is approximately restored when quark masses are reduced from their large effective values in hadronic matter to their small bare ones at sufficiently high temperatures and energy densities.

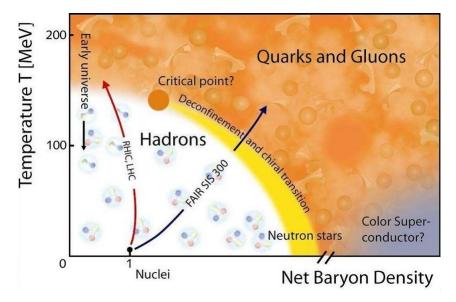

### 1.1 The QCD phase diagram

Different substances exist in the universe across phases such as gas, liquid, and solid, depending on the temperature and pressure. A variation of these conditions might cause a transition from one phase to another one. The boundaries between different transition lines can be described in a diagram of temperature as function of the pressure. Significant efforts have been made so far to explore the phase diagram of strongly interacting matter [5]. In contrast to the countless, very distinct phase diagrams found in condensed matter physics, the phase diagram probed in heavy-ion collisions is a unique and fundamental feature of QCD. The most common way to characterize the QCD phase diagram is in the plane of temperature (T) and the baryon chemical potential ( $\mu_B$ ). The hypothetical phases of strongly interacting matter and their boundaries are illustrated in Fig. 1.1.

Figure 1.1: Schematic phase diagram of dense nuclear matter, in the baryon chemical potential  $\mu_B$  -temperature (T) plane.

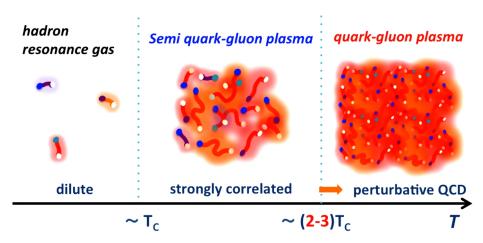

In the region of low temperatures and baryon chemical potential, partons are bound to form hadronic matter (protons, neutrons, mesons, etc). When temperature rises, space is filled with a dilute gas of hadrons; as the temperature increases this hadronic gas gradually fills the space, until the hadrons begin to merge, continuously transforming the matter structure and leading to a breakdown of its description purely in terms of hadrons. Figure 1.2 shows a schematic of the transition from hadronic to quark-gluon plasma phase with increasing the temperature. Yet, a quasiparticle description based on quarks and gluons does not apply either, for while the hadrons have broken down, the strong correlations remain. Thus, the system may be described as a strongly correlated quark-gluon plasma in which both hadronic-like and quark-like degrees of freedom can exist. These conditions, where the number of baryons and antibaryons is almost equal, existed in the early Universe several microseconds after the Big Bang [6]. In this region a smooth crossover from partonic to hadronic matter is expected. Experiments at the Relativistic Heavy Ion Collider (RHIC) and the Large Hadron Collider (LHC) have provided compelling evidence of the formation of a deconfined state of quarks and gluons for matter close to  $\mu B = 0$  and temperatures above 156 MeV.

Figure 1.2: Schematic picture of the crossover transition from the hadronic to quark-gluon plasma phase with increasing temperature [7].

In the region of moderate temperatures and large baryon densities, a first order phase transition has been predicted from hadronic to partonic matter [8]. These predictions, together with the existence of an end point or critical point at high  $\mu$ B have been proposed for several QCD-based models. However, the locations of the phase boundary, the existence of a critical point and a first order phase transition at higher  $\mu$ B remains to be confirmed experimentally.

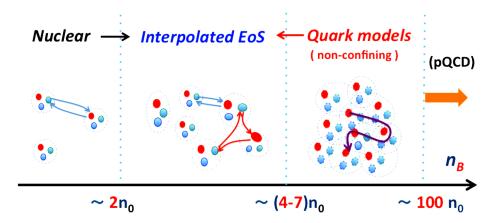

Figure 1.3: Schematic picture of the transition from nuclear to deconfined quark matter with increasing density [7].

At very high baryon densities and low temperatures, the distance between nucleons becomes smaller, making these ones to crush into each other. At a sufficiently high density the matter should percolate, in the sense that their quark constituents are able to propagate throughout the system. Figure 1.3 shows the transition from nuclear to deconfined quark matter with the increasing density. The deconfinement of nuclear matter with increasing density has many similarities to the manner in which atomic gases, when compressed, become gases of itinerant electrons in a background of ions. This state of matter is possibly existing in the interior of the neutron stars.

The phases of QCD are characterized by a variety of condensates in which a macroscopic number of particles (and antiparticles) are strongly correlated by the strong interaction. The emergence of condensates reduces the energy of the system, and in addition, condensates break symmetries in QCD, leading to states with lower symmetry than in the QCD Hamiltonian. The condensates, which depend on temperature and baryon density, play an important role in the structure of hadrons, as well as in neutron stars, since the condensation energies are a large fraction of the energy density in a neutron star core.

### 1.2 QCD at high baryon densities: neutron stars

In the hadronic regime, three quarks bind together to produce a color singlet object. In the regime between hadronic and quark matter, colored quarks and diquarks appear virtually during quark exchanges between baryons (essentially the baryon-baryon interactions). In the quark matter regime, a diquark or a pair of quarks can easily find an extra quark nearby to produce local color neutrality, so that the extra quark is weakly correlated with the diquark or pair. With increasing baryon density or temperature, the effective degrees of freedom of matter change, possibly accompanied by phase transitions. Neutron stars are some of the densest manifestations of massive objects in the universe. They are ideal laboratories for testing theories of dense matter physics and provide connections among nuclear and particle physics and astrophysics. They might exhibit conditions and phenomena not observed elsewhere, such as hyperon-dominated matter, deconfined quark matter, superfluidity and superconductivity, opaqueness to neutrinos, and magnetic fields in excess of  $10^{13}$  Gauss.

Neutron stars are created in the aftermath of the gravitational collapse of the core of a massive star (larger than 8 Solar masses) at the end of its life, which triggers a Type II supernova explosion [10]. Typical neutron stars masses are about 1.4 solar masses, while the radii are in the range of 10 to 14 km. The density can reach values between 5 to 10 times nuclear saturation density and the temperature can go up to  $10^{10}$  kelvins (around 1 MeV). The exception is at neutron star births in supernovae, where temperatures can be tens of MeV, and in final gravitational mergers where temperatures could reach values up to 100 MeV. The bulk properties of neutron stars (e.g., mass, radius, moment of inertia, mass-shed frequency, tidal deformability, etc.) chiefly depend on the equation of state (EOS) describing the macroscopic properties of stellar matter. The EOS of dense matter is also one of the main ingredients for the study of various astrophysical phenomena related to neutron stars, as core-collapse supernovae and binary neutron star (BNS) mergers.

In August 2017, the LIGO-Virgo Scientific Collaboration reported the milestone detection of gravitational waves (GW) from binary neutron stars (BNS) merger GW170817 [11] and since then, the interest in dense matter physics has increased substantially. Although the gravitational waves from this discovery event seen by LIGO only reveal the inspiraling incident neutron stars, with coming improvements to LIGO's sensitivity, future events will give a view of the collision itself, making it possible to learn about the compactness and density profile of the incident neutron stars and, conceivably, whether or not they feature dense quark matter cores. If they do, present constraints on heat transport in neutron stars coming from X-ray observations of how they cool down will turn into constraints on the equation of state and the transport properties of cold dense quark matter.

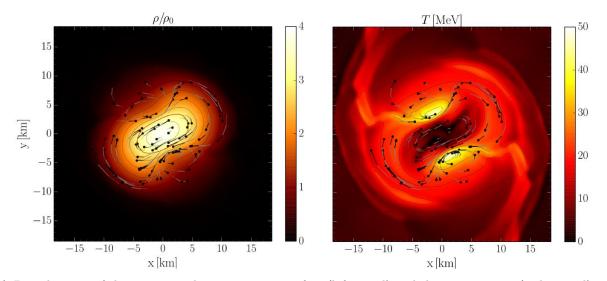

The densities created in the mergers of compact stars can exceed several times the nuclear ground state density. Furthermore, in the early time of the merger, high temperatures close to 100 MeV are obtained. The properties of matter at such high temperature and density are very

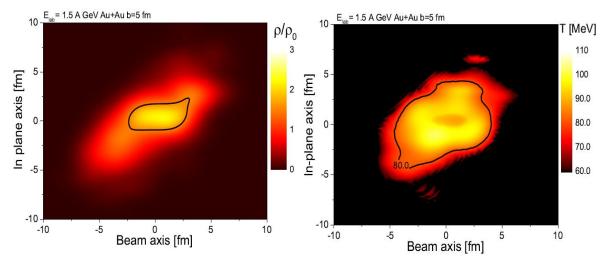

(a) Distributions of the rest-mass density  $\rho$  in units of  $\rho_0$  (left panel) and the temperature (right panel) on the equatorial plane at a post-merger time of t = 6.34 ms for the neutron stars binary merge LS220-M132.

(b) Net baryon density contour in the reaction plane of a non-central Au + Au collision (b = 5 fm) at a beam energy of  $E_{lab} = 1.5 \text{ AGeV}$  (left panel) and the respective temperature (right panel).

Figure 1.4: Comparison between neutron stars binary merge LS220-M132 and Au + Au collision at SIS100. Densities for the heavy ion collisions were calculated using the UrQMD transport model and the temperatures were calculated from the density and energy density using the  $Q\chi P$  model for the equation of state [9].

different from what it's expected from cold nuclear matter. Similar densities and temperatures can be created in the relativistic collisions of heavy nuclei at different particle accelerators. In such heavy ion experiments the heavy nuclei are accelerated to relativistic velocities. It is therefore very intriguing to study QCD matter at similar temperatures and densities in two rather different experimental setups, in neutron star mergers and heavy ion collisions. Figure 1.4 illustrates a comparison between neutron stars binary merge LS220-M132 and Au + Au collision at SIS100, where multiple similarities between both systems can be observed. By combining the findings from both observations one can be able to deduce information about the properties of the QCD matter at high densities and its phase structure. The properties of the equation of state of QCD are the link connecting neutron star mergers and relativistic nuclear collisions. Consequently the goal of such studies aim to find a description for the EOS that should be able to describe neutron star merger and nuclear collision observables and therefore, establish the connection.

#### **1.2.1** Equation of state

The physics of neutron stars represents a way to test our understanding of matter under extreme conditions of density and temperature. This requires the modeling of systems in very different physical conditions such as heavy neutron rich nuclei arranged to form a lattice structure as in the outer crust of the star, or a charge neutral system of interacting hadrons (nucleons, and possibly hyperons or a phase with deconfined quarks) and leptons forming a quantum fluid as in the stellar core [10].

The main ingredient needed to describe the structure of neutron stars is the equation of state. The EOS refers to the equations describing how the pressure and other thermodynamic variables, such as the free energy and entropy, depend upon the quantities of density, temperature and composition. For high density matter, for instance found in neutron stars, the composition is not well understood and the equation of state remains highly uncertain. In the past decades, several approaches have been developed to derive the dense matter EOS. Among non-relativistic approaches, some of the most popular models are based on effective Skyrme interactions, which can be used to describe finite nuclei as well as nuclear matter and neutron stars. The general relativity and causality set important constraints to the neutron stars compactness [11]. In addition, analytic general relativity solutions are useful for understanding the relationships that exist among the maximum mass, radii, moments of inertia, and tidal Love numbers of neutron stars, which are accessible to observation. Some of these relations are independent of the underlying dense matter equation of state, while others are very sensitive to the equation of state.

The EOS of dense matter below nuclear saturation densities can be well approximated by the use of the liquid droplet model, while at higher densities, it can be described by the EOS of bulk nucleonic matter. Bulk neutron star matter differs from bulk matter in ordinary atomic nuclei largely because of the different equilibrium values of the proton fraction. Neutron star matter near and above nuclear saturation densities has very few protons, and is nearly pure neutron matter. The difference between neutron and nuclear matter with nearly equal proton and neutron concentrations is described by the nuclear symmetry energy. The greatest uncertainty in the description of neutron star matter is due to uncertainties in the nuclear symmetry energy, however experiments are beginning to closely constrain those properties.

Recent observations of neutron stars from pulsar timing, quiescent X-ray emission from binaries, and Type I X-ray bursts can set important constraints on the structure of neutron stars and the underlying equation of state. In addition, measurements of thermal radiation from neutron stars have uncovered the possible existence of neutron and proton superfluidity/superconductivity in the core of a neutron star, as well as offering powerful evidence that typical neutron stars have significant crusts. These observations impose constraints on the existence of strange quark matter stars, and limit the possibility that abundant deconfined quark matter or hyperons exist in the core of the stars.

As the only source of data on cold high density matter in QCD, neutron stars are a rich testing ground for microscopic theories of dense nuclear matter, providing an approach complementary to probe dense matter in ultrarelativistic heavy ion collision experiments.

## **1.3** Heavy ion collisions

Heavy ion collision experiments at relativistic energies create extreme states of strongly interacting matter and allow their investigation in the laboratory. In order to search for features like the predicted first-order phase transition, the chiral phase transition and the critical endpoint, moderate temperatures and high baryochemical potentials must be achieved and experimentally accessed. High-energy heavy ion collision experiments worldwide have been investigating the strongly interacting matter under extreme conditions. The RHIC in Brookhaven National Laboratory and the LHC in CERN have been running heavy ion programs to explore the QGP at small baryon chemical potentials and high temperatures, where matter is produced with almost equal numbers of particles and antiparticles, simulating several microseconds after the Big Bang. The efforts made from this collaborations opens the gate for claiming that partonic degrees of freedom prevail in the early phase of the fireball evolution.

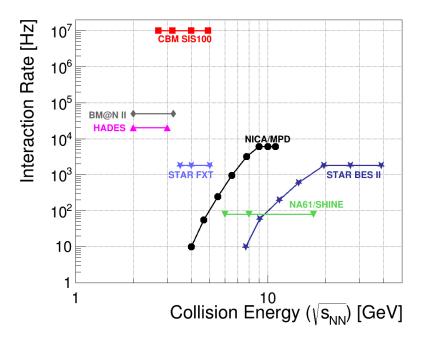

Most of the experimental observables, which are sensitive to the properties of dense nuclear matter, like the flow of some identified particles, higher moments of event-by-event multiplicity distributions of conserved quantities, multi-strange hyperons, and di-leptons demand very high statistics. Therefore, one of the key feature for future experiments is the rate capability, which allows to measure the above mentioned observables with high precision. The interaction rates of existing and planned heavy-ion experiments are presented in Fig 1.5 as a function of center-of-mass energy [12].

Figure 1.5: Comparison of the interaction rates of existing and planned heavy-ion experiments as a function of the center-of-mass energy [12].

The QCD phase diagram at large baryon chemical potentials has been explored by pioneering heavy-ion experiments. Due to the detector technologies available back then when these experiments were designed, their measurements were restricted to abundantly produced hadrons and to di-electron spectra with limited statistics. At the CERN-SPS, the NA61/SHINE experiment continues to search for the first-order phase transition by measuring hadrons using light and medium heavy ion beams. This detector setup is limited to reaction rates of about 80 Hz. The existing HADES detector at SIS18 measures hadrons and electron pairs in heavy-ion collision systems with reaction rates up to 20 kHz. The STAR collaboration at RHIC has been performing a beam energy scan from energies down to  $\sqrt{S_{NN}} = 3.3 \text{ GeV}$  by modifying the collider geometry experiment to a fix target one. At beam energies above  $\sqrt{S_{NN}} = 20 \text{ GeV}$ , the reaction rates of STAR are limited to 800 Hz due to the TPC read-out, and drop down to a few Hz at beam energies below  $\sqrt{S_{NN}} = 8 \text{ GeV}$ because of the decreasing beam luminosity provided by the RHIC accelerator. At the Joint Institute for Nuclear Research (JINR) in Dubna, the fixed-target experiment BM@N is being developed at the Nuclotron to study heavy-ion collisions at gold beam energies up to 4 AGeV. Moreover, at JINR the Nuclotron-based Ion Collider facility NICA with the Multi-Purpose Detector (MPD) is already under operation. The NICA collider is designed to run at a maximum luminosity of  $L = 10^{27} \text{ cm}^{-2} \text{s}^{-1}$  at collision energies between  $\sqrt{S_{NN}} = 8$  and 11 GeV corresponding to a reaction rate of 6 kHz for minimum bias Au + Au collisions. The interaction rate at NICA decreases to about 100 Hz because of low luminosity at  $\sqrt{S_{NN}} = 5 \text{ GeV}$ .

The Facility for Antiproton and Ion Research (FAIR), currently under construction in Darmstadt, Germany, will offer the opportunity to study nuclear collisions at extreme interactions rates. The FAIR Modularized Start Version (MSV) comprises the SIS100 ring, which provides energies for gold beams up to 11 AGeV ( $\sqrt{S_{NN}} = 4.9$  GeV), for Z = N nuclei up to 15 AGeV, and for protons up to 30 GeV.

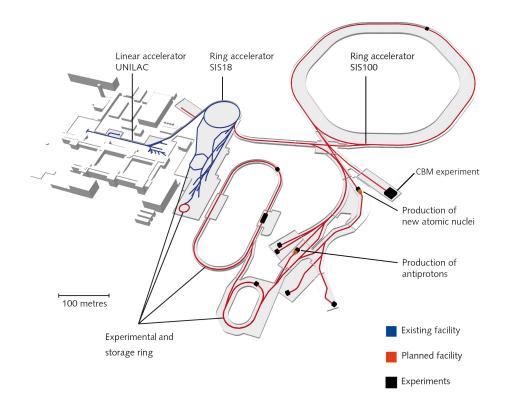

## 1.4 The FAIR facility

The international FAIR facility will provide unique research opportunities in the fields of nuclear, atomic and plasma physics, and applications in the fields of materials research and radiation biophysics including novel medical treatments and space science. The upgraded existing GSI (GSI Helmholtzzentrum für Schwerionenforschung) accelerators UNILAC (Universal Linear Accelerator) and SIS18 (SchwerIonenSynchrotron) will serve as injectors. They will be followed by a superconducting double-synchrotron SIS100 with a circumference of 1084 m and a magnetic rigidity of 100 Tm. The energies of the SIS100 will be up to 30 GeV for protons and up to 11 AGeV for Au ions. The beam intensity will be up to 10<sup>9</sup> ions per second resulting in 10<sup>7</sup> interactions per second using a 1% interaction probability in target. Figure 1.6 illustrates the existing and future installations of the FAIR facility.

FAIR will have the unique ability to provide particle beams of all chemical elements and their ions, as well as protons and antiprotons. The research program of the FAIR facility is grouped in the following experimental collaborations: APPA (Atomic, Plasma Physics and Applications), CBM (Compressed Baryonic Matter), NuSTAR (NUclear STructure, Astrophysics and Reactions) and PANDA (anti-Proton ANihilation at DArmstadt). The APPA experiment will perform tests of fundamental interactions and symmetries as well as applications of nuclear physics in medicine. The wide program of APPA will cover atomic physics, plasma, medical and space radiation physics. NuSTAR will investigate nuclear structure and dynamics of nuclear astrophysics. PANDA will focus on antimatter research, the weak and the strong forces, exotic states of matter, and the structure of hadrons.

The Compressed Baryonic Matter experiment is a next-generation experiment to be operated at FAIR. The CBM experiment proposes one of the richest and leading research programs in the field of heavy-ion physics. Its physics program aims to explore the QCD phase diagram at high baryon densities, where a first-order phase transition from hadronic to partonic matter and a chiral phase transition is expected to occur. The setup consist of a fix target forward spectrometer with fast and radiation hard detectors employing free-streaming readout electronics with a novel online reconstruction concept. For high-statistic measurements of rare probes, CBM is designed to cope with very high interaction rates up to 10 MHz [12]. The experiment is currently being developed by an international collaboration between institutes from Germany, India, Poland and other countries.

Figure 1.6: Layout of the FAIR facility. Blue lines represents existing GSI facilities, the new accelerator complex is shown with red. The superconducting synchrotron SIS100 will provide ion beams for the CBM experiment.

## 1.5 The physics program of the CBM experiment

The rich physics program of the CBM experiment aims to investigate the equation-of-state of QCD matter at densities similar to the densities in the core of neutron stars, and search for a possible phase transition from hadronic to quark-gluon matter, a critical point of the QCD phase diagram, existence of quarkyonic matter, and signatures of chiral symmetry restoration [12, 13].

The CBM physics program will be able to address the following fundamental questions:

- The equation of state of QCD matter and the relevant degrees of freedom at high net-baryon densities. Is there a phase transition from hadronic to quark-gluon matter, or a region of phase coexistence? Do exotic QCD phases exist? Is there a critical point?

- To what extent are the properties of hadrons modified in dense baryonic matter? Are we able to find indications of chiral symmetry restoration?

- How far can we extend the chart of nuclei towards the strange dimension by producing single? and double-strange hypernuclei? Does strange matter exist in the form of heavy multi-strange objects?

To address these questions CBM will investigate collisions of heavy ion and proton beams, with fixed, heavy element targets, at beam energies between 2 and 14 AGeV (up to 14 AGeV for light nuclei and 29 AGeV for protons). The combination of high-intensity beams with a high-rate detector system provides unique conditions for a comprehensive study of QCD matter at the highest net-baryon densities achievable in the laboratory.

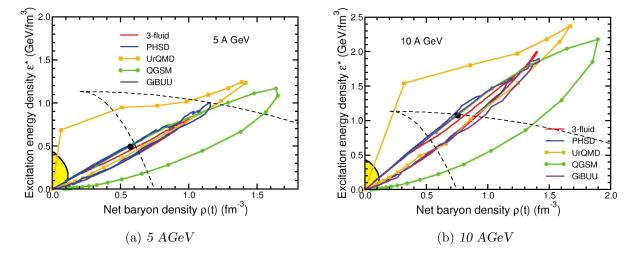

Figure 1.7: Evolution of the excitation energy in the center of the fireball as a function of the baryon-net density calculated by different transport models and a 3-fluid hydrodynamics code. The Au+Au collision system is simulated for two different running scenarios, at 5 and 10 AGeV respectively [12].

Figure 1.7 illustrates the excitation energy density in the center of the collision zone is shown as a function of the net-baryon density for central Au + Au collisions at beam energies of 5 AGeV and 10 AGeV, as predicted by several transport models and a hydrodynamic calculation [14]. The excitation energy is defined as a function of the energy density and the mass density. The solid lines correspond to the time evolution of the system and the dots on the curves labeled UrQMD and QGSM correspond to steps of 1 fm/c in collision time. The expected region of phase coexistence is enclosed by dashed lines.

Some significant observables that are particularly relevant for addressing the questions above will be briefly describe in the following subsections.

#### **1.5.1** Event by event fluctuations

Event by event fluctuations of conserved quantities such as baryon number, strangeness and electrical charge can be related to the thermodynamical susceptibilities and hence provide insight into the properties of matter created in high-energy nuclear collisions [15]. Lattice QCD calculations suggest that higher moments of these distributions are more sensitive to the phase structure of the hot and dense matter created in such collisions. Non-Gaussian moments (cumulants) of these fluctuations are expected to be sensitive to the proximity of the critical point since they are proportional to powers of the correlation length, with increasing sensitivity for higher-order moments [16, 17].

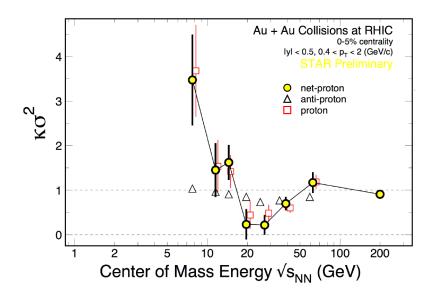

Measurements of these fluctuations have been performed by other collaborations in order to search for the critical point. Figure 1.8 shows results from STAR collaboration, which depicts the volume-independent cumulant ratio  $\kappa\sigma^2$  (excess kurtosis times squared standard deviation) of the net-proton multiplicity distribution as a function of the collision energy, measured in Au + Au collisions.

However, up to date no higher-order event by event fluctuations have been measured at SIS100 energies. The CBM experiment will, for the first time, perform a high-precision study of higher-order fluctuations at various beam energies in order to search for the elusive QCD critical point

Figure 1.8: Energy dependence of the product  $\kappa\sigma^2$  (excess kurtosis times variance) of the net-proton multiplicity distribution (yellow circles) for top 0 - 5% central Au + Au collisions. The Poisson expectation is denoted as dotted line at  $\kappa\sigma^2 = 1$  [12].

in the high net-baryon density range  $\sqrt{S_{NN}} = 2.7$  - 4.9 GeV, corresponding to  $\mu_B \simeq 800$  - 500 MeV [12].

#### 1.5.2 Collective flow

The collective flow of hadrons, resulting from heavy-ion reactions, is driven by the pressure gradient created in the early fireball and provides important information on the dense phase of the collision. The isotropic, radial flow allows to characterize the collision system at kinetic freezeout, i.e. when elastic collisions of the produced particles come to an end. On the other hand, anisotropic flow is produced from the conversion into pressure gradients of anisotropies in the density distribution [18]. Flow effects can be characterized by the azimuthal distribution of the emitted particles in the plane transverse to the beam axis:

$$\frac{dN}{d\varphi} \propto 1 + 2\sum_{n=1}^{\infty} v_n cos[n(\varphi - \Psi_n)]$$

(1.1)

where N is the number of produced particles,  $\varphi$  is the azimuthal angle of each particle,  $\Psi_n$  is the  $n^{th}$  order symmetry plane and the  $v_n$  coefficients are related to the magnitude of the flow-vector [19].

Important observables like multi-differential flow measurements for several hadron species, in particular strange hadrons and anti-baryons, the equation of state and the properties of strange particles, are mandatory for a variety of collision systems and beam energies in the SIS100 energy range in order to address the degree of thermalization.

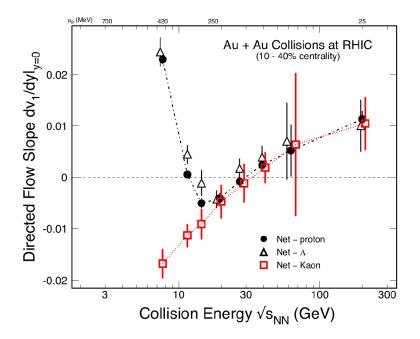

The direct flow  $(v_1)$  is important to understand the role of partonic degrees of freedom and it is sensitive to the softening of the QCD matter EOS, as well as to the phase transition details [21]. Figure 1.9 shows the performance for directed flow  $(v_1)$  of strange hyperons for the STAR collaboration. The directed flow slope  $(dv_1/dv_y)$  is represented as a function of the beam energy for intermediate centrality (10 - 40%) Au + Au collisions for net-protons, net- $\Lambda$ 's and net-Kaons. The error bars define statistical uncertainties, while the caps are systematic uncertainties [20].

Figure 1.9: Directed flow slope  $(dv_1/dv_y)$  versus beam energy for intermediate centrality (10 - 40%) Au + Au collisions for net-protons, net-A's and net-Kaons [20].

The elliptic flow  $(v_2)$  depends on the particle transverse momentum, which can bring insights about the degrees of freedom prevailing in the early stage of the collision. At low collision energies, close to the SIS100 energy range,  $(v_2)$  measurements are only available for pions, protons, antiprotons, charged kaons, with relatively poor precision. The CBM experiment will improve this situation by measuring the flow of identified particles including multistrange hyperons and di-leptons. On the other hand, one of the main goals is to measure the flow of particles not significantly suffering from re-scattering like hyperons or mesons, for which no experimental data exist. These measurements will significantly contribute to our understanding of the QCD matter equation of state at neutron star core densities [12].

#### 1.5.3 Lepton pairs

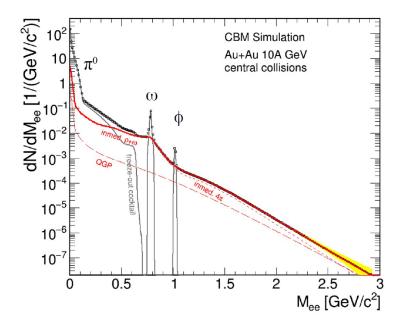

One of the most important goals of heavy-ion collision experiments is the search for signatures of chiral symmetry restoration at very high baryon-net densities and temperatures. Di-leptons offer a unique opportunity to investigate the microscopic properties of strongly interacting matter. Virtual photons are radiated off during the whole time evolution of a heavy-ion collision. Once produced, they decouple from the collision zone and materialize as muon or electron pairs. Hence, leptonic decay channels offer the possibility to look into the fireball and to probe the hadronic currents of strongly interacting systems in a state of high temperature and density. The degeneration of the spectral functions of chiral partners, such as the  $\rho$ -meson and the  $a_1$ -meson, is a consequence of the restoration of the chiral symmetry. While the  $a_1$ -meson is very difficult to measure in the nuclear medium, the in-medium spectral function of the  $\rho$ -meson is accessible via the measurement of its decay into lepton pairs [22]. Moreover, the excess yield of lepton pairs in the energy range ( $M \leq 1 \text{ GeV/c}^2$ ) is sensitive to the temperature of the created matter and its space-time extension. This observable should be sensitive to chiral symmetry restoration, and it is expected to be a measure of the fireball lifetime. Figure 1.10 shows the invariant-mass spectrum of  $e^+e^-$  pairs radiated from a central Au + Au collision at 10 AGeV. The slope of the di-lepton invariant-mass spectrum between 1 and 2.5 GeV/c<sup>2</sup> directly reflects the average temperature of the fireball [23]. The solid red curve shows the contribution of the thermal radiation, which includes in-medium  $\rho$ ,  $\omega$ , 4- $\pi$  spectral functions and QGP spectrum calculated using the many-body approach. The freeze-out hadron cocktail, represented with a solid grey curve, is calculated using the Pluto event generator and includes two body and Dalitz decays of  $\pi^0$ ,  $\omega$  and  $\phi$ .

Figure 1.10: Invariant-mass spectrum of  $e^+e^-$  pairs radiated from a central Au + Au collision at 10 AGeV [12].

Heavy ion collision experiments have no data measured in the range of energies between 2 and 40 AGeV. The CBM experiment will perform pionering multi-differential measurements of lepton pairs over the whole range of invariant masses emitted from a hot and dense fireball. The main experimental challenges are the very low signal cross sections, decay probabilities in the order of  $10^{-4}$  and high combinatorial background [12].

#### 1.5.4 Strangeness and hypernuclei

High precision measurements of excitation functions of multi-strange hyperons in symmetric nucleus-nucleus collisions at SIS100 energies will allow to study the degree of equilibration of the fireball, and, hence, open the possibility to find a signal for the onset of deconfinement in QCD matter at high net-baryon densities. Strangeness production is an essential observable with possible connection to a phase transition.

According to hadronic transport models, which do not feature a partonic phase, multi-strange anti-hyperons are produced in sequential collisions involving kaons and lambdas, therefore, they are sensitive to the density in the fireball. This sensitivity is largest at beam energies close to, or even below, the production threshold in elementary collisions and is expected to shed light on the compressibility of nuclear matter.

The CBM experiment will open a new era of multi-differential precision measurements of strange hadrons including multi-strange hyperons. The expected particle yields will be sufficient to study,

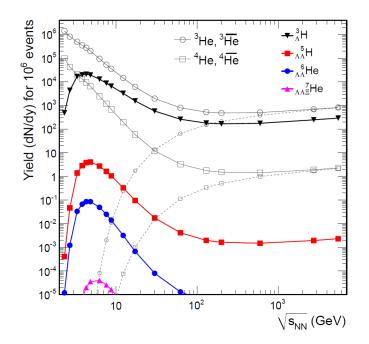

Figure 1.11: Energy dependence of predicted hypernuclei yields at mid-rapidity for  $10^6$  central collisions. The predicted yields of <sup>3</sup>He and <sup>4</sup>He nuclei are included for comparison, along with the corresponding antinuclei (dashed lines) [12].

with excellent statistical significance, the production and propagation of heavy strange and antistrange baryons up to  $\Omega^+$  in dense nuclear matter. It will also open possibilities to identify excited hyperon states and to study hyperon-nucleon and hyperon-hyperon correlations in order to explore the role of hyperons in neutron stars, helping to reconcile the measured masses of neutron stars with the presence of hyperons in their interiors (the so-called hyperon puzzle).

Thermal model calculations show that the maximum of the hypernuclei excitation function is at SIS100 energies, see Fig 1.11. This is due to the superposition of two main effects: the increase of light nuclei production with decreasing beam energy, and the increase of hyperons production with increasing beam energy [24]. The CBM experiment has also substantial discovery potential for light double- $\Lambda$  hypernuclei. Information about hyperon-hyperon and hyperon-nucleon interaction can be deduced from measuring double- $\Lambda$  hypernuclei and their lifetimes, which will further our understanding of the nuclear matter EOS at high densities.

#### 1.5.5 Open and hidden charm

Particles containing charm quarks are expected to be created in the very first stage of the reaction, and, therefore, offer the possibility to probe the degrees-of-freedom over the entire collision history. Depending on their interaction with the medium, the charm and anti-charm quarks hadronize into D mesons, charmed baryons, or charmonium [25].

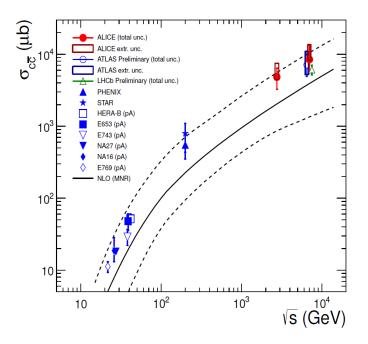

There is no available data on open and hidden charm production in heavy-ion collisions at beam energies below 158 AGeV. The interpretation of existing data is complicated due to the lack of knowledge of interactions between charmed particles and the cold hadronic medium [12]. Figure 1.12 shows the energy dependence of the total nucleon-nucleon charm production cross section. In case of proton-nucleus (pA) or deuteron-nucleus (dA) collisions, the measured cross sections have been scaled down by the number of binary nucleon-nucleon collisions calculated in a Glauber model of the proton-nucleus or deuteron-nucleus collision geometry. The NLO MNR calculation (and its uncertainties) is represented by solid (dashed) lines [26].

Figure 1.12: Energy dependence of the total nucleon-nucleon charm production cross section [26].

With CBM-SIS100, hidden and open charm production will be studied for the first time in proton-induced reactions at beam energies close to production threshold (up to 29 GeV) and different targets. At these energies, the formation time of charmonium is small compared to the lifetime of the reaction system. Systematic measurements of open charm will shed light on the charmonium interaction with cold nuclear matter and constitute an important baseline for measurements in nuclear collisions.

In a deconfined medium, charmonium states are expected to dissociate into c and  $\bar{c}$  quarks due to color screening effects. This has been the first predicted signature for the QGP formation [25]. At SIS100, charmonium will be measured in collisions of symmetric nuclei up to 15 AGeV and, more challenging even, below threshold in Au + Au collisions at 10 AGeV. In order to detect this specific observable, very high interaction rates and a dedicated experimental configuration, optimized for the identification of the  $J/\psi$ , will be used in the CBM experiment [12].

### **1.6** The CBM experimental setup

The CBM experiment possesses a wide and challenging physics program. Many of the important observables are rare diagnostic probes carrying the information of the dense stage of the fireball evolution. The CBM detector system is designed to measure the collective behavior of hadrons, together with rare diagnostic probes such as multi-strange hyperons, charmed particles and vector mesons decaying into lepton pairs with unprecedented precision and statistics. Most of these particles will be studied for the first time in the FAIR energy range. In order to achieve the required precision, the measurements will be performed at reaction rates up to 10 MHz. This requires very fast and radiation hard detectors, a novel data readout and analysis concept including free streaming

#### 1.6. THE CBM EXPERIMENTAL SETUP

front-end electronics, and a high performance computing cluster for online event selection [15].

The CBM detector has an angular acceptance between  $2.5^{\circ}$  and  $25^{\circ}$  to cover mid and forward rapidity hemisphere for symmetric collision systems at beam energies between 2 and 40 AGeV. The estimated data rate for the whole experiment in Au + Au collisions is approximately 1 TB/s, therefore, fast algorithms for reconstruction and event selection will be performed in real time in order to reduce by two order of magnitude the stored data.

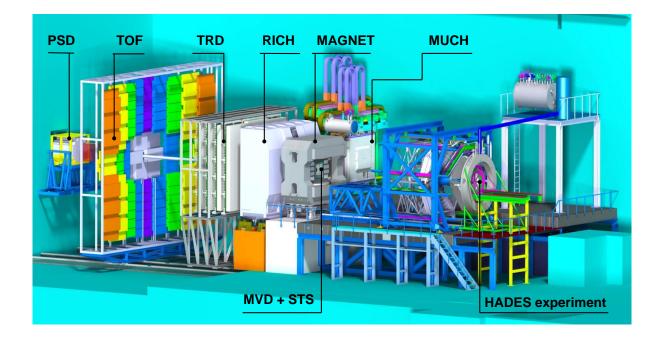

Figure 1.13: The CBM experimental setup as part of the FAIR facility.

The full schematic view of the CBM experimental setup concept, including the HADES (High-Angle Di-Electron Spectrometer) experiment, is shown in Fig. 1.13. It comprises the following subsystems:

- a dipole magnet for momentum measurements;

- a Micro Vertex Detector (MVD) to measure short-lived decay vertices and low-momentum particles;

- a Silicon Tracking System (STS) to provide tracking of charged particles and to measure their momentum;

- a Muon Chamber (MUCH) for muon identification and track reconstruction;

- a Ring Imaging Cherenkov detector (RICH) to provide electron/pion identification;

- a Transition Radiation Detector (TRD) to suppress pions and to support track reconstruction;

- a Time-of-Flight (ToF) wall for hadrons identification;

- a Projectile Spectator Detector (PSD) for the collision centrality and event plane determination.

#### 1.6. THE CBM EXPERIMENTAL SETUP

The CBM detector system can be used in two operation modes: the first one is optimized for electron identification (all the subsystems apart from MUCH will be involved) and the second is specialized for muon identification (the RICH detector will be replaced by MUCH).

#### Superconducting dipole magnet

The superconducting dipole magnet serves to bend charged particle trajectories in order to determine their momenta. The device is essential for particle momenta determination of all charged particles for the CBM experiment. It will be superconducting in order to reduce the operation costs. The superconducting dipole magnet provides a vertical magnetic field with a field integral of 1 Tm from the interaction point to approximately 1 m downstream the target [27].

#### Micro Vertex Detector (MVD)

The main task of the MVD is to distinguish between primary vertex and displaced vertices, for example, to reconstruct decays of charmed hadrons: D-mesons or  $\Lambda_c$  baryons. This task requires a high resolution along the position vector of approximately 70  $\mu$ m, which turns to 5  $\mu$ m spatial resolution and low material budget.

The MVD is located directly behind the target (5 - 20 cm downstream) inside the dipole magnet. The MVD is placed in vacuum, thus it is able to reconstruct low-momentum tracks that helps to reject background for di-electrons [28]. Due to the limited readout speed, the MVD will participate only in data taking with the interaction rate up to  $10^5$  Hz [28, 29]. The requirements of high spatial resolution, low material budget and high radiation tolerance are fulfilled with CMOS Monolithic Active Pixel Sensors (MAPS) with fine pixel size of several dozens of  $\mu$ m. Being operated in the target chamber vacuum, the sensors need to be cooled, with the total anticipated power of 300 W.

#### Muon Chambers Detector (MUCH)

The experimental challenge for muon measurements in heavy ion collisions at FAIR energies is to identify low-momentum muons in an environment of high particle densities [15]. It is experimentally challenging to identify low-momentum muons in heavy ion collisions due to the high particle multiplicity [15]. The reconstruction of di-muon decay channels of vector mesons like  $\rho$ ,  $\omega$ ,  $\phi$  and  $J/\psi$  requires a very precise muon identification. The MUCH system in combination with STS are the main detectors in CBM to perform this task [30]. The MUCH is located downstream the STS detector and it will be replacing the RICH detector in the CBM muon configuration. It will be operated in different setup configurations by varying the positions of the absorber-detector combinations. The design of the MUCH detector system consists of 5 hadron absorber layers (60 cm thick carbon plate followed by four iron plates of 20 cm, 20 cm, 30 cm and 100 cm thickness) and several gaseous tracking chambers located in triplets behind each iron slab. The tracking planes are based on Gas Electron Multiplication (GEM) [31] and Resistive Plate Chambers (RPC) detectors.

#### **Ring-Imaging Cherenkov Detector (RICH)**

The RICH detector is designed to provide identification, via Cherenkov radiation [32], of electrons and suppression of pions in the momentum range below 8 GeV/c. The electron identification efficiency reaches values above 85% and the suppression factor for pions is above 300, which in combination with TRD will allow to reduce drastically the pion contamination. The RICH detector, located behind the dipole magnet, about 1.6 m downstream of the target, will be used in the electron-hadron configuration of the CBM setup. The detector design consist of a 1.7 m long  $CO_2$  gas radiator and two arrays of mirrors and photo detector planes. The gas constituents and its pressure are chosen to cover the largest possible momentum range. The photo detector planes are based on Multi-Anode Photo-Multipliers (MAPMTs) (Hamamatsu H12700) in order to provide high granularity, high geometrical acceptance and high photon detection efficiency. In order to direct the light to the high granularity photon detectors the mirrors of the RICH detector are constructed with a reflective  $Al + MgF_2$  coating [33].

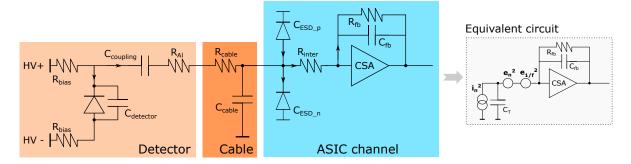

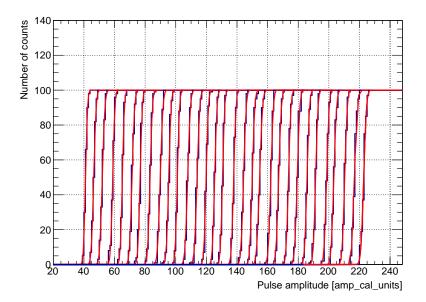

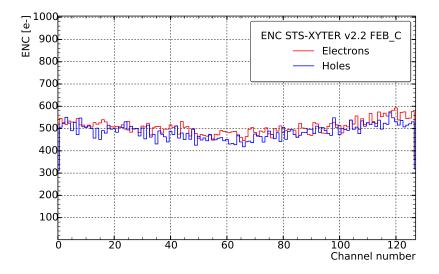

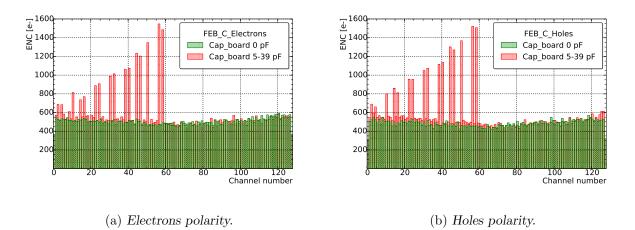

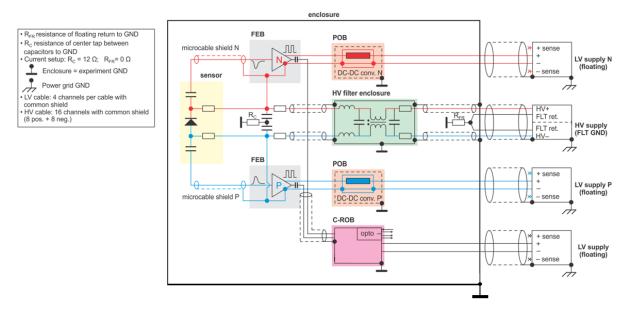

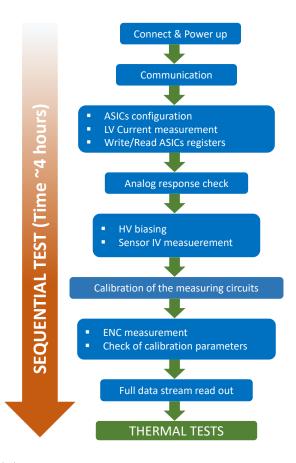

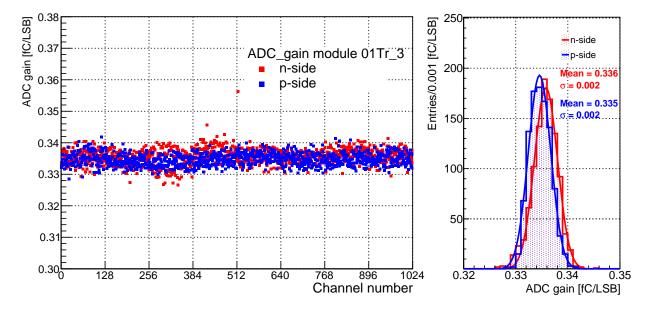

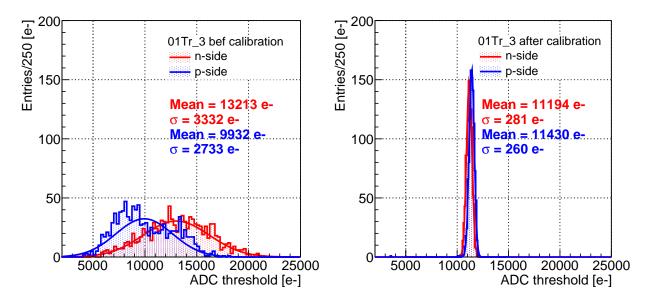

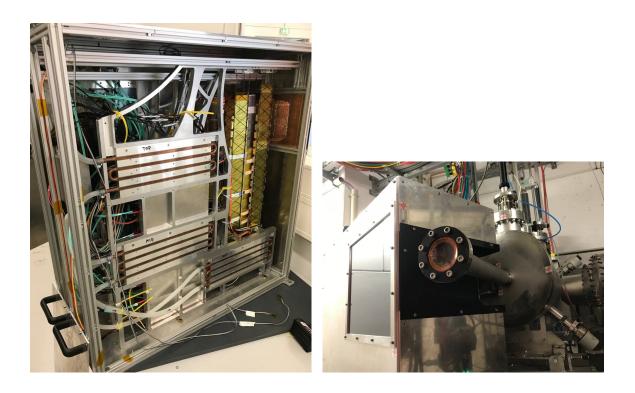

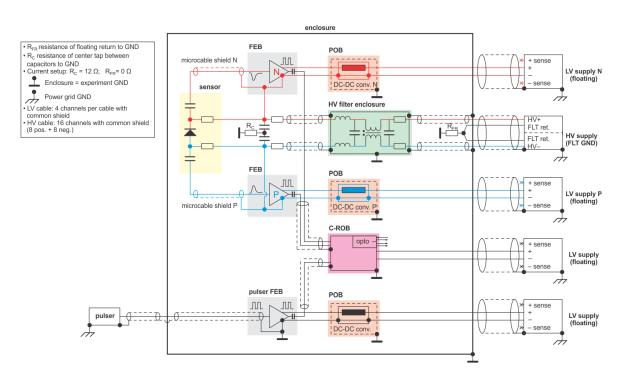

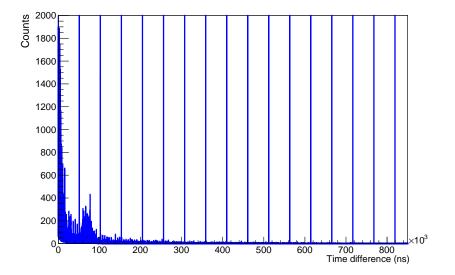

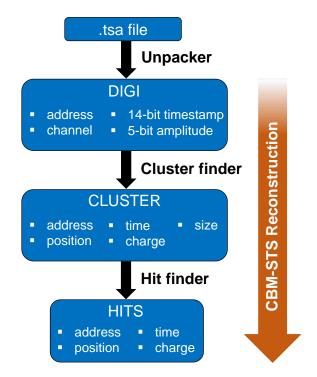

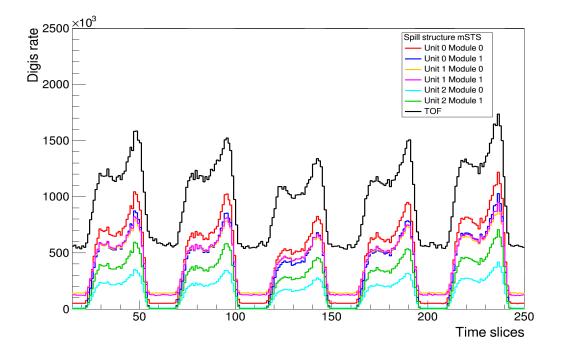

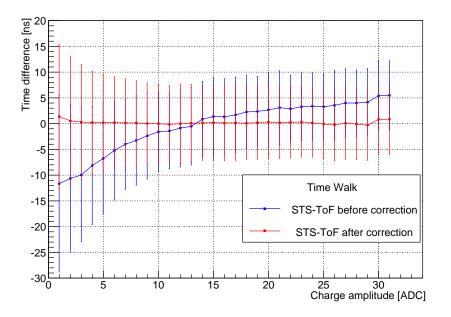

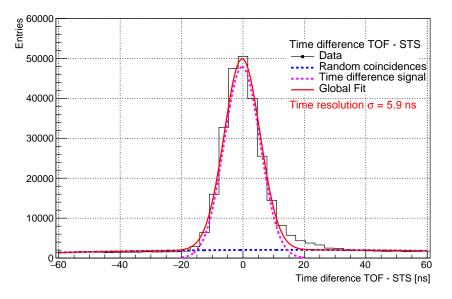

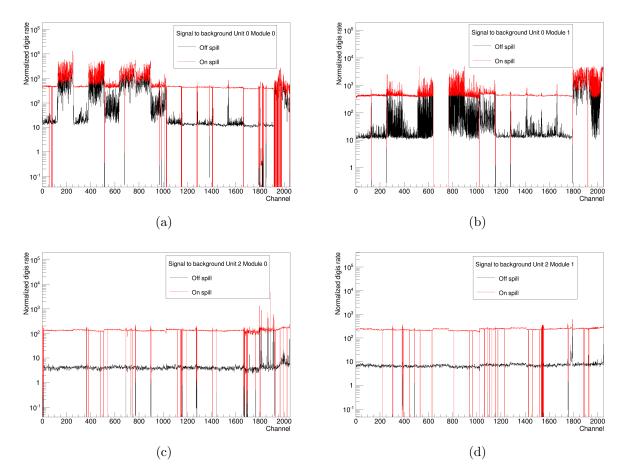

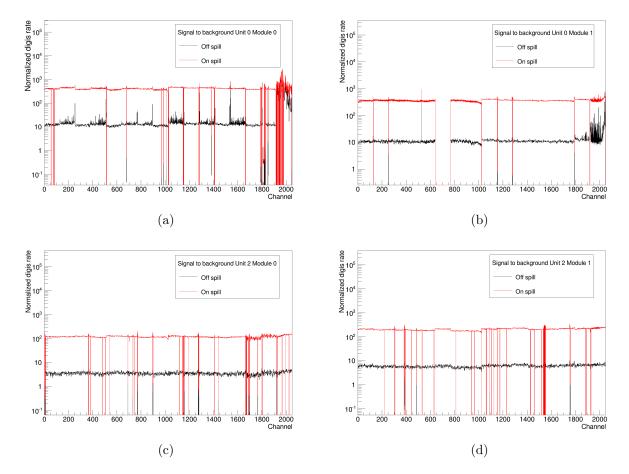

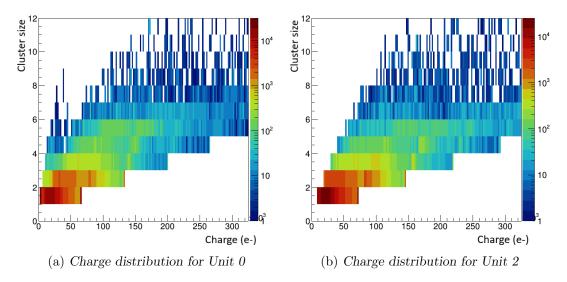

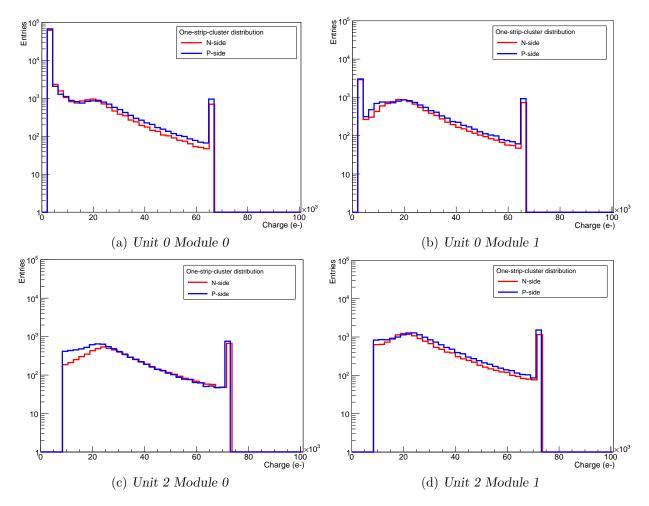

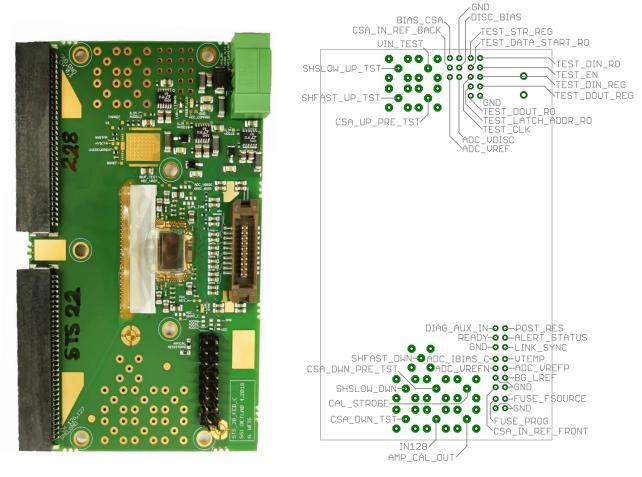

#### Transition Radiation Detector (TRD)