## Requirements

- PANDA specific requirements:

- self triggering

- precise time resolution

- fully digital hit information

- => not many front-end types available to comply with these requirements

| Parameter                    | Value                                                       | Remarks                                   |  |  |  |  |

|------------------------------|-------------------------------------------------------------|-------------------------------------------|--|--|--|--|

| Geometry                     |                                                             |                                           |  |  |  |  |

| width                        | ≤ 8 mm                                                      |                                           |  |  |  |  |

| depth                        | $\leq 8 \text{ mm}$                                         |                                           |  |  |  |  |

| input pad pitch              | $\approx 50 \ \mu \mathrm{m}$                               |                                           |  |  |  |  |

| pad configuration            | lateral pads occupied only for diagnostic functions, should |                                           |  |  |  |  |

|                              | be left unconnected for final setup                         |                                           |  |  |  |  |

| channels per front-end       | $2^6 \dots 2^8$                                             | default: 128 channels                     |  |  |  |  |

| Input Compliance             |                                                             |                                           |  |  |  |  |

| sensor capacitances,         |                                                             |                                           |  |  |  |  |

| fully depleted sensor        |                                                             |                                           |  |  |  |  |

|                              | < 10 pF                                                     | rect. short strips                        |  |  |  |  |

|                              | < 50  pF                                                    | rect. long strips + ganging               |  |  |  |  |

|                              | < 20  pF                                                    | trapezoidal sensor                        |  |  |  |  |

| input polarity               | either                                                      | selectable via slow control               |  |  |  |  |

| input ENC                    | $< 800 e^{-}$                                               | $C_{\rm sensor} = 10 \text{ pF}$          |  |  |  |  |

|                              | $< 1,000 e^{-}$                                             | $C_{\rm sensor} = 25 \text{ pF}$          |  |  |  |  |

|                              | Signal                                                      |                                           |  |  |  |  |

| dynamic range                | $240 \text{ ke}^- (\approx 38.5 \text{ fC})$                |                                           |  |  |  |  |

| min. SNR for MIPS            | 12                                                          | $22,500 e^-$ for MIPs in 300 $\mu m$ sil- |  |  |  |  |

|                              |                                                             | icon, guaranteed within lifetime          |  |  |  |  |

| peaking time                 | $\approx 5 \dots 25 \text{ ns}$                             | typical Si drift times                    |  |  |  |  |

| digitisation resolution      | $\geq 8 \text{ bit}$                                        |                                           |  |  |  |  |

|                              | Power                                                       |                                           |  |  |  |  |

| overall power dissipation    | < 1 W                                                       | assuming 128 channels per front-          |  |  |  |  |

|                              |                                                             | end                                       |  |  |  |  |

|                              | Dynamical                                                   |                                           |  |  |  |  |

| trigger                      | internally generated                                        | when charge pulse exceeds ad-             |  |  |  |  |

|                              |                                                             | justable threshold value                  |  |  |  |  |

| time stamp resolution        | < 20 ns                                                     |                                           |  |  |  |  |

| dead time / ch               | < 6 μs                                                      | baseline restored to $1\%$                |  |  |  |  |

| overshoot recovery time / ch | < 25 μs                                                     |                                           |  |  |  |  |

| average hit rates / ch       |                                                             | derived from simulations at               |  |  |  |  |

| (poissonian mean)            | _                                                           | a beam momentum of 15 GeV/ $c$            |  |  |  |  |

| hot spots                    | $9,000 \text{ s}^{-1}$                                      | $  \overline{p}p$                         |  |  |  |  |

|                              | $40,000 \text{ s}^{-1}$                                     | $\overline{p}Au$                          |  |  |  |  |

| average occupancy            | $6,000 \text{ s}^{-1}$                                      | $\overline{p}p$                           |  |  |  |  |

|                              | $30,000 \text{ s}^{-1}$                                     | $\overline{p}Au$                          |  |  |  |  |

| Interface                    |                                                             |                                           |  |  |  |  |

| slow control                 | any                                                         | low pincount, e.g. I <sup>2</sup> C       |  |  |  |  |

| data                         | sparsified data                                             |                                           |  |  |  |  |

## Technical Design Report for the: **PANDA**

Micro Vertex Detector

PANDA Collaboration

30th November 2011

Section 4.2.1, Table 4.3

## **Options**

- adapted ToPix(3)

- FAIR/STS-XYTER

- (modified) FSSR2

ILC calorimeter development by M. Idzik

## **Options**

- other then the aforementioned?

- => looked through several experiments

- (BNL, JLAB, Fermi-lab, (S)LHC, AMS, ...)

- in most of the cases even the APV25 is more suitable

## **Options**

### Comparison

Technical Design Report for the:

#### **PANDA**

Micro Vertex Detector

PANDA Collaboration

30th November 2011

Section 4.2.2, Table 4.4

| Parameter               | adapted ToPix        | STS-XYTER                               | FSSR2                     |

|-------------------------|----------------------|-----------------------------------------|---------------------------|

| input pad pitch         | $\approx 50 \ \mu m$ | $50~\mu\mathrm{m}$                      | 50 μm                     |

| channels per front-end  | 128                  | 128                                     | 128                       |

| dynamical range         | 100 fC               | 15 fC                                   | 25 fC                     |

| ENC                     | $1,000 e^- @ 20 pF$  | $700 \; { m e^-} \; @ \; 28 \; { m pF}$ | $240 e^{-} + 35 e^{-}/pF$ |

| peaking time            | 6 ns                 | 80 ns                                   | 65  ns                    |

| power consumption       | $0.8~\mathrm{mW/ch}$ | $1.2 \mathrm{\ mW/ch}$                  | 4.0  mW/ch                |

| trigger                 | self-triggering      | self-triggering                         | self-triggering           |

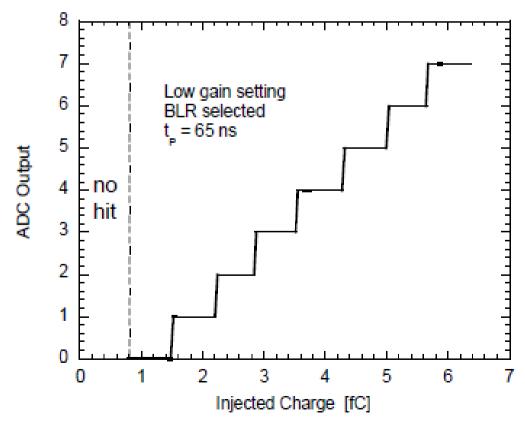

| digitisation technique  | ТоТ                  | ТоТ                                     | Flash-ADC                 |

| digitisation resolution | 10 bit               | 4-6 bit                                 | 3 bit Flash-ADC           |

| time resolution         | 1.85 ns @ 155 MHz    | 1.85  ns @ 155  MHz                     | 132 ns time stamp         |

| data interface          | e-link - SLVS        | up to 2.5 Gbps                          | LVDS                      |

| number of data lines    | 1 pair               | 1 pair                                  | 1 to 6 pairs              |

| slow control            | custom (serial)      | custom                                  | custom LVDS               |

| process                 | 0.13 μm CMOS         | UMC 0.18 μm                             | $0.25~\mu\mathrm{m}$ CMOS |

| radiation hardness      | > 10 MRad            | 10 MRad                                 | up to 20 MRad             |

|                         |                      |                                         |                           |

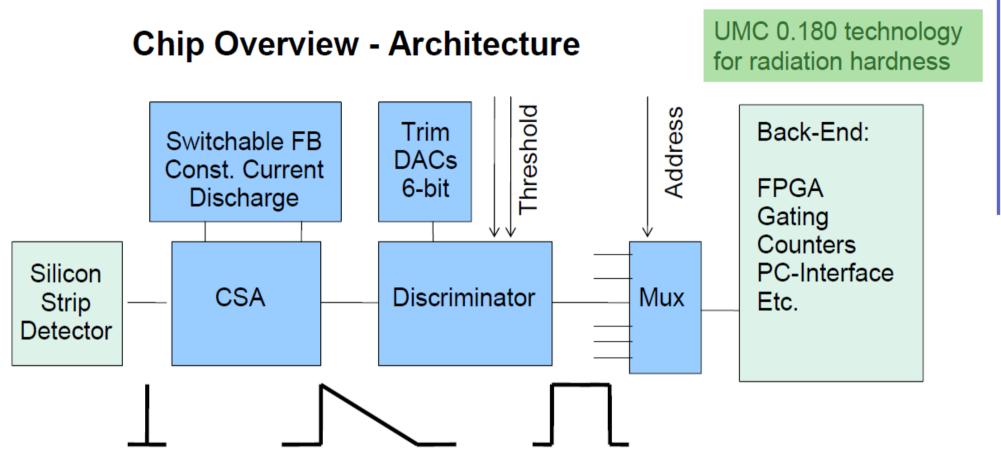

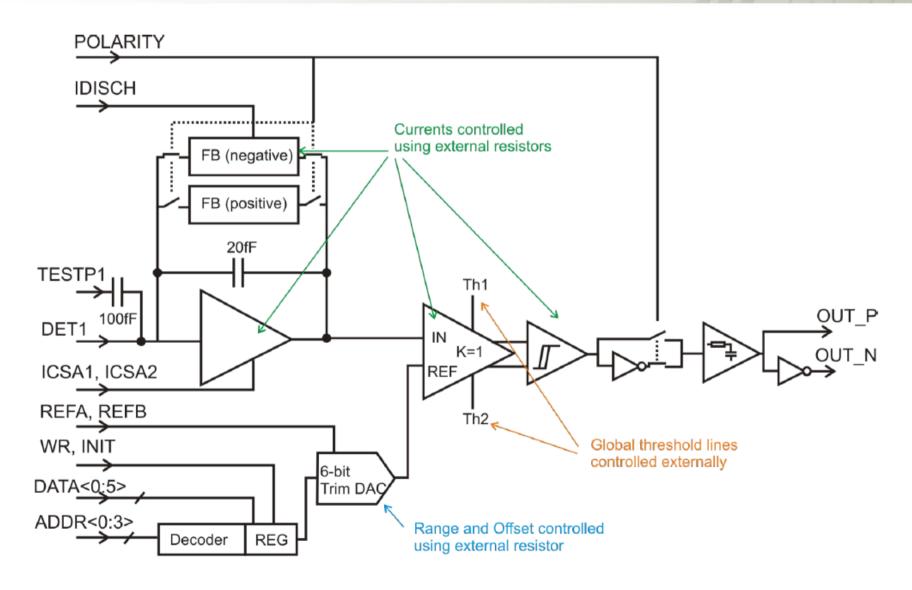

## STS-XYTER

- development by R. Szczygiel et al., AGH

Krakow in early prototype state

- self triggered architecture

- low power and low resolution dedicated for silicon strip detectors

- ToT-based digitization

#### Low Power STS-XYTER in Second Iteration

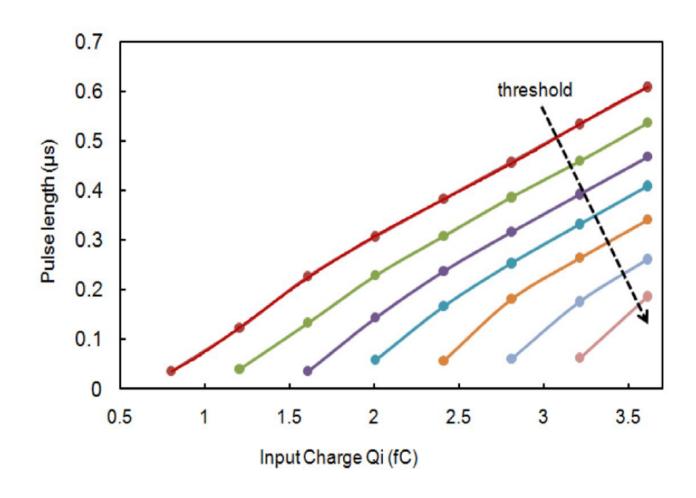

- Time over threshold energy conversion (ToT)

- 2.3 mW/channel at 500 ENC/30pF (c.f. ~20mW on n-XYTER)

- 4 to 6 bit resolution

we favor high resolution

- 30 channels

R. Szczygiel et al., AGH Krakow

## STS-XYTER

- latest test results as of January 2012

- shown on CBM FEE/DAQ/FLES Workshop

#### TOT01 -> TOT02 evolution

#### **Major modifications:**

- -> added digital back-end (fast serial interface)

- -> rad-hard layout of AFE (ELT NMOS transistors)

- -> improved CSA core (boosted folded cascode)

- -> improved constant-current FB (more linear at low charges)

#### Design parameters:

- -> optimized for low noise ~750 e- @30pF AC-coupled detector

- -> power consumption: 2.1 mW / analogue channel

- -> peaking time: ~80 ns

- -> Technology: UMC 180nm CMOS 1.8V

- -> 16 channels, 50 μm pitch

# Issues discovered during TOT01 development and tests

#### Remedies:

- -> reduce operation of the feedback current mirror below Vdsat

(reduce the Vdsat by increasing W/L while keepeing the parameters of the mirror at acceptable level)

- -> increasing gain of the CSA core (using boosted folded-cascode amplifier)

### **Parameter summary**

| Die parameters                                                  |                            |                                  |                                         |  |  |  |

|-----------------------------------------------------------------|----------------------------|----------------------------------|-----------------------------------------|--|--|--|

| Technology                                                      | UMC 180 nm<br>CMOS         | Die size                         | 1.5 mm x 1.5 mm<br>2.25 mm <sup>2</sup> |  |  |  |

| Number of pads /<br>channels                                    | 56 / 16                    | Channel pitch / length           | 50 μm / 820 μm                          |  |  |  |

| Measured chip performance                                       |                            |                                  |                                         |  |  |  |

| No detector (C <sub>d</sub><br>ASIC#1                           | <sub>et</sub> =0pF),       | 2cm detector (Cdet=3pF), ASIC#2  |                                         |  |  |  |

| Voltage gain                                                    | =55 mV/fC<br>+-0.36 mV/fC  | Voltage gain                     | =54.7 mV/fC<br>+-0.64 mV/fC             |  |  |  |

| Time gain                                                       | =216 ns/fC<br>+-7.54 ns/fC | Time gain                        | =198 ns/fC<br>+-8.97 ns/fC              |  |  |  |

| ENC <sub>thr.scan</sub>                                         | 196 e-                     | ENC <sub>thr.scan</sub>          | 240 e-                                  |  |  |  |

| ENC <sub>tot.scan</sub>                                         | 286 e-                     | ENC <sub>tot.scan</sub>          | 350 e-                                  |  |  |  |

| Measured static power consumption                               |                            |                                  |                                         |  |  |  |

| CSA                                                             | 1.25 mW                    | Semi-digital back-end            | 330 μW                                  |  |  |  |

| Discriminator +<br>DAC                                          | 530 μW                     | Total (w/o digital back-<br>end) | 2.1 mW/channel                          |  |  |  |

| Simulated performance of the CSA core (not directly measurable) |                            |                                  |                                         |  |  |  |

| Gain                                                            | 7000 V/V                   | Bandwidth                        | 1.3 MHz                                 |  |  |  |

| GBW                                                             | 9 GHz                      |                                  |                                         |  |  |  |

#### Noise:

#### (thr scan)

ENC=196+14.6\*Cdet ENC@30pF = 634 e-

#### (tot scan)

ENC=286+21.3\*Cdet ENC@30pF = 925 e-

#### Pros & cons

#### Pros:

- infinite dynamic range

- low power consumption

- simple architecture

#### Cons:

- sensitivity to leakage currents

- pulse length dependant on signal amplitude

- wideband → noise

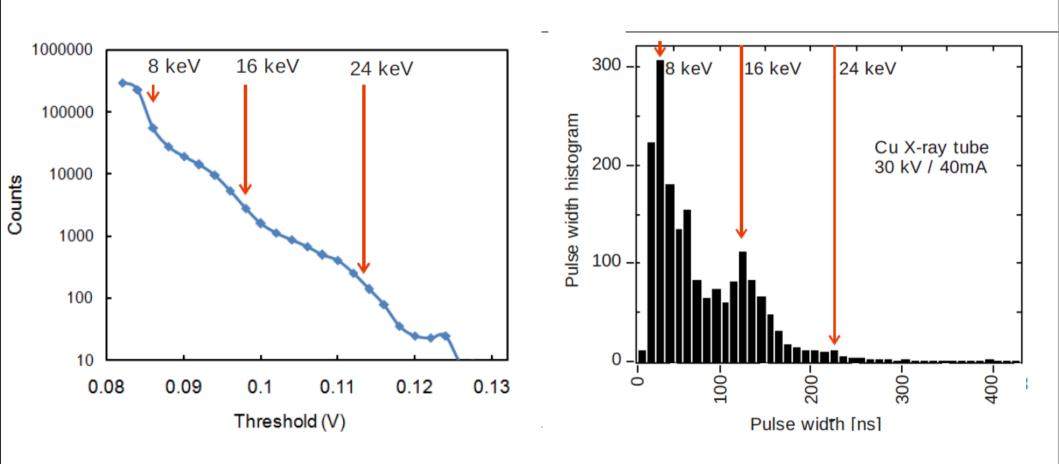

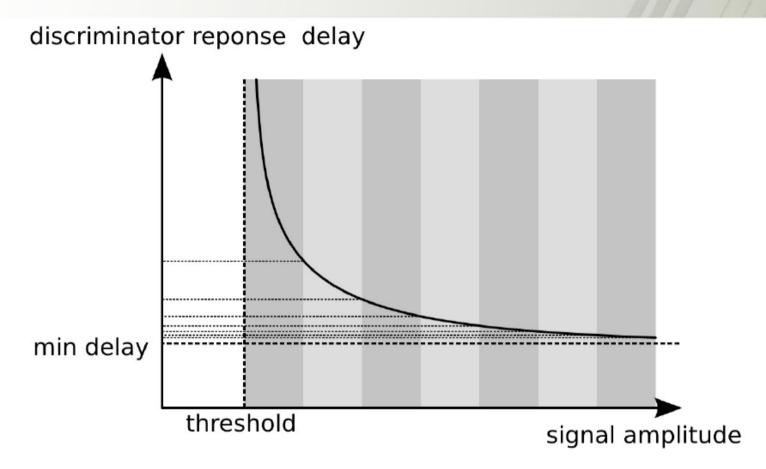

- timewalk (timestamp precision vs noise)

## STS-XYTER

- Designer not happy with:

- time resolution (time walk)

- threshold dispersion

- reasons are due to a mixture of:

- noise level of CBM sensors + long cables

and

- low signals time walk

- => new architecture for STS ASIC!!

## STS ASIC working specifications

- 128 channels

- CBMnet backend

- Linear range 1-12 fC (typical input charge = 2 fC)

- Power < 10 mW / channel</li>

- Time measurement < 10 ns resolution</li>

- Detector: DC (AC?), 30 pF total capacitance

- Dual polarity

- Recovery from overload

- Leakage current compensation

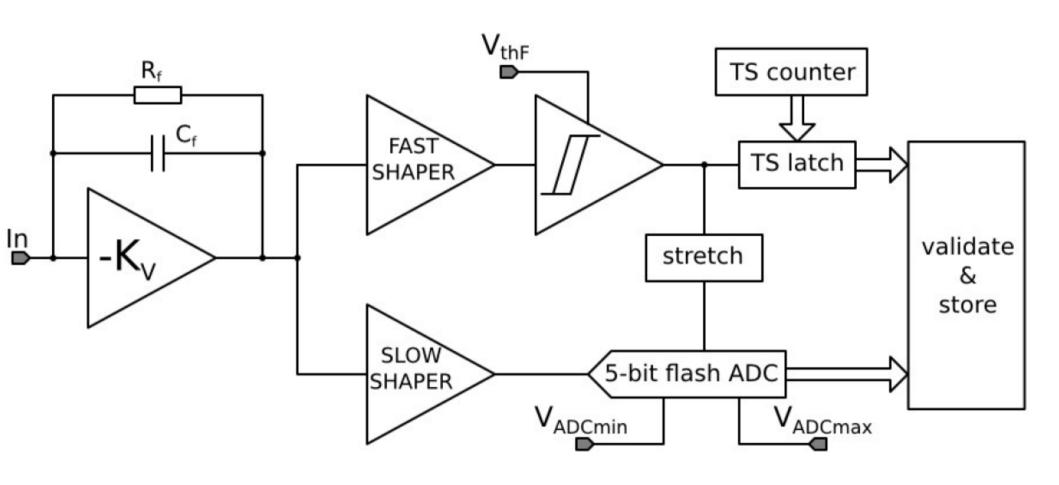

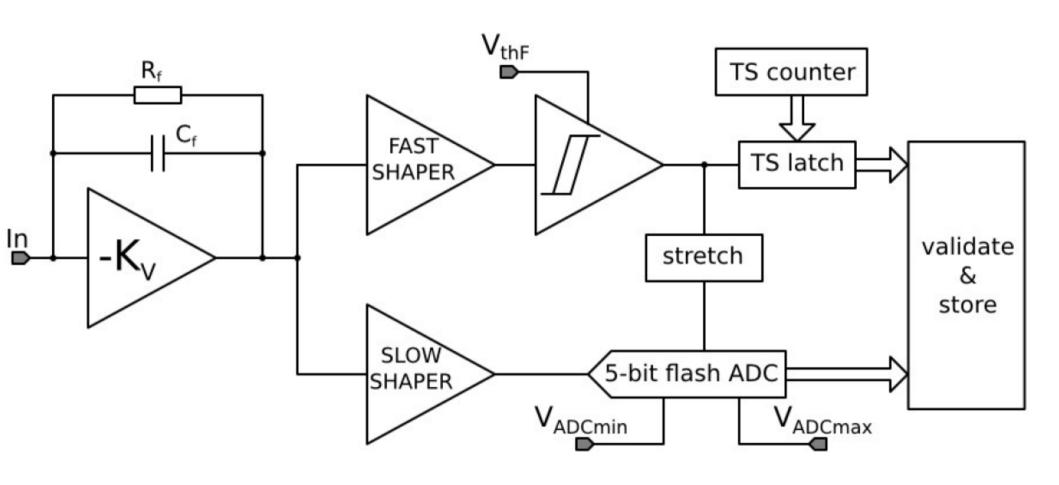

## Block diagram of a single channel

$V_{thF}$  <  $V_{ADCmin}$  -> the time measurement is validated by the energy measurement – worst cases dropped

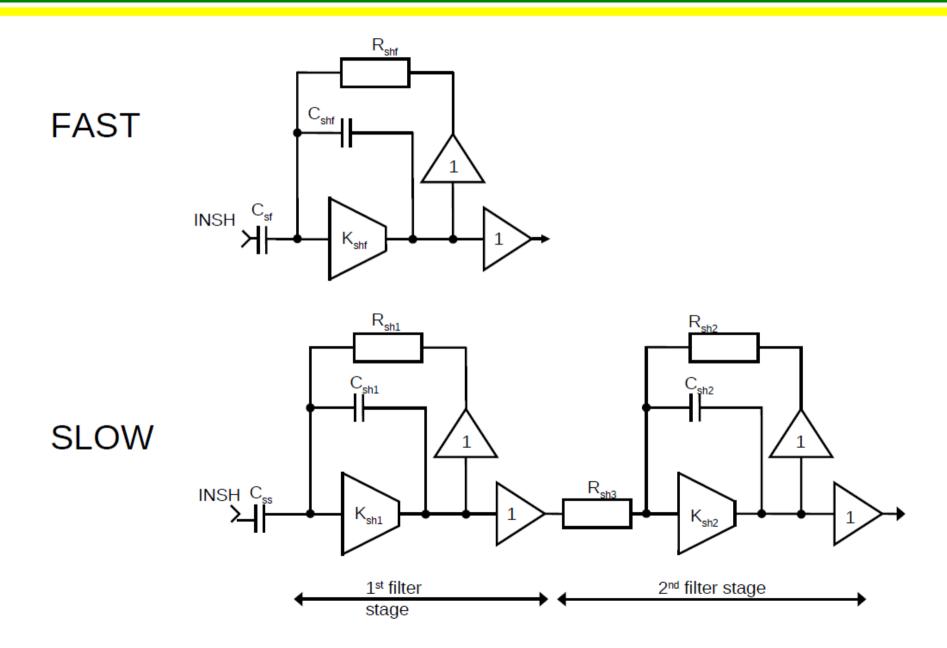

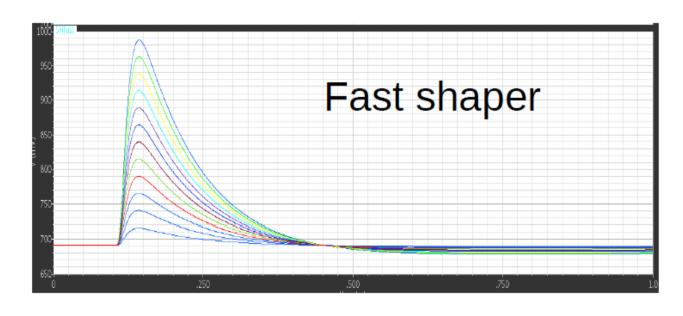

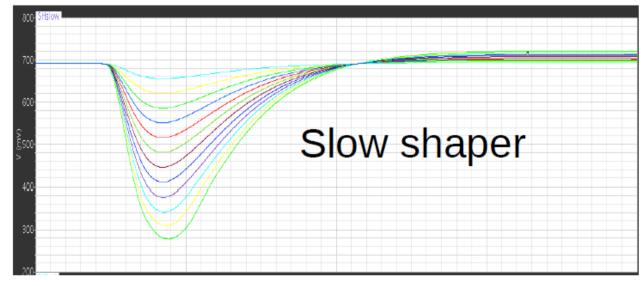

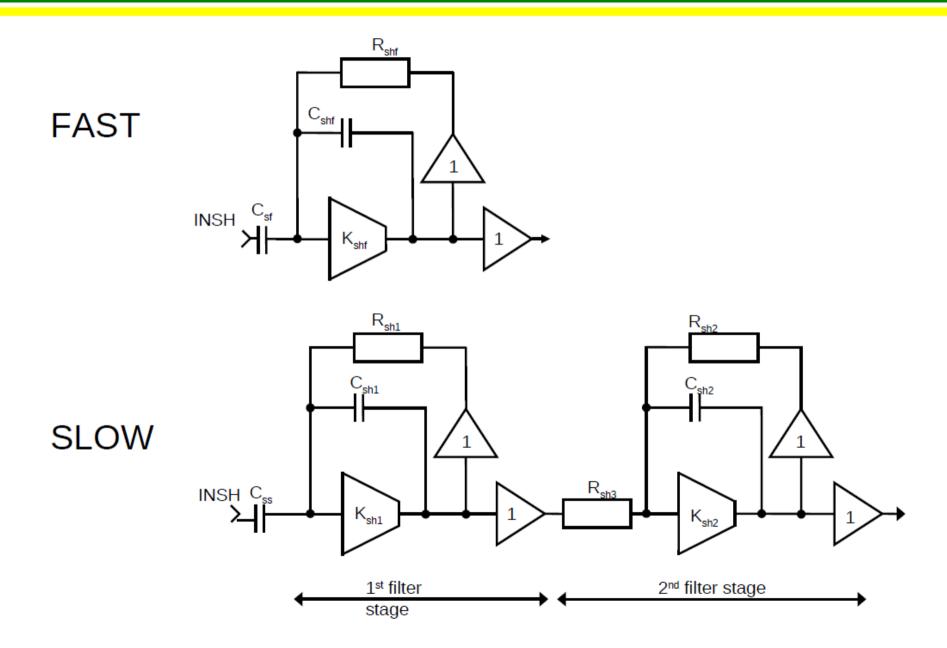

## Fast CR-RC and slow CR-(RC)<sup>2</sup> shapers

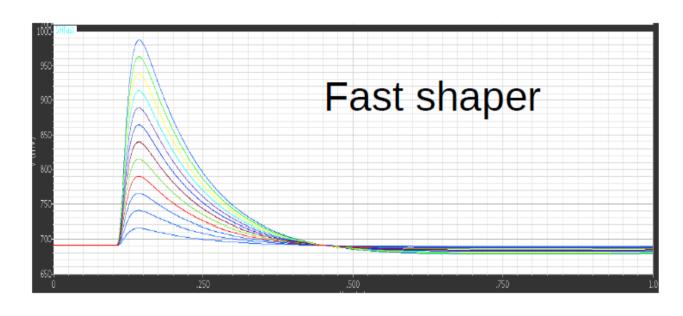

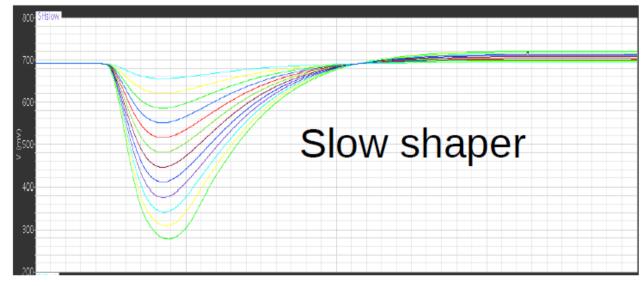

## Timing and ENC: Qin = 1-12fC, PWR =5.5mW

Tp = 38ns ENC = 1020 el

Tp = 95ns ENC = 624 el

Only simulation!!!

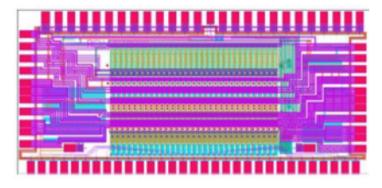

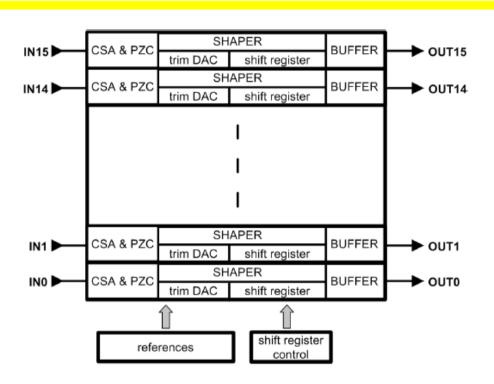

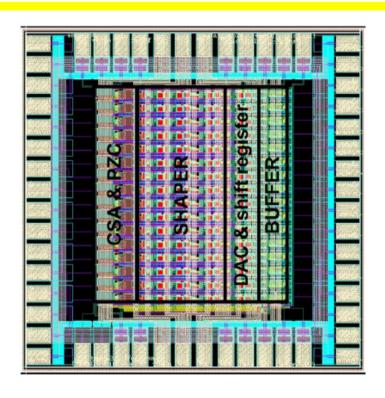

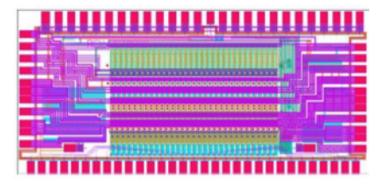

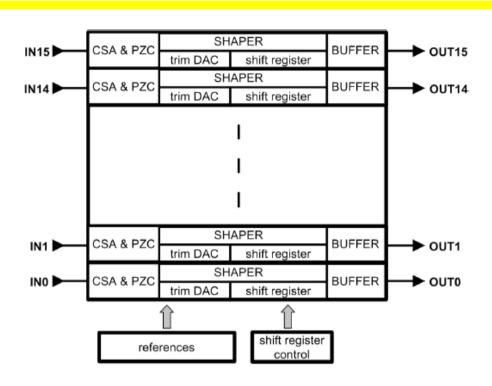

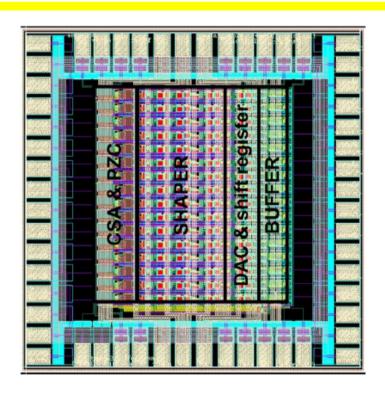

### Our prototype: FSDR16 chip, tested 2011/2012

#### FSDR16 - features:

- · implemented in UMC 180nm CMOS,

- · dedicated for silicon strip detectors,

- two programmable shaper types which allow to make a comparison between typical CR-(RC)<sup>5</sup> shaper based on real poles and a nearly true Gaussian shaper based on complex poles,

- two switchable peaking time tp for each of shaper types

#### FSDR16 - block diagram:

- · contains 16 channels,

- 16 analog inputs, 16 analog outputs,

- single channel is built with an analog (CSA, PZC, shaper) and digital (shift register) part

- DC voltage shaper output spread is corrected by a 7-bit trim DAC separately in ech channel.

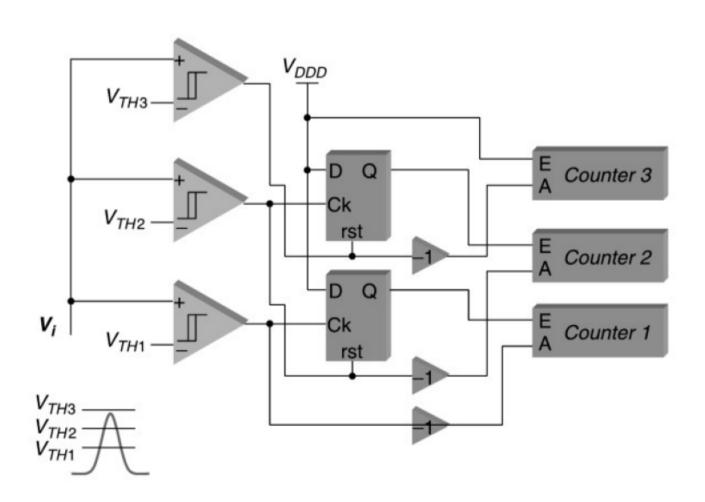

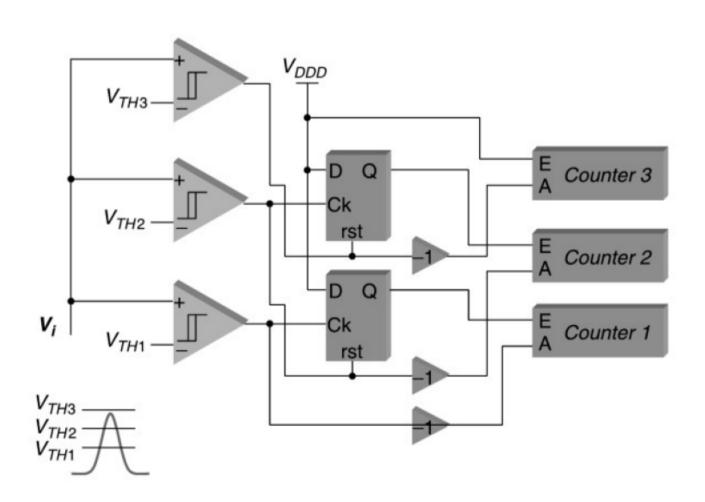

## Energy measurements: 5-bit flash ADC

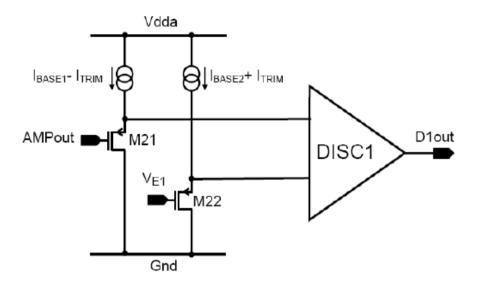

### Small discriminator

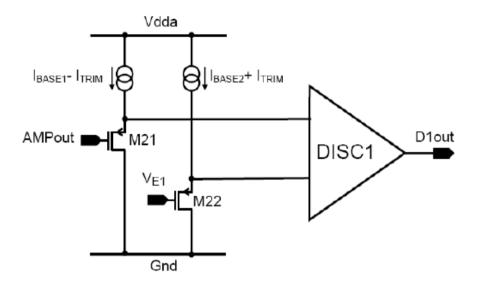

### Option 1: discriminator with trimming

Area:  $20 \times 50 \text{ um}^2$ ( $40 \times 50 \text{ um}^2 \text{ with register}$ )

PWR: 10 – 20 uW

Option 2: discriminator with automatic offset cancellation

### Conclusions

- Separated channels for time and amplitude measurements independent optimization for timestamp precision and noise

- Expected better noise than ToT

- Expected better timing precision than ToT

- Needs more power than ToT

- Possible time measurement correction using ADC value

- Most components of well known architecture (CSA, shapers, discriminators, trimming DACs)

Deadline: July 2012

## STS-XYTER

- ToT-version results were actuallynot bad

- noise of 925e @30pF

- 2,1 mW per channel (analog part only)

- STS-XYTER primary development for CBM

- CBMnet backend (can be deactivated)

- => option dropped in ranking

## ToPix3

- adaptation of analog circuits for strip detectors

- would provide comparable readout structures between pixel and strip part

- work by Alberto Potenza, Turin showed feasibility

- how can we bring it on?

## Summary

- front-end decision needed urgent

- decision needed in order to specify:

- hybrid design

- power and cooling rating

- interface to module controller

- slow control

AGH UNIVERSITY OF SCIENCE AND TECHNOLOGY

## **TOT02** STS prototype readout ASIC status

Robert Szczygieł,

Krzysztof Kasiński,

Paweł Gryboś

robert.szczygiel@agh.edu.pl

kasinski@agh.edu.pl

pawel.grybos@agh.edu.pl

Department of Measurement and Instrumentation AGH - UST Kraków, Poland

CBM FEE/DAQ/FLES Workshop January 25-27, 2012 ZITI, University of Heidelberg

#### **Agenda**

- TOT01 -> TOT02 evolution (improvements)

- Problems discovered with TOT01 ASIC and remedies for them

- Methodology, test setup, error sources

- Measurements and results

- Summary and conclusions

#### TOT01 -> TOT02 evolution

#### **Major modifications:**

- -> added digital back-end (fast serial interface)

- -> rad-hard layout of AFE (ELT NMOS transistors)

- -> improved CSA core (boosted folded cascode)

- -> improved constant-current FB (more linear at low charges)

#### Design parameters:

- -> optimized for low noise ~750 e- @30pF AC-coupled detector

- -> power consumption: 2.1 mW / analogue channel

- -> peaking time: ~80 ns

- -> Technology: UMC 180nm CMOS 1.8V

- -> 16 channels, 50 μm pitch

# Issues discovered during TOT01 development and tests

#### Remedies:

- -> reduce operation of the feedback current mirror below Vdsat

(reduce the Vdsat by increasing W/L while keepeing the parameters of the mirror at acceptable level)

- -> increasing gain of the CSA core (using boosted folded-cascode amplifier)

### **TOT02** overview - reminder

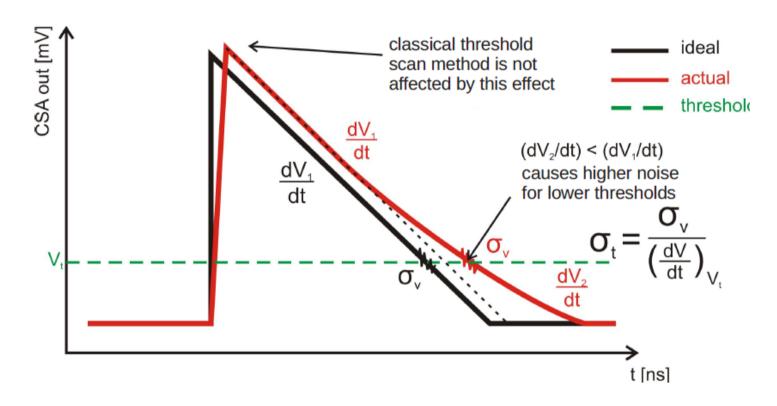

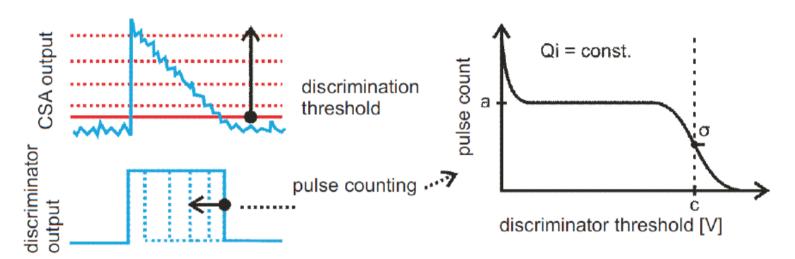

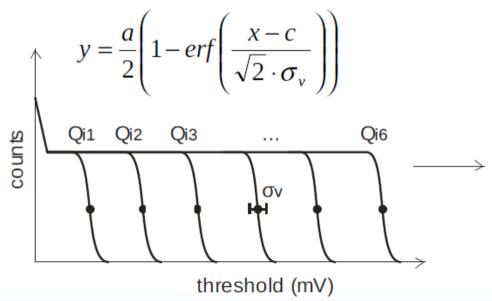

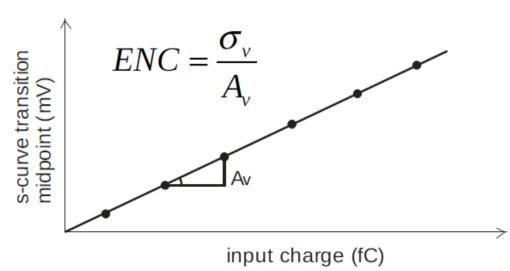

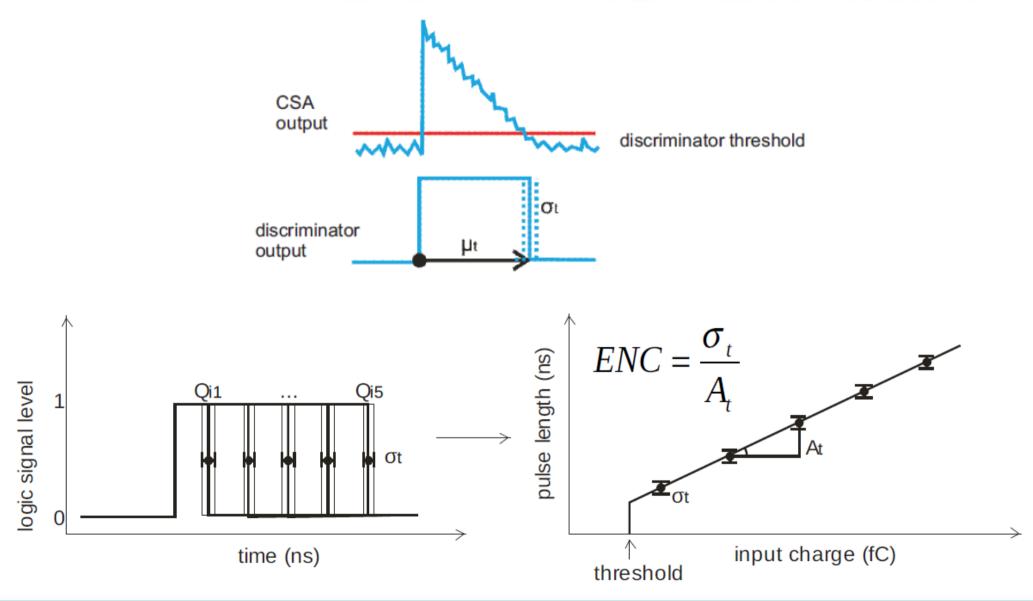

# Methodology of characterization THRESHOLD SCAN

# Methodology of characterization TOT SCAN

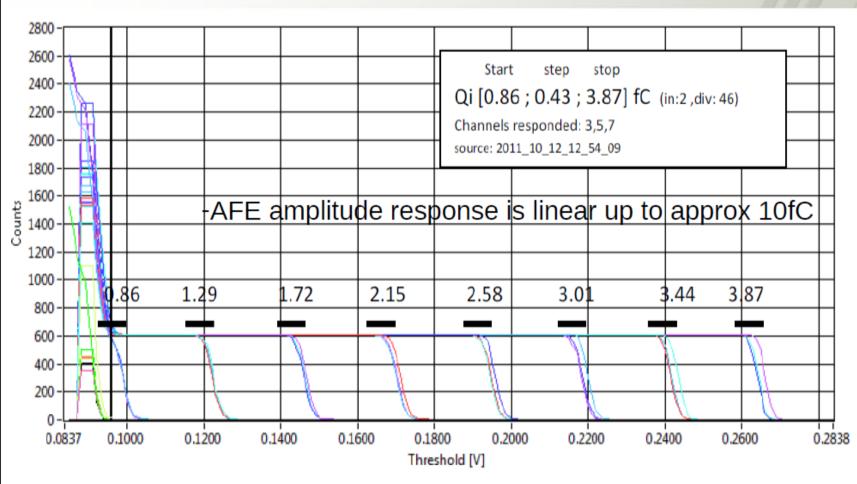

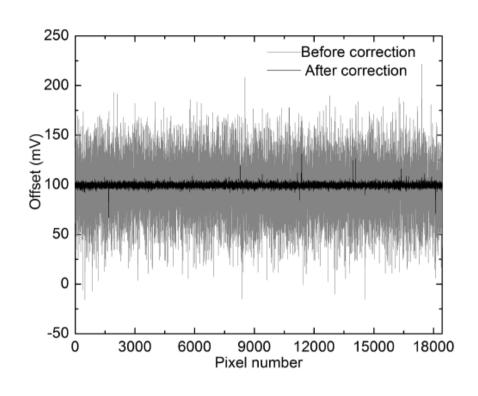

#### Characteristics - threshold scan

DC offset spread before correction

5.77 mV 654 eDC offset spread after correction

< 0.33 mV < 37.4 e-

### **Characteristics - ToT scan**

### X-ray irradiation

Tube parameters: Cu, V=40kV, I=40mA

## **Parameter summary**

| Die parameters                                                  |                                   |                                  |                                         |  |  |  |  |

|-----------------------------------------------------------------|-----------------------------------|----------------------------------|-----------------------------------------|--|--|--|--|

| Technology                                                      | UMC 180 nm<br>CMOS                | Die size                         | 1.5 mm x 1.5 mm<br>2.25 mm <sup>2</sup> |  |  |  |  |

| Number of pads /<br>channels                                    | 56 / 16                           | Channel pitch / length           | 50 μm / 820 μm                          |  |  |  |  |

|                                                                 | Measured chip performance         |                                  |                                         |  |  |  |  |

| No detector (C <sub>d</sub><br>ASIC#1                           | <sub>et</sub> =0pF),              | 2cm detector (Cdet=3pF), ASIC#2  |                                         |  |  |  |  |

| Voltage gain                                                    | =55 mV/fC<br>+-0.36 mV/fC         | Voltage gain                     | =54.7 mV/fC<br>+-0.64 mV/fC             |  |  |  |  |

| Time gain                                                       | =216 ns/fC<br>+-7.54 ns/fC        | Time gain                        | =198 ns/fC<br>+-8.97 ns/fC              |  |  |  |  |

| ENC <sub>thr.scan</sub>                                         | 196 e-                            | ENC <sub>thr.scan</sub>          | 240 e-                                  |  |  |  |  |

| ENC <sub>tot.scan</sub>                                         | 286 e-                            | ENC <sub>tot.scan</sub>          | 350 e-                                  |  |  |  |  |

|                                                                 | Measured static power consumption |                                  |                                         |  |  |  |  |

| CSA                                                             | 1.25 mW                           | Semi-digital back-end            | 330 μW                                  |  |  |  |  |

| Discriminator + 530 μW DAC                                      |                                   | Total (w/o digital back-<br>end) | 2.1 mW/channel                          |  |  |  |  |

| Simulated performance of the CSA core (not directly measurable) |                                   |                                  |                                         |  |  |  |  |

| Gain                                                            | 7000 V/V                          | Bandwidth                        | 1.3 MHz                                 |  |  |  |  |

| GBW                                                             | 9 GHz                             |                                  |                                         |  |  |  |  |

#### Noise:

#### (thr scan)

ENC=196+14.6\*Cdet ENC@30pF = 634 e-

#### (tot scan)

ENC=286+21.3\*Cdet ENC@30pF = 925 e-

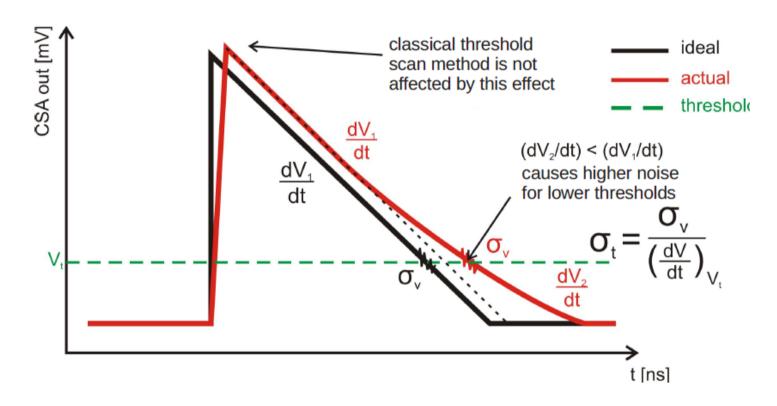

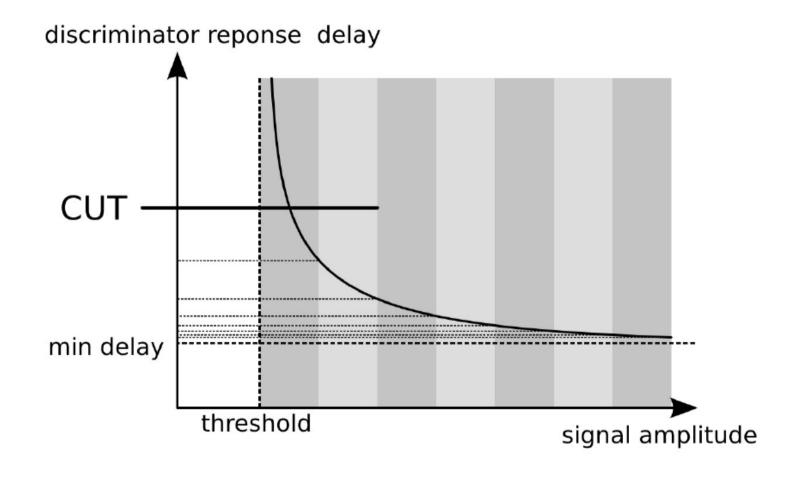

## **Timewalk**

## Timewalk dependent on:

- pulse rise time

- discriminator response time (amplitude over threshold, noise)

#### Pros & cons

#### Pros:

- infinite dynamic range

- low power consumption

- simple architecture

#### Cons:

- sensitivity to leakage currents

- pulse length dependant on signal amplitude

- wideband → noise

- timewalk (timestamp precision vs noise)

# Proposed architecture of prototype readout ASIC for CBM STS

R. Szczygiel, P. Grybos, K. Kasinski, R. Kleczek

AGH UST Cracow, Poland

## **Outline**

- 1. Requirements

- 2. Front-end architecure

- 3. Fast and slow channel

- 4. Time measurement

- 5. Amplitude measurements

- 6. Conclusions

## STS ASIC working specifications

- 128 channels

- CBMnet backend

- Linear range 1-12 fC (typical input charge = 2 fC)

- Power < 10 mW / channel</li>

- Time measurement < 10 ns resolution</li>

- Detector: DC (AC?), 30 pF total capacitance

- Dual polarity

- Recovery from overload

- Leakage current compensation

## Block diagram of a single channel

$V_{thF}$  <  $V_{ADCmin}$  -> the time measurement is validated by the energy measurement – worst cases dropped

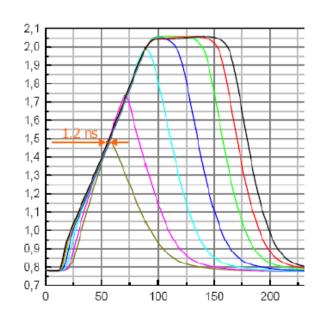

## Fast CR-RC and slow CR-(RC)<sup>2</sup> shapers

## Timing and ENC: Qin = 1-12fC, PWR =5.5mW

Tp = 38ns ENC = 1020 el

Tp = 95ns ENC = 624 el

Only simulation!!!

## Measurements – other groups (UMC180)

NSS CONFERENCE RECORD, 2010 IEEE, KNOXVILLE, USA

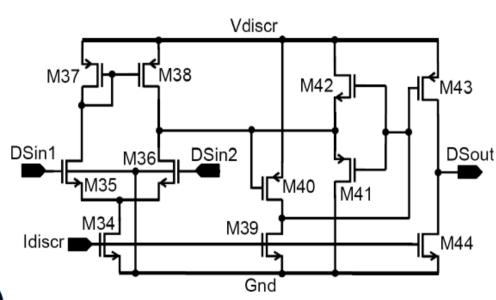

#### SPADIC - A Self-Triggered Pulse Amplification and Digitization ASIC

Tim Armbruster, Peter Fischer and Ivan Perić

Fig. 7. Preamplifier noise vs. detector capacitance

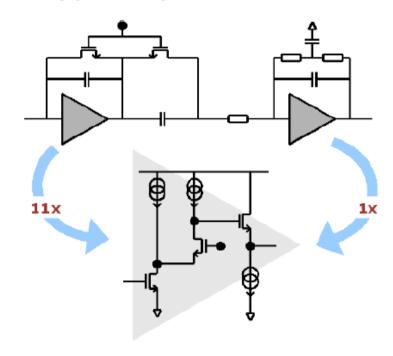

#### C. Preamplifier and Shaper

Fig. 4. Simplified preamp/shaper schematic

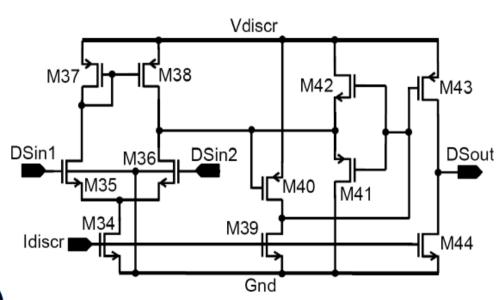

As sketched (Fig. 4) each amplifier channel basically consists of a single-ended preamplifier with NMOS input and a pole-zero cancellation feedback, a 2nd order T-feedback shaper (82 ns shaping-time) and a comparator (not shown)

## Our prototype: FSDR16 chip, tested 2011/2012

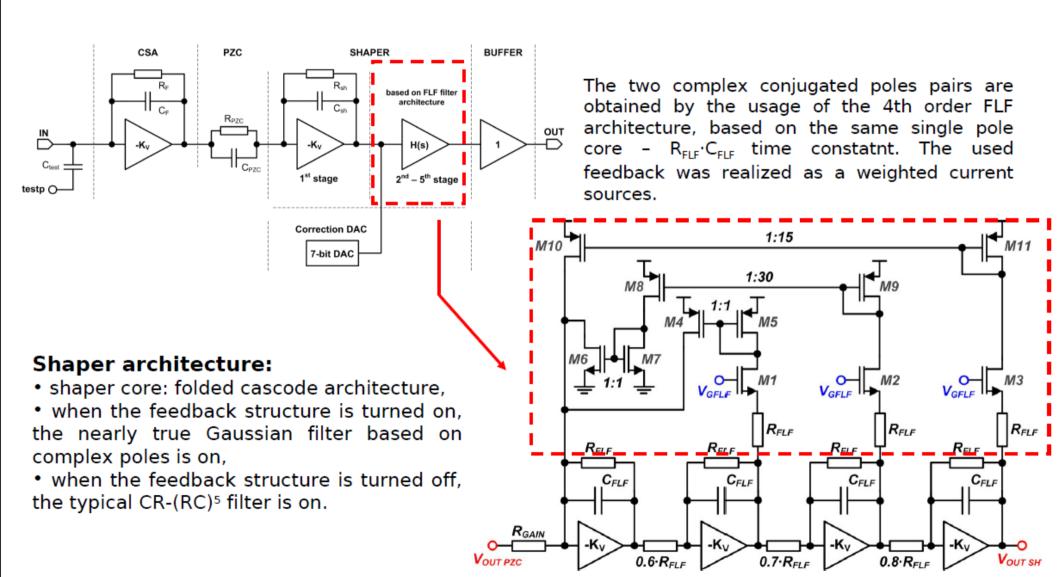

#### FSDR16 - features:

- · implemented in UMC 180nm CMOS,

- · dedicated for silicon strip detectors,

- two programmable shaper types which allow to make a comparison between typical CR-(RC)<sup>5</sup> shaper based on real poles and a nearly true Gaussian shaper based on complex poles,

- two switchable peaking time tp for each of shaper types

#### FSDR16 - block diagram:

- · contains 16 channels,

- 16 analog inputs, 16 analog outputs,

- single channel is built with an analog (CSA, PZC, shaper) and digital (shift register) part

- DC voltage shaper output spread is corrected by a 7-bit trim DAC separately in ech channel.

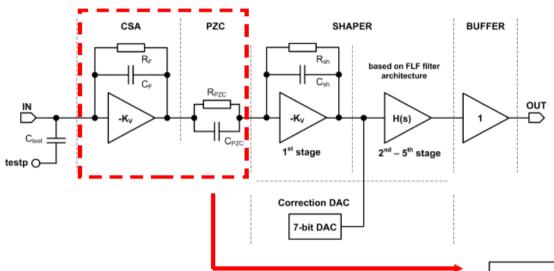

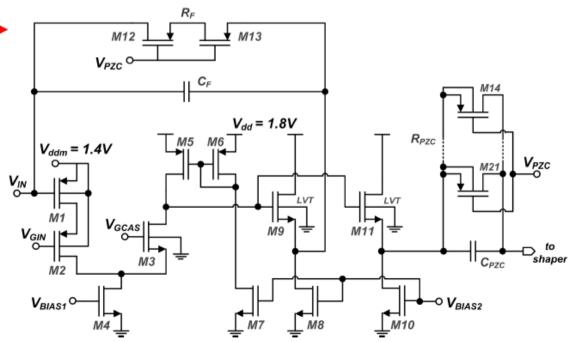

## FSDR16 - channel and CSA architectures

#### Channel architecture:

- · Charge Sensitive Amplifier,

- · Pole-Zero Cancellation circuit,

- Pulse Shaping Amplifier (two options: CR-(RC)<sup>5</sup> or based on complex poles),

- output buffer,

- 7-bit trim DAC,

- 8-bit shift register.

#### CSA and PZC architectures:

- CSA core: folded cascode architecture.

- input transistor optimized for detector capacitance  $C_{\text{DET}}$  of about 30pF,

- $R_{\mbox{\tiny F}}$  and  $R_{\mbox{\tiny PZC}}$  resistors are a MOS transistors working in linear region.

## FSDR16: shaper architecture, 5<sup>th</sup>, complex poles

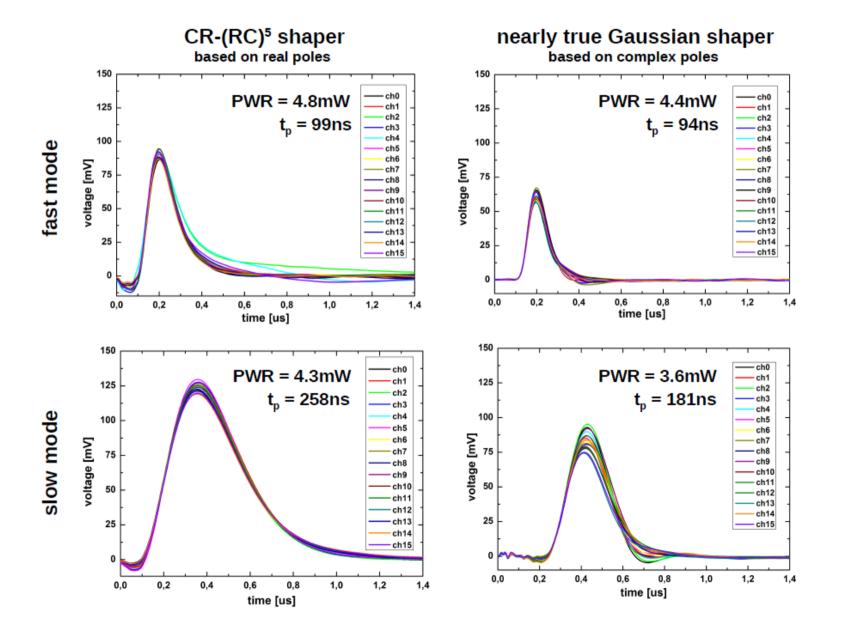

## **FSDR16** - measurements

waveforms for input charge q<sub>in</sub>=1fC without attached detector

## FSDR16 - measurements results

#### DC voltage, gain, peaking time $t_p$ , pulse width $t_w$ / peaking time $t_p$ ratio measurement results

|                           | DC voltage<br>[mV] | spread<br>[mV] | gain<br>[mV/fC] | spread<br>[mV/fC] | t <sub>p</sub> [ns] | spread [ns] | t <sub>w</sub> / t <sub>p</sub> | spread |

|---------------------------|--------------------|----------------|-----------------|-------------------|---------------------|-------------|---------------------------------|--------|

| Complex fast              | 523                | 3              | 62              | 3.4               | 94                  | 2.7         | 3.5                             | 0.6    |

| Complex slow              | 518                | 5.9            | 85              | 6.4               | 181                 | 5.8         | 2.96                            | 0.57   |

| CR-(RC)⁵ fast             | 522                | 2.1            | 91              | 2.6               | 99                  | 7.9         | 5.32                            | 0,75   |

| CR-(RC) <sup>5</sup> slow | 521                | 1.5            | 124             | 2.8               | 258                 | 5.1         | 4.6                             | 1.74   |

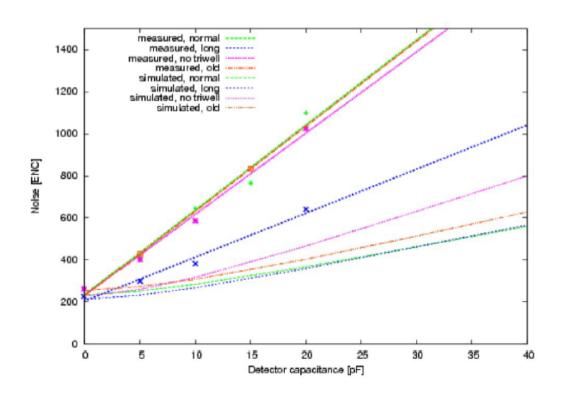

#### CR-(RC)<sup>5</sup> shaper:

fast mode: ENC = 214el + 13.3el/pF  $\cdot$  C<sub>DET</sub>

slow mode: ENC = 153el + 12el/pF  $\cdot$  C<sub>DET</sub>

#### Nearly true Gaussian shaper

**fast mode**: ENC = 246el + 23.7el/pF  $\cdot$  C<sub>DET</sub>

slow mode: ENC =  $176el + 16.7el/pF \cdot C_{DET}$

#### **ENC - measurements**

|                           | ENC<br>[e <sup>-</sup> ] | spread<br>[e <sup>-</sup> ] | ENC at<br>C <sub>DET</sub> =3pF<br>[e <sup>-</sup> ] | spread<br>[e <sup>-</sup> ] | ENC at<br>C <sub>DET</sub> =30pF<br>[e <sup>-</sup> ] |

|---------------------------|--------------------------|-----------------------------|------------------------------------------------------|-----------------------------|-------------------------------------------------------|

| Complex fast              | 246                      | 6.9                         | 317                                                  | 14.4                        | 956                                                   |

| Complex slow              | 176                      | 11.3                        | 226                                                  | 11.2                        | 676                                                   |

| CR-(RC)⁵ fast             | 214                      | 5.3                         | 254                                                  | 5.3                         | 614                                                   |

| CR-(RC) <sup>5</sup> slow | 153                      | 3.4                         | 189                                                  | 2.5                         | 513                                                   |

# **ENC** - estimation

## **Shaper is very complex!**

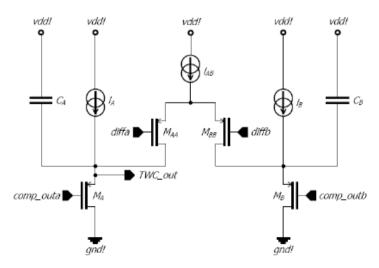

## Time measurement : option 1

Fast shaping time and later validation using ADC value

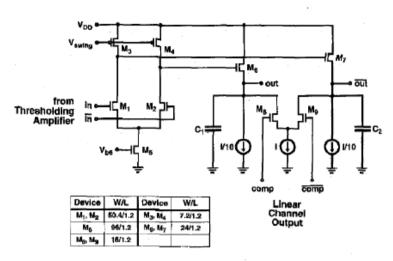

## Time walk compensation – option 2

Fig. 12. Time walk compensation circuit.  $I_{\rm DS}(M_{\rm S})=70~\mu{\rm A},~I=100~\mu{\rm A},~C_1=C_2=0.1~{\rm pF}.$

## A CMOS Multichannel IC for Pulse Timing Measurements with 1-mV Sensitivity

Marc J. Loinaz, Student Member, IEEE, and Bruce A. Wooley, Fellow, IEEE

PhD - T. Fiutowski

## Energy measurements: 5-bit flash ADC

## Small discriminator

## Option 1: discriminator with trimming

Area:  $20 \times 50 \text{ um}^2$ ( $40 \times 50 \text{ um}^2 \text{ with register}$ )

PWR: 10 – 20 uW

Option 2: discriminator with automatic offset cancellation

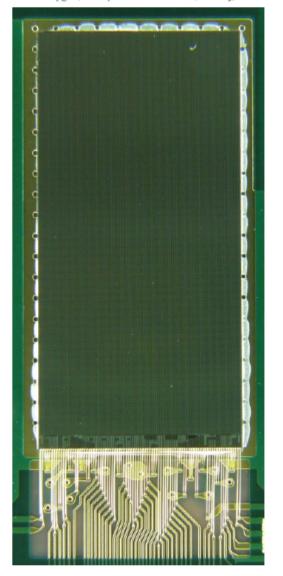

# Triming DAC is necessary – see PXD18k chip (UMC180nm)

PXD18k – Fast Single Photon Counting Chip with Energy Window for Hybrid Pixel Detector

R. Szczygiel, P. Grybos Member IEEE, P. Maj, M. Zoladz

#### Results:

before correction: sd = 15 mV

- 7-bit trim: sd = 0.76 mV

- 6-bit trim: sd = 1.19 mV

**Trimming procedure: 40s**

## Conclusions

- Separated channels for time and amplitude measurements independent optimization for timestamp precision and noise

- Expected better noise than ToT

- Expected better timing precision than ToT

- Needs more power than ToT

- Possible time measurement correction using ADC value

- Most components of well known architecture (CSA, shapers, discriminators, trimming DACs)

Deadline: July 2012

## Requirements

- some parameters depend each other:

- hit rate → dead time, data link, buffer

- digitization resolution → point resolution, PID

- time resolution → event building

- power consumption → cooling

- supply → cabling effort

# Requirements

- radiation hardness, SEU mitigation

- → technology

- detector capacitance → noise

- shaping time → noise, dead time

- linearity → energy resolution

- dimension, pad layout → stave layout

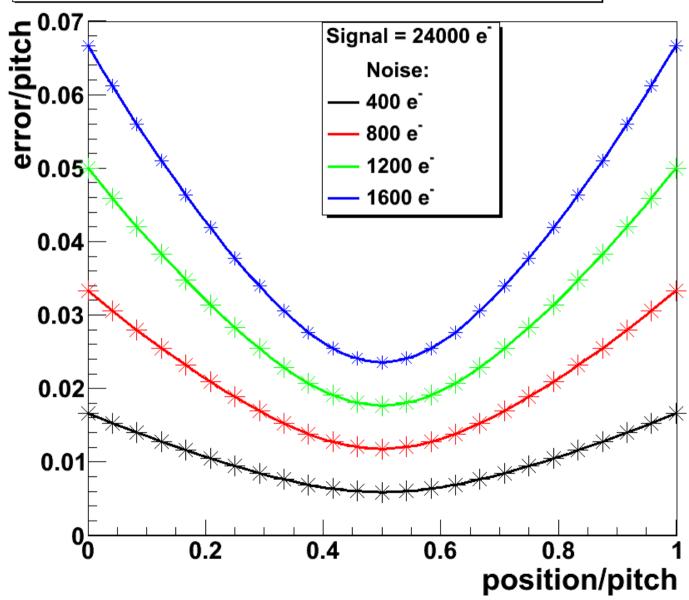

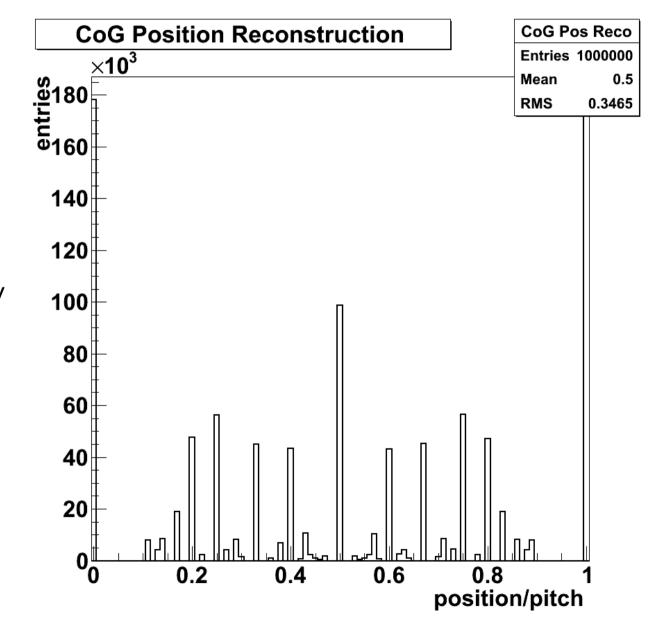

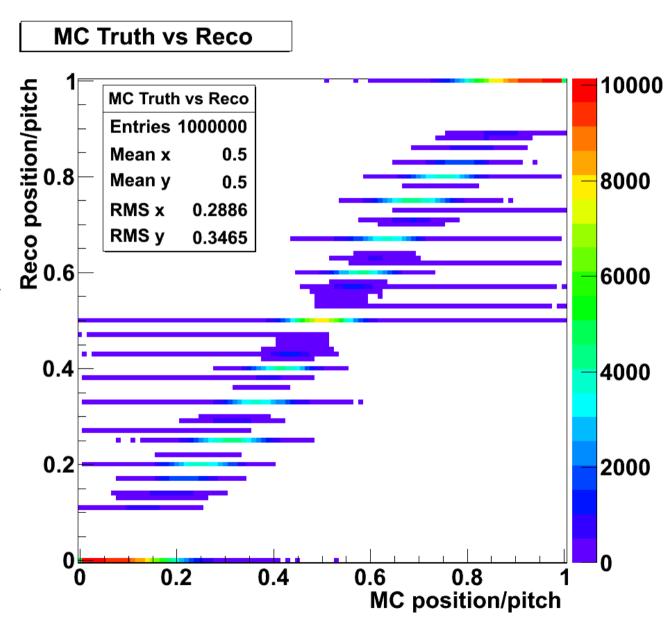

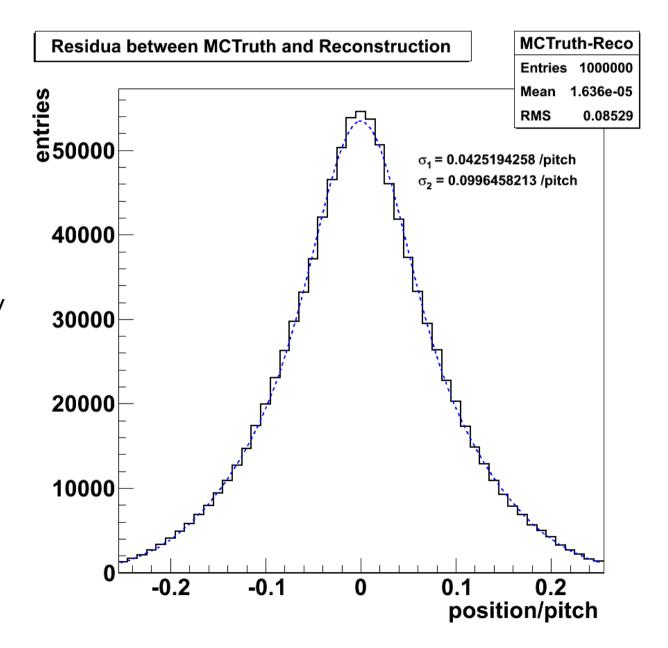

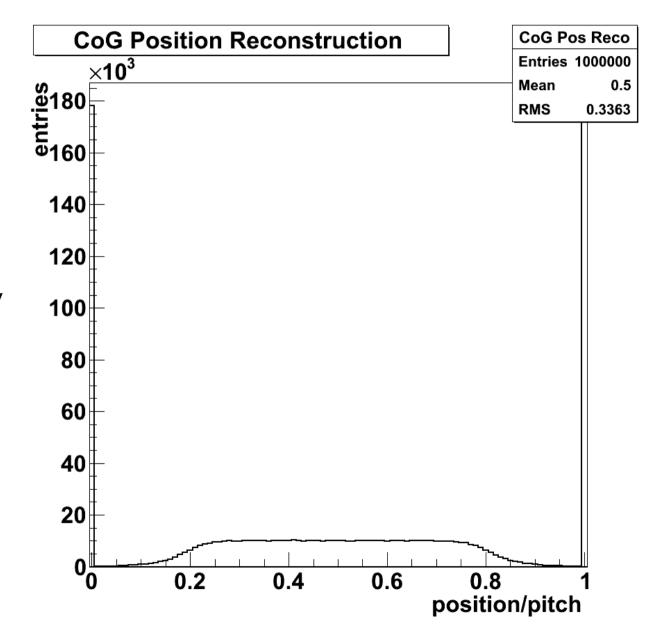

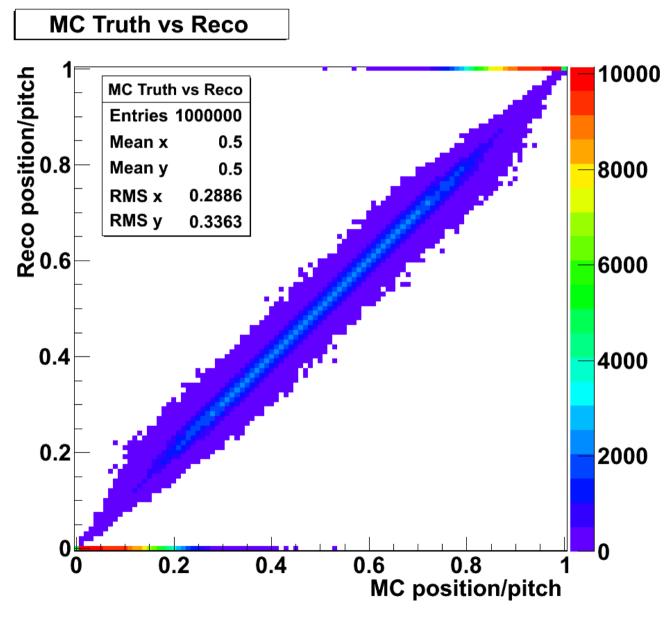

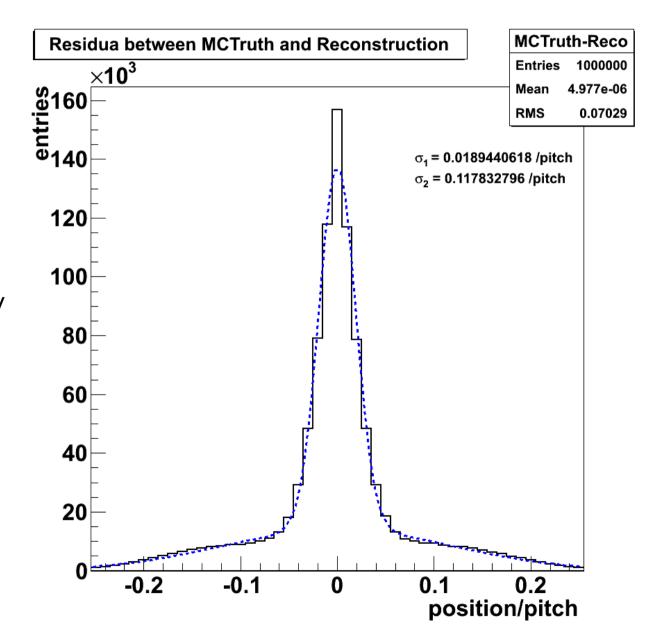

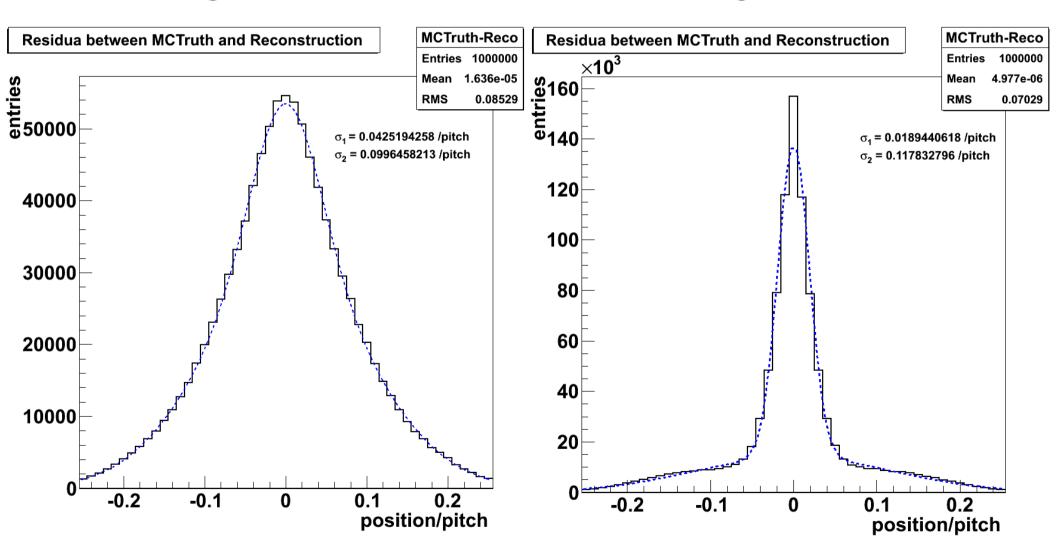

# Digitization Resolution

- important parameter for:

- spatial resolution through clustering

- PID through energy loss measurement

- → spatial resolution limited by noise (as shown below)

#### Center of Gravity Error - gaussian error, 2 strips

XL PANDA Meeting, MVD Subgroup Meeting - March 05, 2012

# Digitization Resolution

- central question:

- How many bits of digitization resolution required?

- contributes to amount of data

- provoke more power consumption

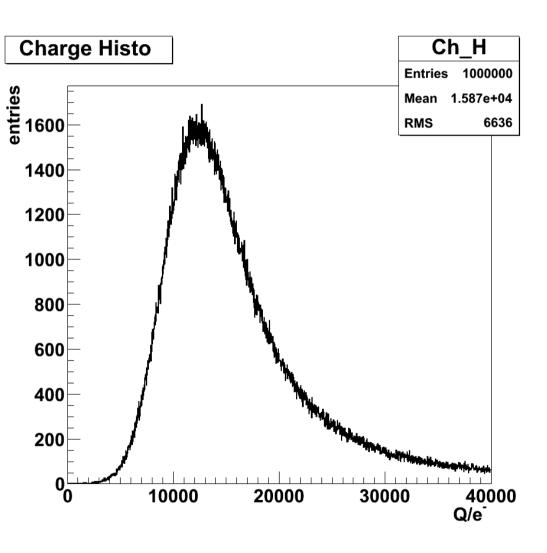

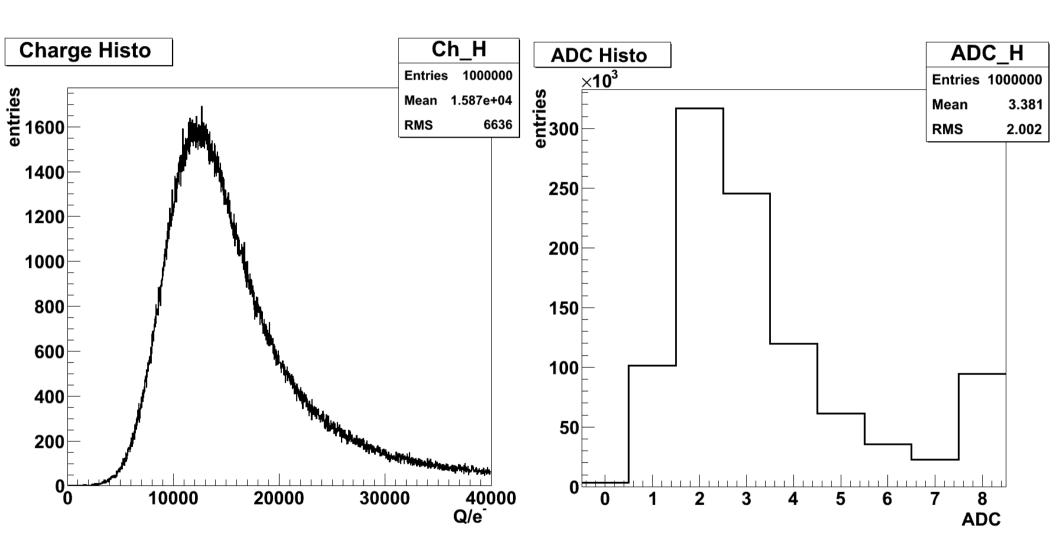

Example: FSSR2 digitization centered around 1 MIP

(2005 IEEE Nuclear Science Symposium Conference Record)

XL PANDA Meeting, MVD Subgroup Meeting - March 05, 2012

XL PANDA Meeting, MVD Subgroup Meeting - March 05, 2012

- 2 strip hit

- FSSR2 digi 3 bit

- hit threshold =  $5.000 e^{-1}$

- landau distributed signal

- $signal = 24.000 e^{-}$

- noise sigma =  $800 e^{-1}$

- clustering: Center of Gravity

- 2 strip hit

- FSSR2 digi 3 bit

- hit threshold =  $5.000 e^{-}$

- landau distributed signal

- $signal = 24.000 e^{-}$

- noise sigma =  $800 e^{-1}$

- clustering: Center of Gravity

- 2 strip hit

- FSSR2 digi 3 bit

- hit threshold =  $5.000 e^{-1}$

- landau distributed signal

- $signal = 24.000 e^{-}$

- noise sigma =  $800 e^{-1}$

- clustering: Center of Gravity

- 2 strip hit

- "analog" front-end

- hit threshold =  $5.000 e^{-1}$

- landau distributed signal

- $signal = 24.000 e^{-}$

- noise sigma =  $800 e^{-1}$

- clustering: Center of Gravity

- 2 strip hit

- "analog" front-end

- hit threshold =  $5.000 e^{-}$

- landau distributed signal

- $signal = 24.000 e^{-}$

- noise sigma =  $800 e^{-1}$

- clustering: Center of Gravity

- 2 strip hit

- "analog" front-end

- hit threshold =  $5.000 e^{-1}$

- landau distributed signal

- $signal = 24.000 e^{-}$

- noise sigma =  $800 e^{-1}$

- clustering: Center of Gravity

## 3-bit digital front-end

## analog front-end

XL PANDA Meeting, MVD Subgroup Meeting - March 05, 2012