## PANDA Collaboration Meeting

### Pixel readout status report

### *G.Mazza* on behalf of the MVD Torino group

Gianni Mazza

## **Pixel specs**

| Pixel size               | $100 	imes 100 \ \mu m^2$               |

|--------------------------|-----------------------------------------|

| Chip active area         | 11.4 × 11.6 mm² (116 rows, 110<br>cols) |

| <i>dE/dx measurement</i> | ToT, 12 bits dynamic range              |

| Max input charge         | 50 fC                                   |

| Noise floor              | <32 aC (200 e <sup>-</sup> )            |

| Clock frequency          | 155.52 MHz                              |

| Time resolution          | 6.45 ns ( 1.9 ns r.m.s. )               |

| Power consumption        | $< 750 \text{ mW/cm}^2$                 |

| Max event rate           | $6 \cdot 10^6$                          |

| Total ionizing dose      | < 100 kGy                               |

Gianni Mazza

PANDA Meeting at GSI, December 13th 2011

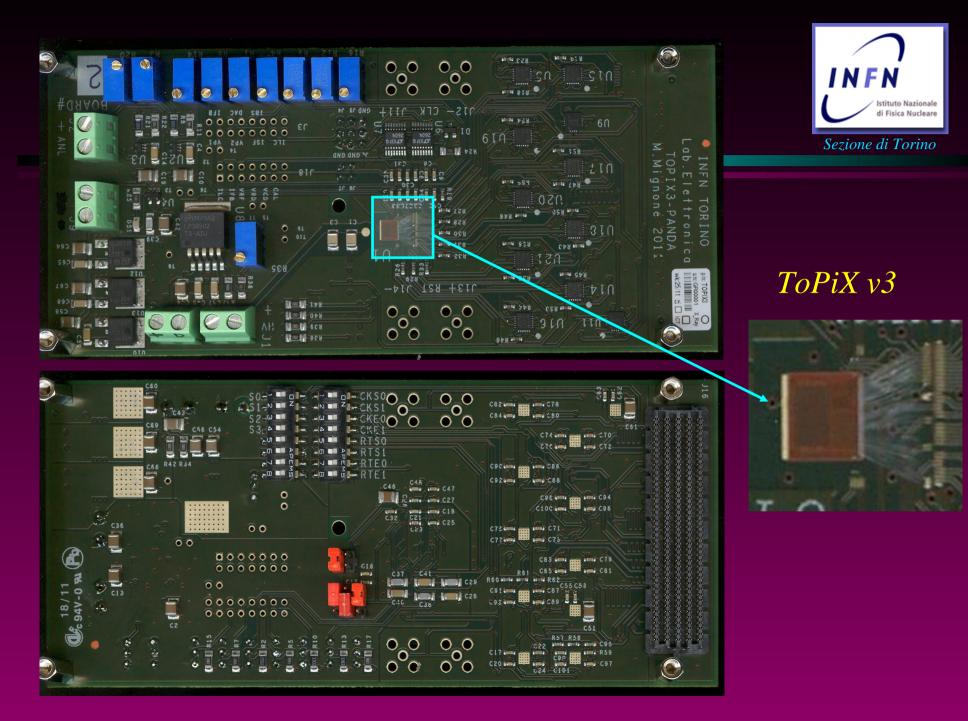

### ToPiX v3

- Layout submitted on February 7<sup>th</sup> received May 16<sup>th</sup>

- $4.5 \text{x4} \text{ mm}^2$  die area

- CMOS 0.13 μm DM technology

- Triple redundancy-based SEU protection

- End of column logic

- 160 Mb/s SLVS serial output

- Pads for bump bonding

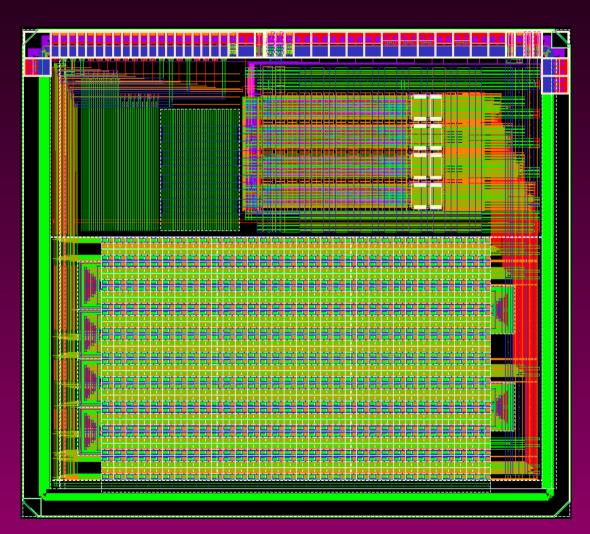

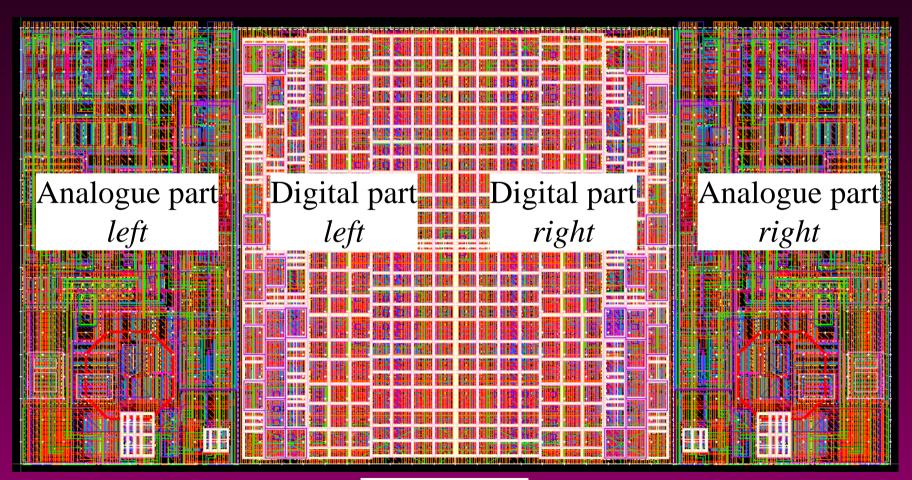

# ToPiX v3 layout

- \* 4.5 mm × 4 mm

- \* CMOS 130 nm

- \* Clock frequency 160 MHz

- bump bonding pads

- \*  $2 \times 2 \times 128$  columns

- \*  $2 \times 2 \times 32$  columns

- \* 32 cells EoC FIFO

- \* SEU protected EoC

- \* Serial data output

- \* SLVS I/O

PANDA Meeting at GSI, December 13th 2011

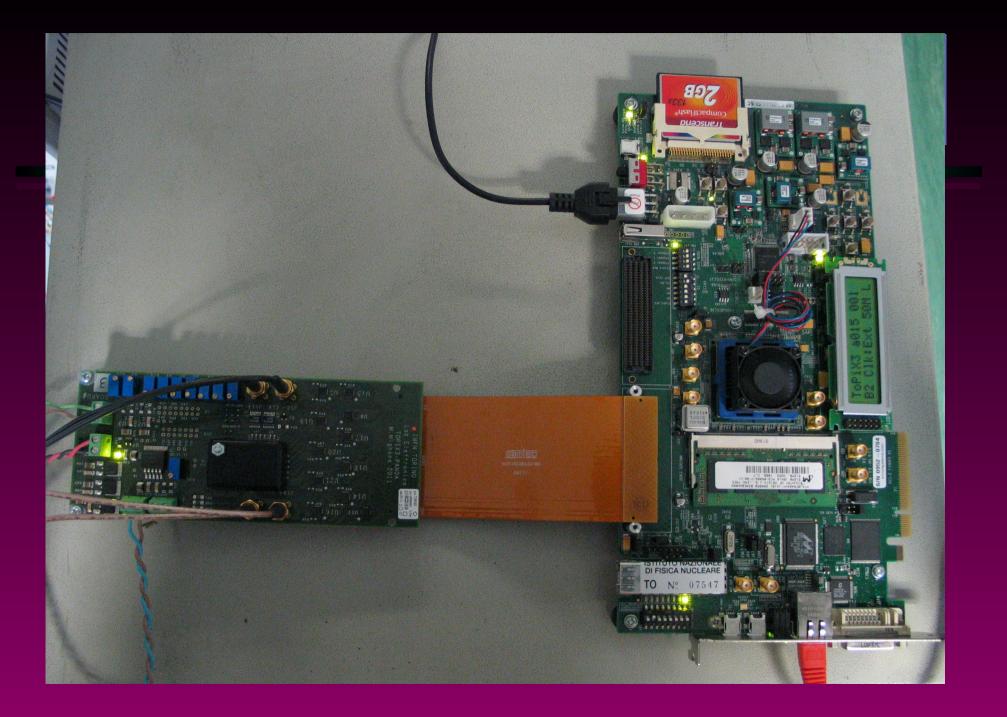

# ToPiX v3 test status

- \* At 160MHz can only read and program first ~32 pixels of each column

- \* At 50MHz (with pre-emphasis disabled) full operation

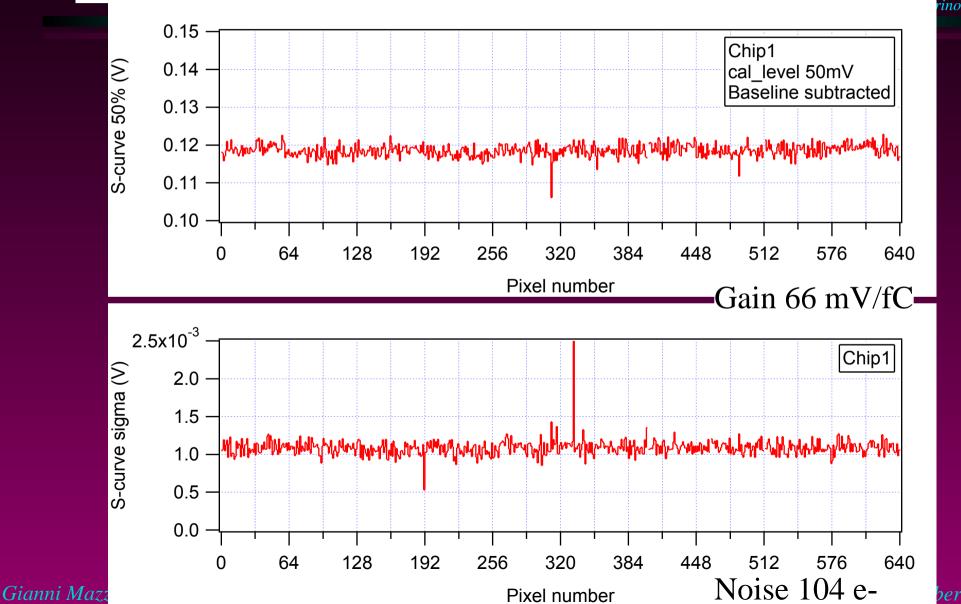

- \* S-curve working well (programmable internal test pulse)

- Baseline measurements ok

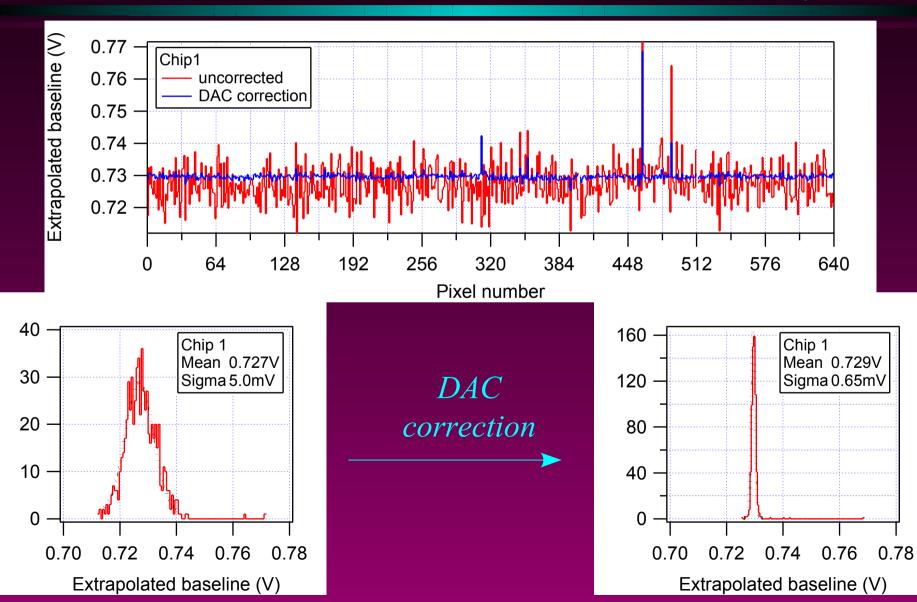

- \* On-pixel DACs characterised and correction applied

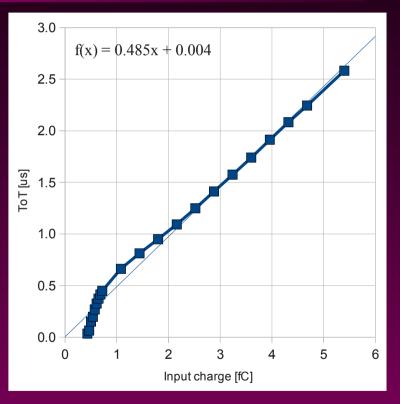

- \* Transfer function measurements in good agreement with simulations

- \* Acquisition system is working (4 boards)

- Test beam results under analysis

Gianni Mazza

#### PANDA Meeting at GSI, December 13<sup>th</sup> 2011

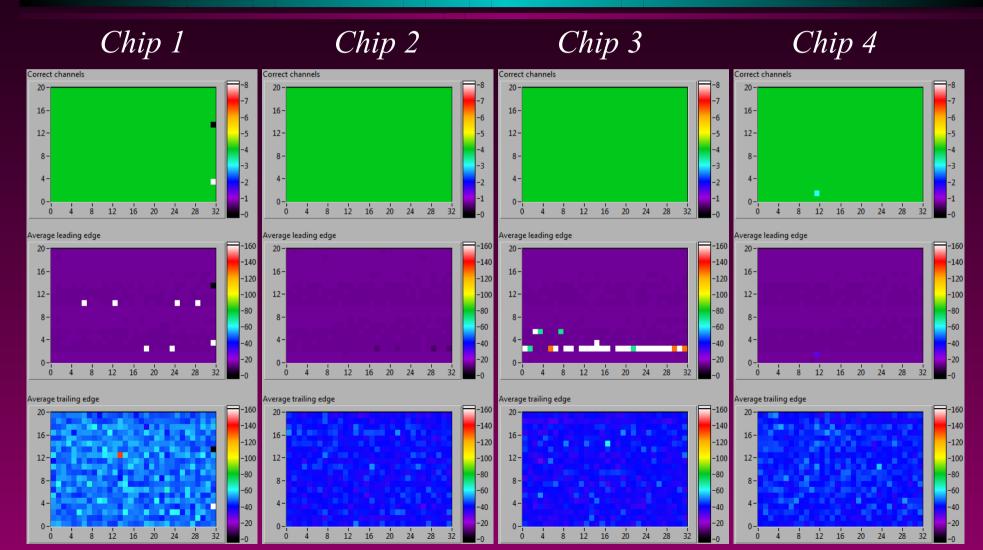

## Functional tests @ 50 MHz

Gianni Mazza

Gianr

### **Baseline correction**

2011

Gain & Noise

ber 13<sup>th</sup> 2011

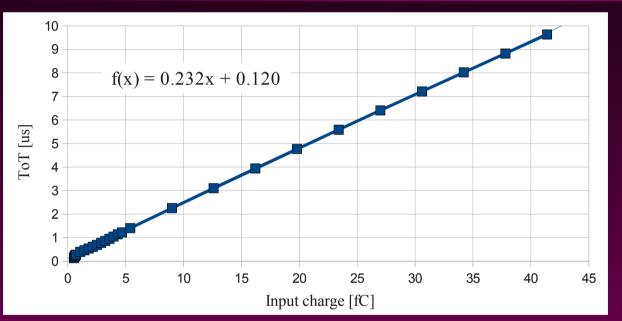

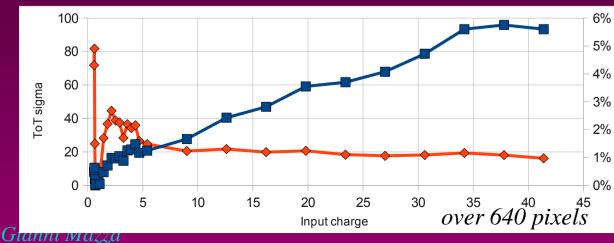

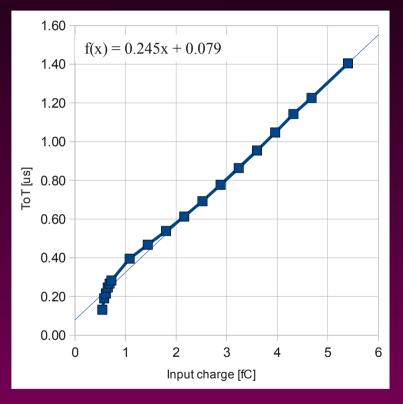

# ToT @ 5 nA

$I_{FB} = 5 nA$ Simulated gain : 202 ns/fC PANDA Meeting at GSI, December 13<sup>th</sup> 2011

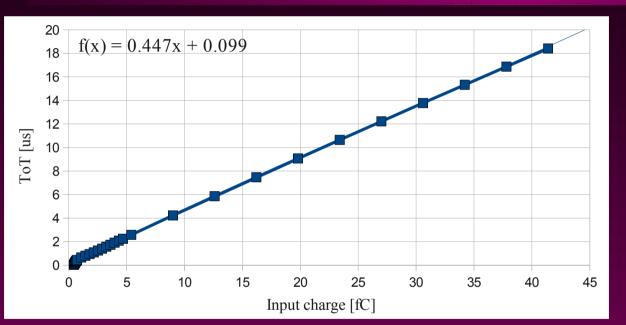

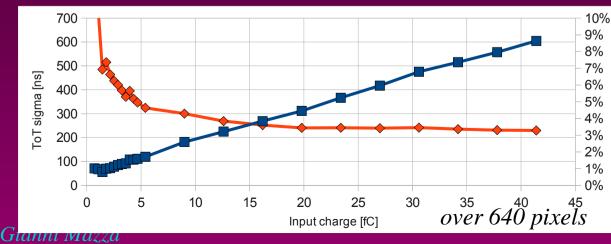

# ToT @ 2.5 nA

I<sub>FB</sub> = 2.5 nA Simulated gain : 400 ns/fC PANDA Meeting at GSI, December 13<sup>th</sup> 2011

## Clock frequency problem

- \* At 160 MHz only the first 32 pixels of the 128 cells columns work correctly

- \* Response improves when the frequency is decreased

- \* "Easy" corrections :

- \* Prototype full column has 30% longer bus and 10% more cells than the final chip

- \* Triple redundancy latches have been connected without buffers

- Bus estimated capacitance : 47.35 fF/cell (55% due to the cell, 45% due to interconnection capacitance)

- \* Total bus capacitance per line : 6.88 pF (now), 3.48 pF (est.)

Gianni Mazza

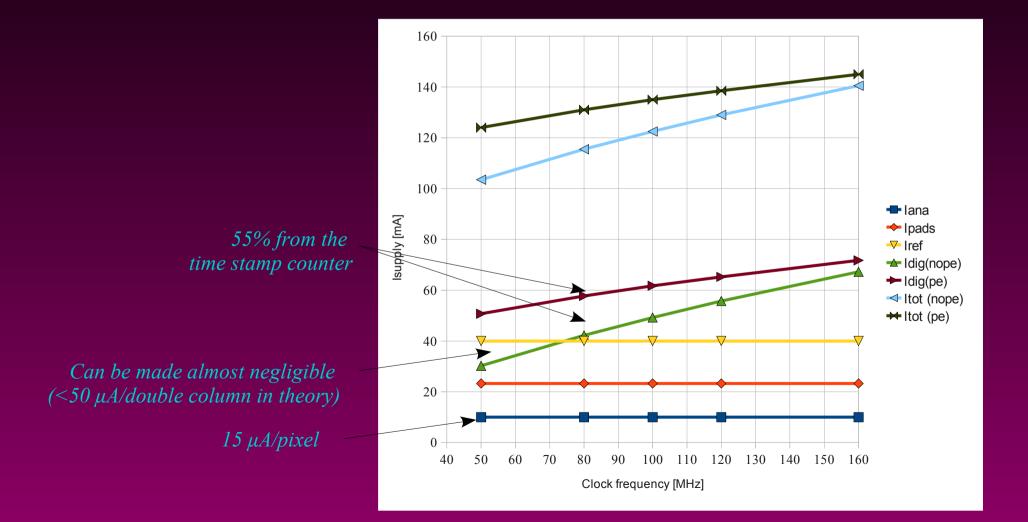

# **Power supply**

PANDA Meeting at GSI, December 13th 2011

Gianni Mazza

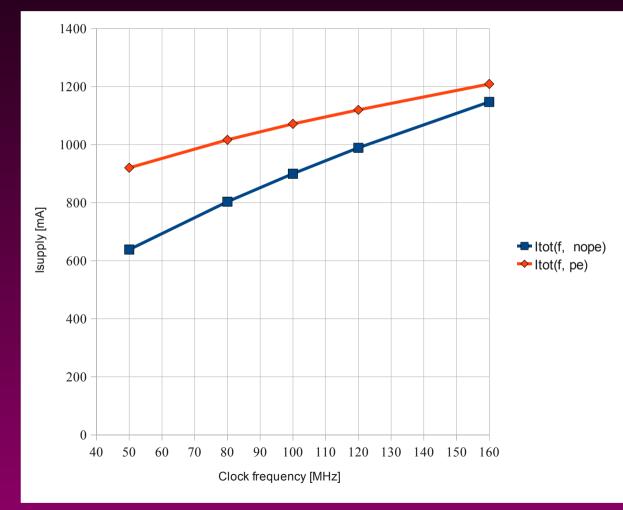

# Full chip estimate

- Very rough estimate

- Still room for improvements(ToPiX v3 not really designed having low power in mind...)

- However, power consumption seems to be an issue

- Do we really need 1.9 ns time resolution ?

# ToPiX v3.1

- Activity on the new ToPiX version started main target is power reduction. Still margin for improvements - *ToPiX v3 was definitely not designed for low power...*

- Custom standard cell library from MediPix collaboration has been analyzed – modifications started to be compatible with the ToPiX requirements.

- \* Time stamp bus re-design is required. Targets are capacitance and voltage swing reduction

- Review of the time resolution requirement is suggested speed does not come for free...

## **New library**

- \* Developed at CERN by the MediPix group

- \* Cells height : 2.4  $\mu$ m (IBM library : 4.8  $\mu$ m )

- \* N. of cells : 43 (IBM library : 361)

- \* Based on low power transistors for low leakage

- \* Characterization with the Cadence Encounter Library Characterization (ELC) tool

- \* Requirements for PANDA :

- move to normal transistors

- add more cells

PANDA Meeting at GSI, December 13<sup>th</sup> 2011

### Conclusions

- \* Electrical tests of the ToPiX v3 almost completed chip is functionally ok, but a time stamp distribution problem limits the maximum speed

- \* Irradiation tests performed, results under analysis

- \* Beam test performed, results under analysis

- Preliminary work for the new ToPiX prototype has started the target is to reduce the on-pixel digital part size and the time stamp bus capacitance

- Power consumption is an issue. The time stamp distribution is a dominant contribution

## Backup slides

Gianni Mazza

PANDA Meeting at GSI, December 13th 2011

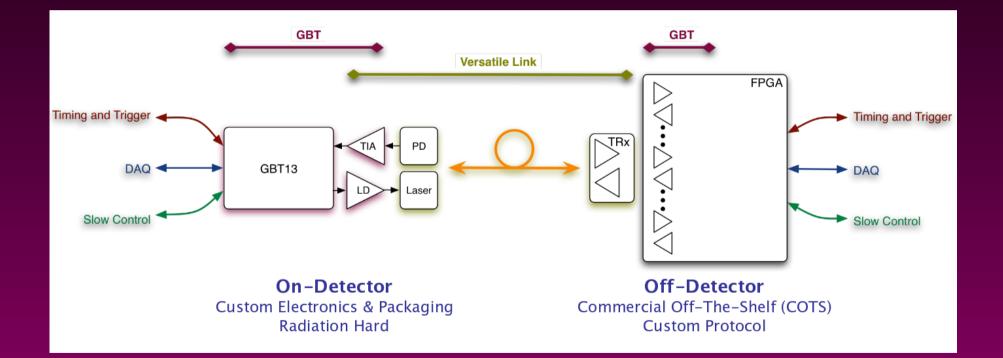

## **GBT** chipset

### Radiation tolerant chipset :

- \* GBTIA : Transimpedance optical receiver

- \* GBLD : Laser driver

- \* GBTx : Data and Timing Transceiver

- \* GBT-SCA : Slow control ASIC

### Supports :

- Bidirectional data transmission

- \* Bandwidth :

- $\rightarrow$  Line rate : 4.8 Gb/s

- $\rightarrow$  Effective : 3.36 Gb/s

#### Gianni Mazza

### Target Applications :

- \* Data readout

- \* TTC

- \* Slow control and monitoring links

### Radiation Tolerance :

- \* Total dose

- Single Event Upset

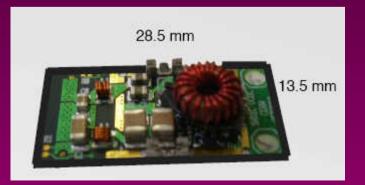

# **Power regulator**

\* ToPiX power supply 1.2 V –  $I_{DC} \sim 1$  A ( estimated )

$\rightarrow$  voltage drop on cables is not negligible

- A DC-DC converter solution compatible with the radiation levels and the magnetic field of a silicon tracker is under development

@ CERN for sLHC

- \* Current CERN version :  $V_{IN} 10 \div 12 \text{ V}, V_{OUT} = 1.8 \div 3.3 \text{ V}, I_{OUT} < 3 \text{ A}$

- \*  $V_{OUT} = 1.5 \text{ V}, I_{OUT} < 3-4 \text{ A now avail.}$

- \* Board position t.b.d.

$\rightarrow$  ToPiX internal regulator t.b.d.

PANDA Meeting at GSI, December 13<sup>th</sup> 2011

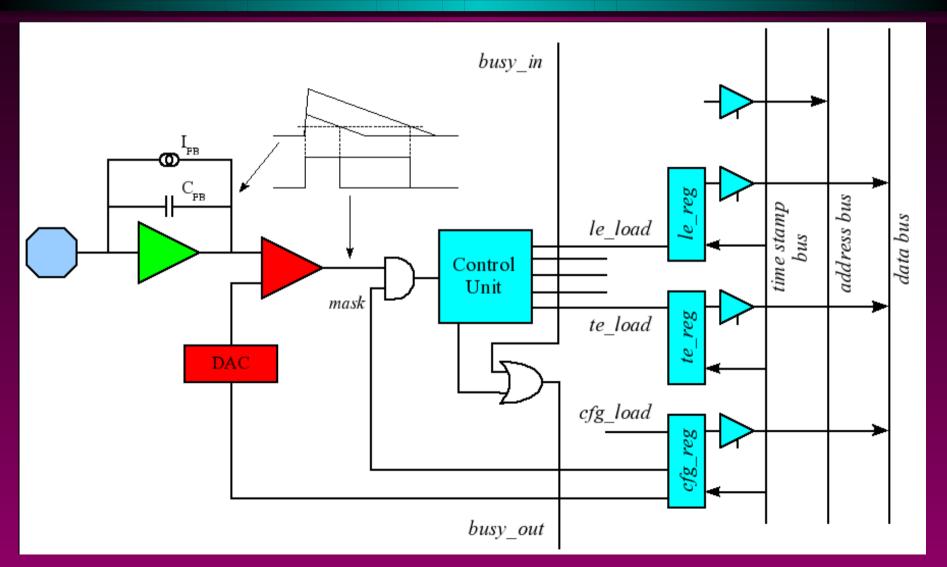

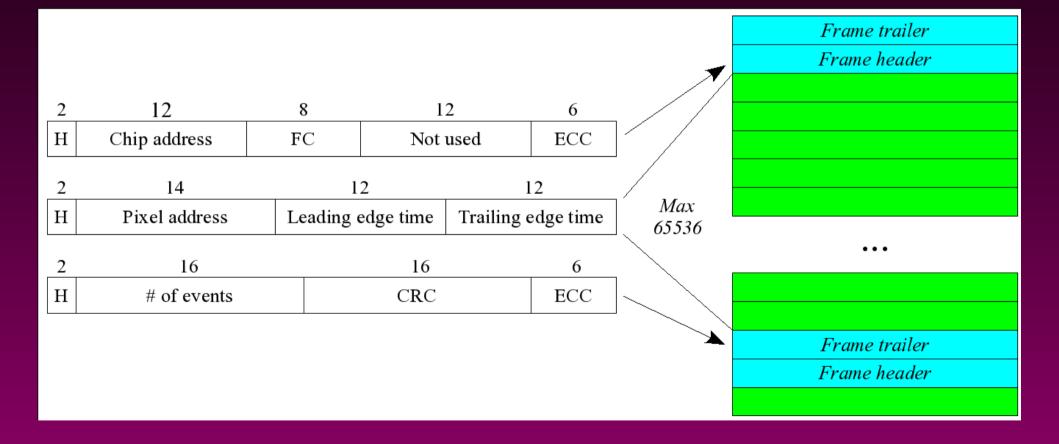

## **ToPiX ASIC**

- \* Custom development for the PANDA MVD

- Provides spatial and time coordinates plus energy resolution measurement (via ToT)

- \* Compatible either with p-type or n-type detectors

- \* Self triggered architecture

- \* Each event has a 12 bits time reference

- Double rate serial readout

- Radiation tolerant

- Data corresponding to a 12 bits counter cycle (26.21 μs) are packed in a frame, with an 8 bits frame counter (6.71 ms cycle)

Gianni Mazza

### **Pixel cell**

PANDA Meeting at GSI, December 13th 2011

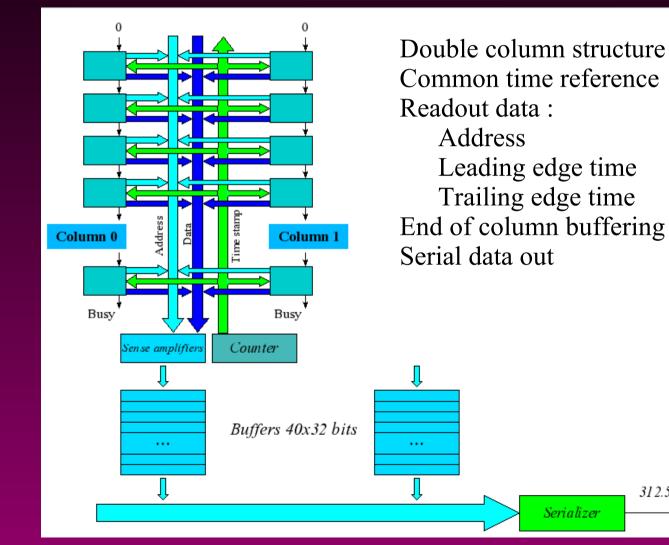

## **Double cell**

Common bus

#### Gianni Mazza

#### PANDA Meeting at GSI, December 13th 2011

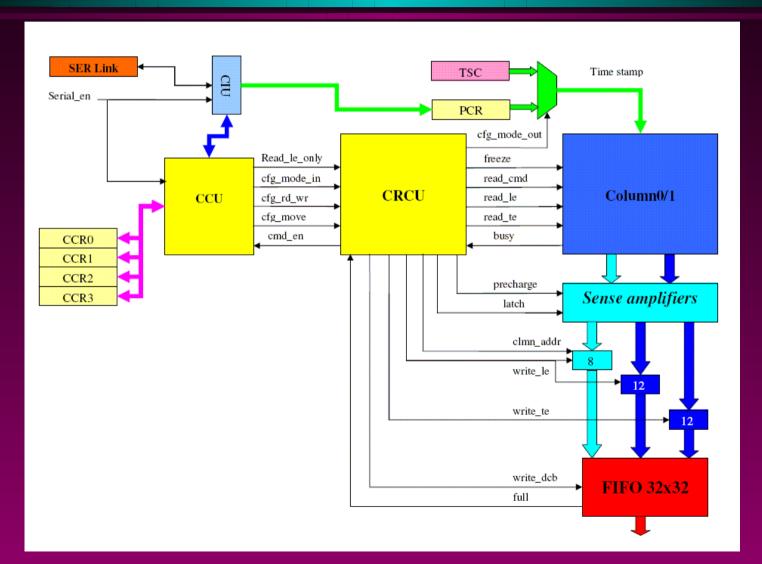

## **ToPiX block diagram**

Gianni Mazza

PANDA Meeting at GSI, December 13<sup>th</sup> 2011

312.5 Mb/s

## **End of column**

### **Data format**

#### Gianni Mazza

#### PANDA Meeting at GSI, December 13th 2011

Gianni Mazza

PANDA Meeting at GSI, December 13th 2011