### The EDD Frontend Electronics Update

Simon Bodenschatz, Lisa Brück, Michael Düren, Avetik Hayrapetyan, Jan Hofmann,

Sophie Kegel, İlknur Köseoğlu-Sari, Jhonatan Pereira de Lira, Mustafa Schmidt, Marc

Strickert, Leonard Welde, Chris Takatsch

PANDA Collaboration Meeting 21/2 - 2021/06/15

JUSTUS-LIEBIG-

History of the EDD -FEE

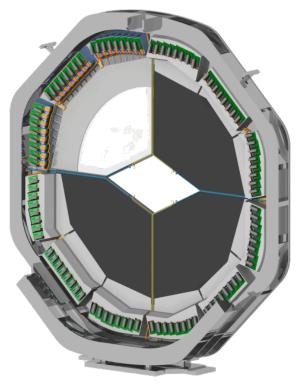

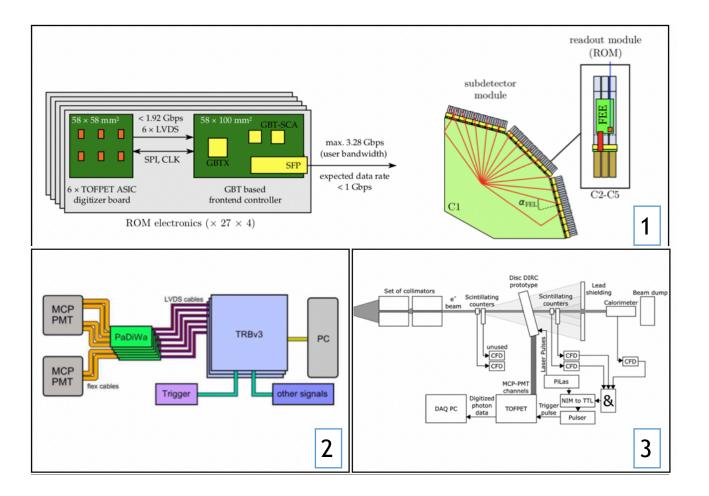

- The readout system was used in 2015 testbeam at CERN (2). TRBv3 boards with PadiWA

- First time it is suggested to use TOFPET system (1).

- First TOFPET system was used in 2016 testbed at DESY (3).

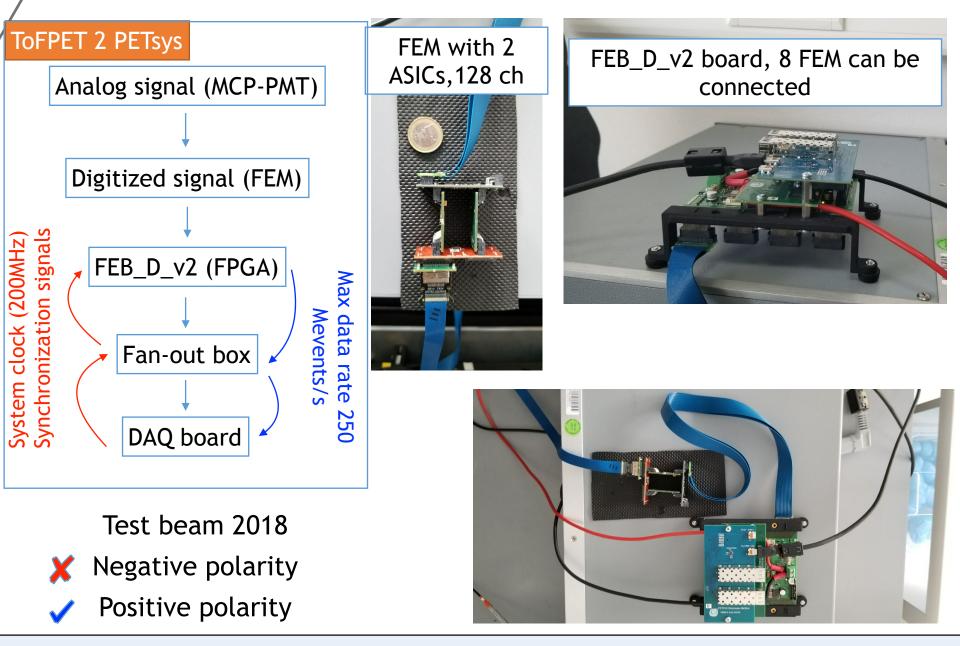

- TOFPET2 was used during testbeam 2018.

The production batch of 2018

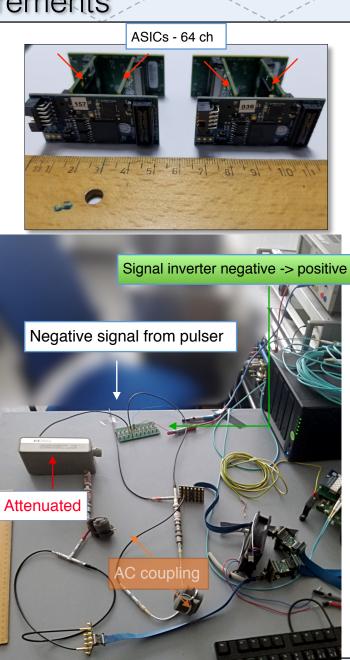

# The 2020 batch of ASICs - test measurements

- Positive Signal ~ 40mV

- Negative Signal  $\sim 40 mV$ , pW 3.5ns

- Compatible to work with both polarities

- Convincing results from GCS data analysis

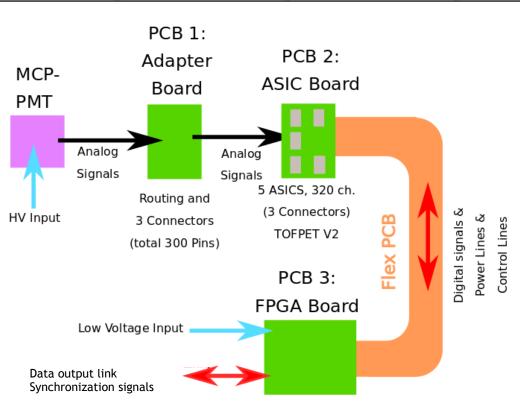

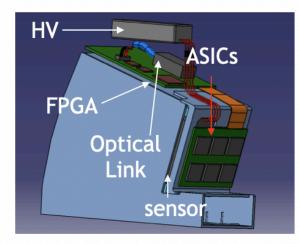

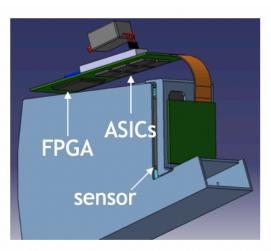

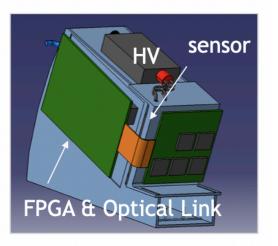

# Design for Prototype & Phase 1

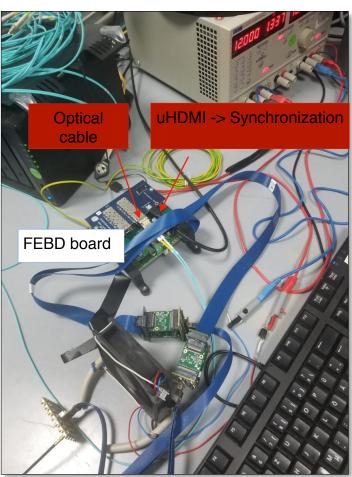

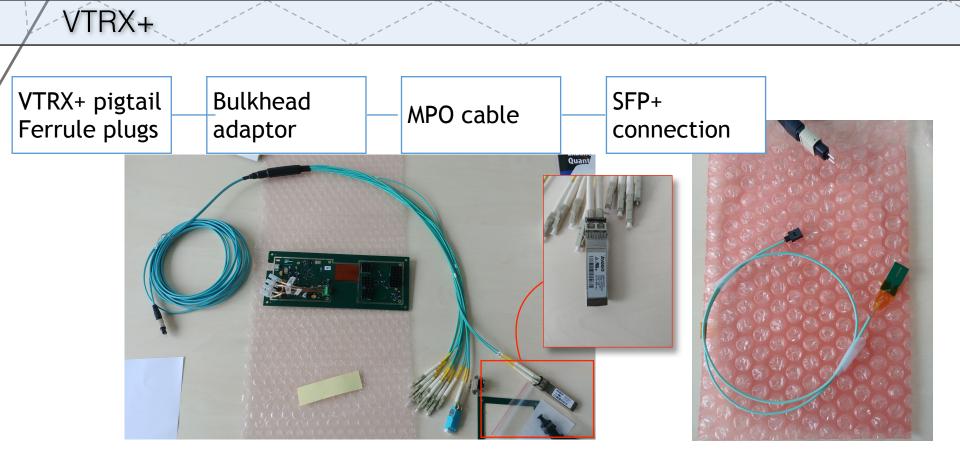

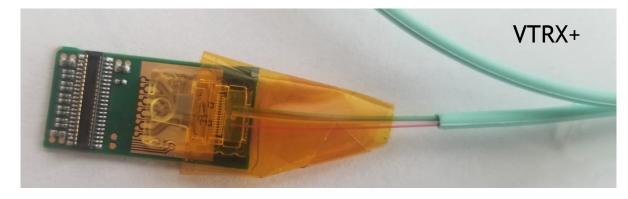

- Optical link -> VTRX+ link (radiation hard and magnetic field resistant)

- DC-DC converters -> FEASTMP modules

- uHDMI cable -> synchronization purposes

## **Different Scenarios**

- 6 ASICs

- ASICs are at the shortest distance to the analog signals.

- The elements are distributed considering the heat generation.

- 6 ASICs

- ASICs and FPGA are positioned on the same rigid board.

- Disadvantage: analog signals had to reach the second board for digitization.

- Disadvantage: Heat generation in a compact area.

- 5 ASICs

- Similar as in scenario-1.

- Due to the limited space in z-direction, alignment can be done to the side of the ROM.

- Disadvantage: 6 ROMs/ side.

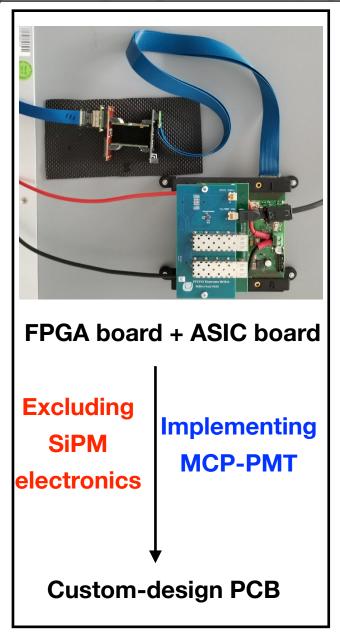

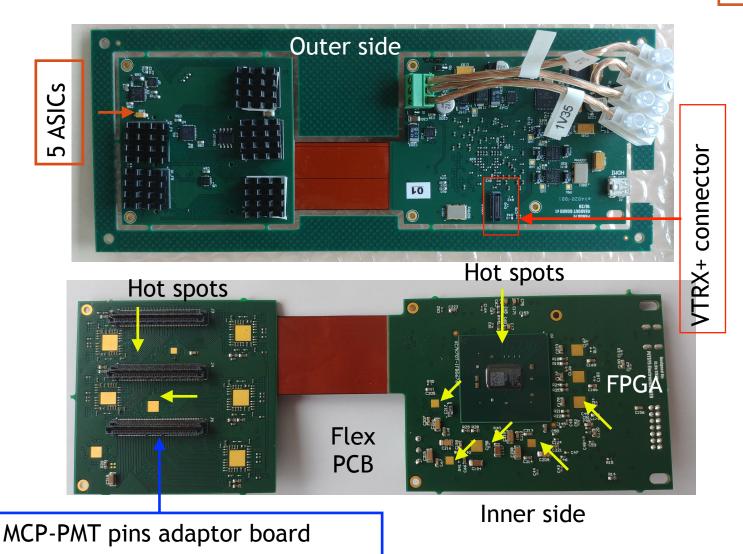

### Custom-design PCB

- The custom-design PCB has been delivered 2 weeks ago.

- Several tests were planned.

### FEASTMP modules

In order to test custom PCB, second DAQ board and fan-out-box (synchronization) are required. The current system is reserved for the GCS.

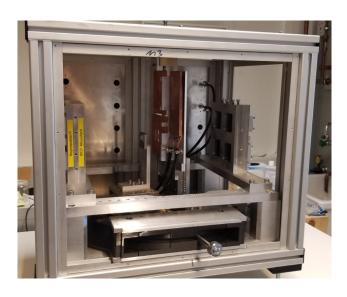

- 1. Testing the custom PCB with MCP-PMT, inside the magnet box without magnets. The laser will be focused on each pixel.

- MCP-PMT will be provided by Erlangen group.

- Magnetic field was measured for different distances, see Leonard's talk.

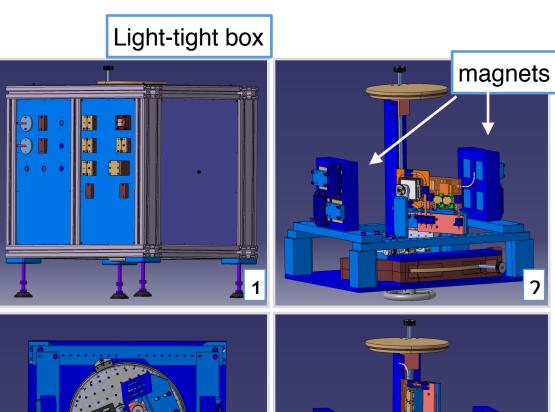

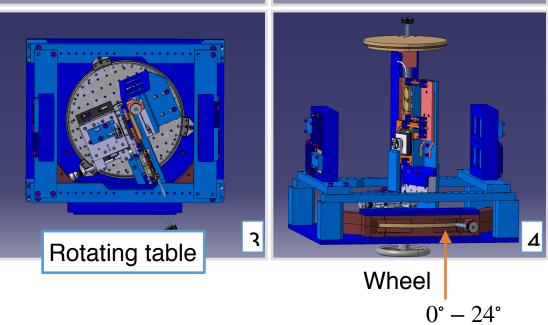

- 2. Same tests will be repeated with magnets. Magnet box allows changing the angle of the MCP-PMT with respect to the magnetic field.

- 3. Custom-design PCB together with MCP-PMT will be integrated into GCS. This requires a different cooling system -> Lisa's talk.

### Magnet Box design

- The light-tightness was tested. It is not perfectly light-tight still some photons enter the box.

- Dark count measurements are ongoing with Hamamatsu.

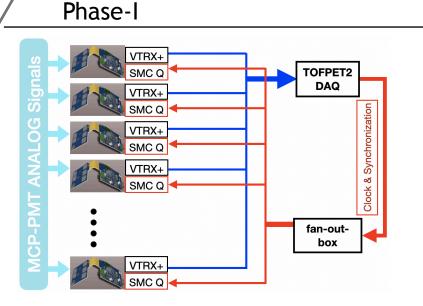

## Project phases

- 16 ROMs are planned to be used.

- Existing DAQ system (TOFPET2 DAQ) will be used for data taking, clock & synchronization

- Optical link (VTRX+)-> data transmission.

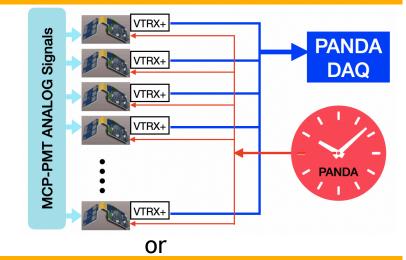

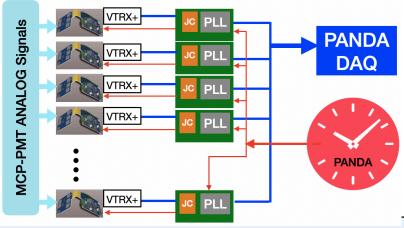

#### Phase-II

#### Scenario-1: All control signals are received via optical cable

Scenario-2: If Clock & Synchronization signals are transmitted as hardware signals

- Reformatting outgoing data into the SODANET format

- Receive SODANET clock & synchronization commands

- TOFPET-2016 was compatible to work with both signal polarities.

- TOFPET2-2018 was compatible to negative signals.

- TOFPET2-2020 is compatible to work with both signal polarizations.

- TOFPET2-2020 ASICs are integrated to the GCS and convincing results were obtained.

- Custom-design PCB has arrived!

- The tests are planned for the custom design PCB with or without magnetic field.

• Thanks for your attention!