## Online processing for Forward Tracker in PANDA

A. Malige

**PANDA Collaboration meeting - March 2021**

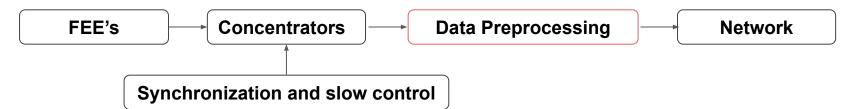

#### **DAQ in PANDA**

- The PANDA DAQ with self triggering detector systems.

- The physics events of interest are identified by an online event selection

- Tracking information is a one of the key input to distinguish signal events from background in FT.

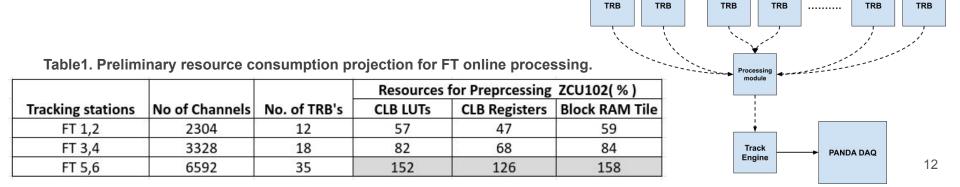

- FT data inflow from 64 TRB's (upto 2.9 GBps)

- Data volume reduction by eliminating background

- FPGA based compute nodes for online data processing.

- Abundant time b/w triggers to filter events before entering the network.

2

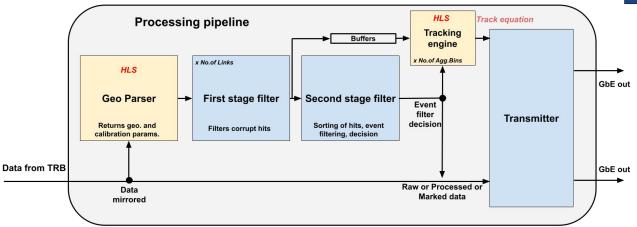

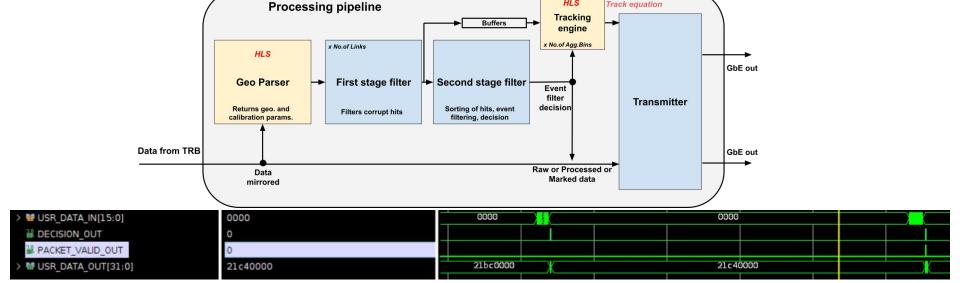

#### **Processing pipeline**

- Intermediate data processing stage.

- Push forward pipeline for event filtering and extraction of tracks.

- Tracking engine to complement the filtering.

- Using Xilinx ZCU102.

Zyng UltraScale+MPSoC ZCU102

#### Geo.Parser

## Geo. Parser and First stage filter

- Maps TDC channel and returns X, Y, Z and straw, layer, module and time Calib parameter.

- Written in C++ using HLS.

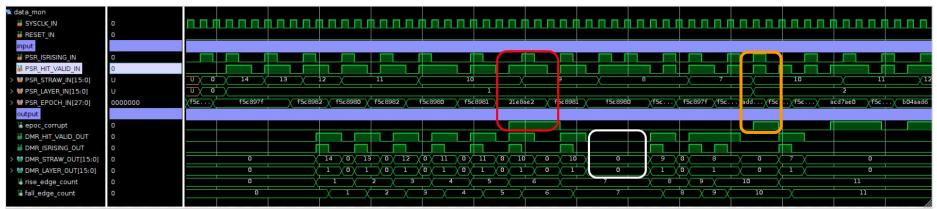

#### Filtering corrupt time

- No.of instances = No.of input links

- Artifacts of tdc implemented like missing edge ,corrupt time

- By comparing the epoch time of the straw hit with the epoch ref. time

- Data from all Links accumulated

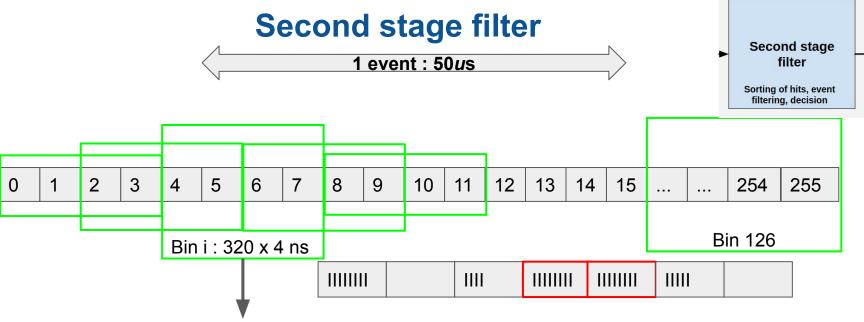

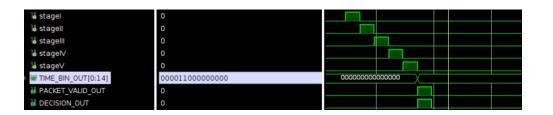

- Time bin based sorting (256 bins in a trigger window and overlap to avoid loss of hits).

- Check

- o if there is a hit from the reference detector (optional)

- o if all the layers have a hit (to form a complete track)

- o if each hit has a pair (hits from neighbouring channels is a must for a track)

- Output decision on conditions begin met and agg.Bin No of potential track

## **Buffering stage**

- Data from first stage filter buffered for the track engine.

- No. Links = No.of instances

- No of fifo's = No.of agg.time bin's

- Upon decision from second stage filter hits stored in potential timebins / fifo is read to track engine.

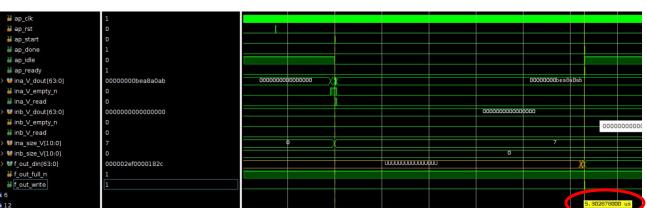

#### **Track engine**

- Written in C++ using HLS

- Primitive tracking using straw no.

- Constructs pairs & clusters of hits

- Best combination of straw pairs with least  $\chi^2$  selected

- Latency of ~6us

- Disadvantage : High resource consumption of upto 6% / inst.

| Name            | BRAM_18K | DSP48E | FF     | LUT    | URAM |

|-----------------|----------|--------|--------|--------|------|

| DSP             | -        | - 6    | -      | -      | - 53 |

| Expression      | -        |        | 0      | 1501   | 7.0  |

| FIFO            | -        | 75     | - 0    | 352    | 35   |

| Instance        | 20       | 32     | 13069  | 14392  | 0    |

| Memory          | 6        | -      | 0      | 0      | 0    |

| Multiplexer     |          | -      | -      | 597    | -    |

| Register        | -        | -      | 2383   | -      | -    |

| Total           | 26       | 32     | 15452  | 16490  | 0    |

| Available       | 1824     | 2520   | 548160 | 274080 | 0    |

| Utilization (%) | 1        | 1      | 2      | 6      | 0    |

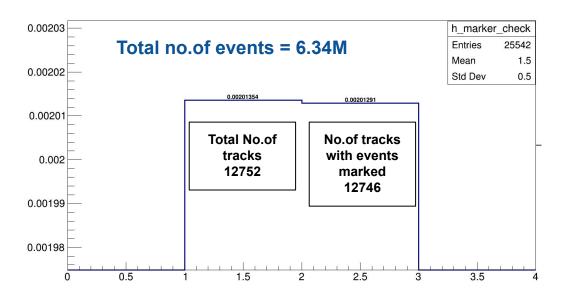

#### **Modes of Op. and Transmitter**

- Modes

- Filtering: Only filtered events are forwarded to the event builder

- Marking: Events satisfying the filtering conditions and having potential tracks are marked and all events are forwarded to the event builder

HLS

Track equation

- Bypass: All data from the TRB's is forwarded to the event builder

- Transmittes track data and raw / processed / filtered data to dedicated ports

#### **Development and Testing scheme**

Offline tracking software

(benchmark for tracks)

tracks

- A flexible development cycle

- Development by streaming stored FT data from the PC to FPGA simulators

- Or by streaming stored FT data to the hardware

- Analyze the outputs stored in PC

- Testing of the module

- Stream data to the hardware from TRB's connected to the detector

- Compare output file with the developed offline tracking software.

- PC / TRB's tracks

from ctor

ftware.

Processed data Pre-processing board (Deployed hardware)

ware must be in agreement with the offline software

raw data

Processed data

Event filtering and tracking in hardware must be in agreement with the offline software analysis of the data.

**FPGA Simulator**

( Development & testing )

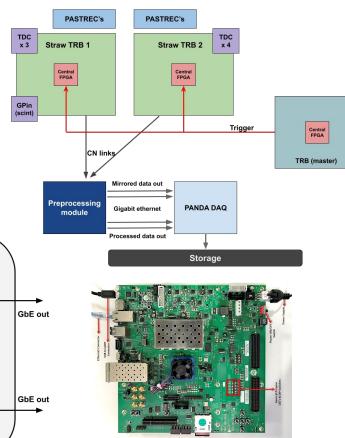

#### **Test setup**

- Processing module tested with

- Detector prototype with 4 modules in 4 layers (8 FEE's)

- Scintillator for ref.time

- Cosmics and <sup>90</sup>Sr radioactive source

- Continuous trigger at 20kHZ

- 32 time bins of width 2.5us with an overlap of 1.25 us

- Data collected for marking and filtering modes.

- Data collected with a similar prototype in 2019 under beam conditions also used for benchmarking.

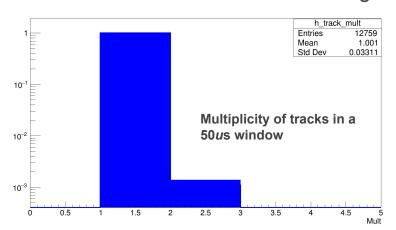

#### **Preliminary results**

- Marking: ~99.9% marking accuracy

- Filtering: 123KB/s compared to 350MB/s under <sup>90</sup>Sr with 2 TRB's

- Bypass : No data loss

- Analysis of track reconstruction efficiency under progress.

#### Scope and conclusion

- Tests of the module demonstrates the scope for immense data reduction with accurate filtering procedure.

- Push forward filtering with no latency, tracking with latency of ~ 6 7us.

- Optimizations required for PANDA production system

- Module to process data from a large no of TRB's

- Time bin width and overlap to meet rates at PANDA production system.

- Instances of Track engine could be minimized and split out into an accelerated platform.

- Serves as a platform for track visualization during online monitoring.

# Thank you