# Status of the DAQ electronics for the PANDA-EMC

- PANDA DC

- LVDS ROB

- Crate Electronics

- Backplane

- Power Supplies

- Crate Controller

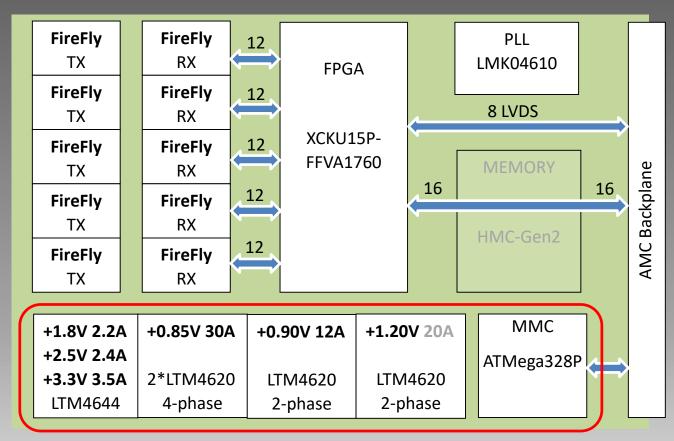

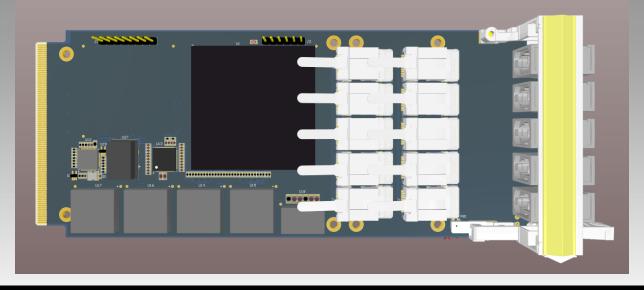

### Panda DC

# $60 \times 14 \text{ Gb/s}$

$16 \times 14 \, Gb/s$

# Status of the DAQ electronics for the EMC PANDA DC

#### PANDA DC

#### **Production and component stock**

- 1. The device has been manufactured and delivered to Uppsala

- 2. All components purchased for 10 pcs.

- 3. The FireFly modules (non-standard pig-tail lengths) are purchased for two pcs. The rest is negotiated between Uppsala, CERN and Samtec.

#### PANDA DC

#### First tests

- 1. First tests show problems with power supply. They are being investigated in Warsaw (Semicon).

- 2. The second pcb has been assembled with power supply only and still shows problems, which are not trivial to understand.

- 3. We suspect problems are coming from the fragile laminate (Megtron 7)

- 4. A new Power test pcb (FR4) is on the way

# Status of the DAQ electronics for the EMC LVDS DC

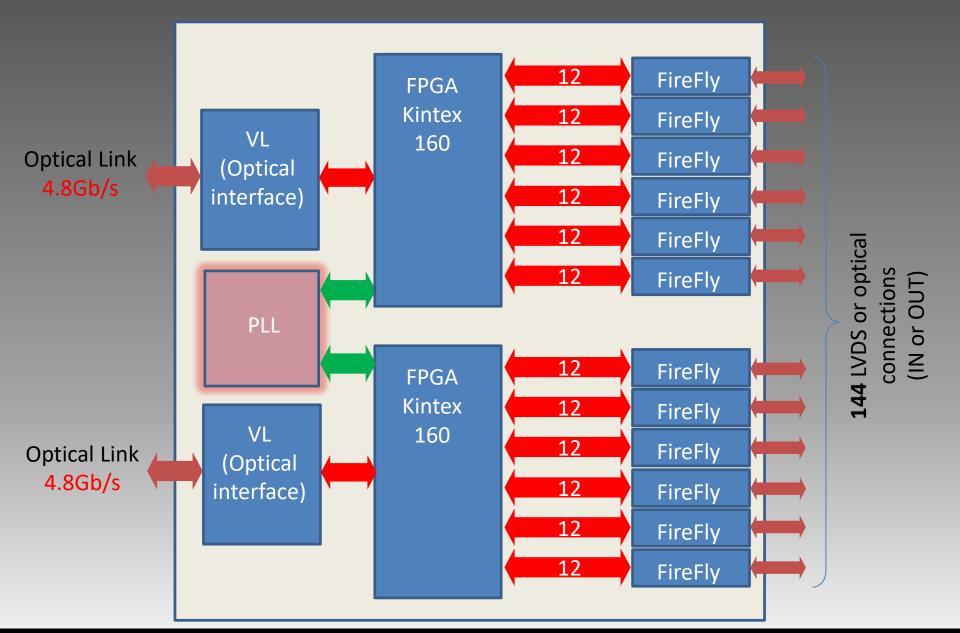

#### LVDS DC

#### A readout board/data concentrator/feature extraction device

#### **Input/output toward FE:**

As many inputs/outputs as possible handling up to 600 Mbit/s

#### **Optical interface (ECUO)**

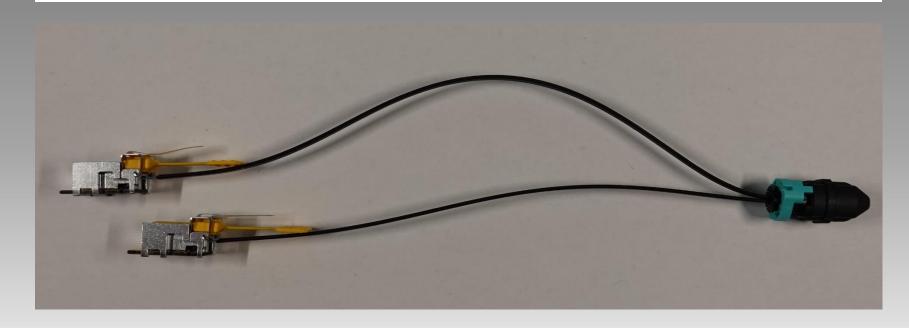

(FireFly™ Active Optical Micro Flyover System™)

or

#### **Electrical interface (ECUE)**

(FireFly<sup>™</sup> Low Profile Micro Flyover System<sup>™</sup> Cable Assembly)

or

#### **Custom interface/connector**

(to be developed on demand)

#### Input/output toward DAQ

1 or 2 optical interfaces up to 4 Gbit/s

#### **Optical interface:**

SFP/VL compatible

# Status of the DAQ electronics for the EMC LVDS DC

# Status of the DAQ electronics for the EMC LVDS DC

#### **Optical interface:**

- SFP/VL compatible

- VL obsolete

#### **Electrical interface**

- Configuration

- Reboot

- SEU handling

- Auxiliary

#### **Power**

- +1.0V 4A (FPGA INT)

- +1.5V 1A (FPGA GTX)

- +2.5V 1A (FPGA IO)

- +3.3V 1A (PLL)

- +3.3V 5A (FireFly)

#### I/O options:

#### 1. Optical interface (ECUO)

(FireFly<sup>™</sup> Active Optical Micro Flyover System<sup>™</sup>)

- 6 TX modules (72 ch.) and

- 6 RX modules (72 ch.)

#### 2. Electrical interface (ECUE)

(FireFly™ Low Profile Micro Flyover System™ Cable Assembly)

12 Firefly modules (144 LVDS channels)

#### 3. Custom interface/connector

(to be developed on demand)

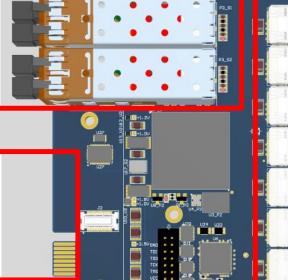

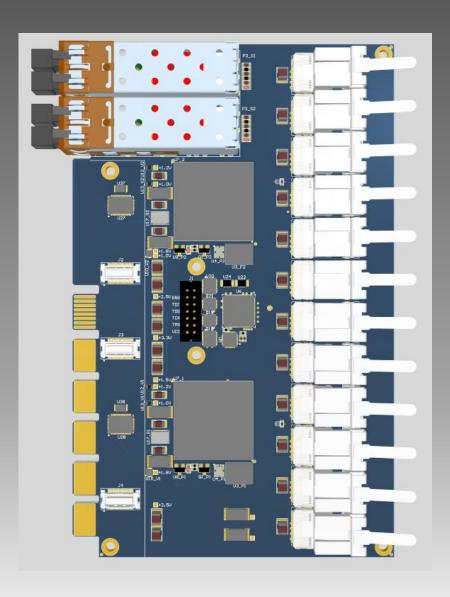

#### Status of the DAQ electronics for the EMC

#### LVDS DC

**Readout Board** obtained from the 64-channel ADC for the EMC Forward Endcap

#### Issues, which were discussed:

- Electrical specifications

- Power supply (internal/external)

- SFP/VL/VL+

- Additional functions

- Mechanical specifications

- Encapsulation

- Placement

#### **Status:**

- Re-design completed

- Ready for production

- Components need to be ordeded before expected price "adjustment"

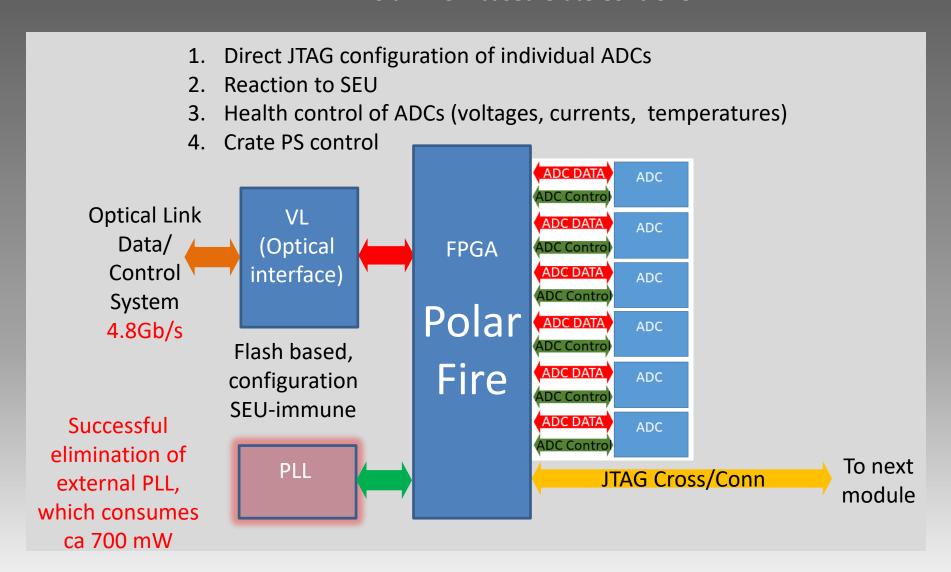

# Status of the DAQ electronics for the EMC CRATE CONTROLLER

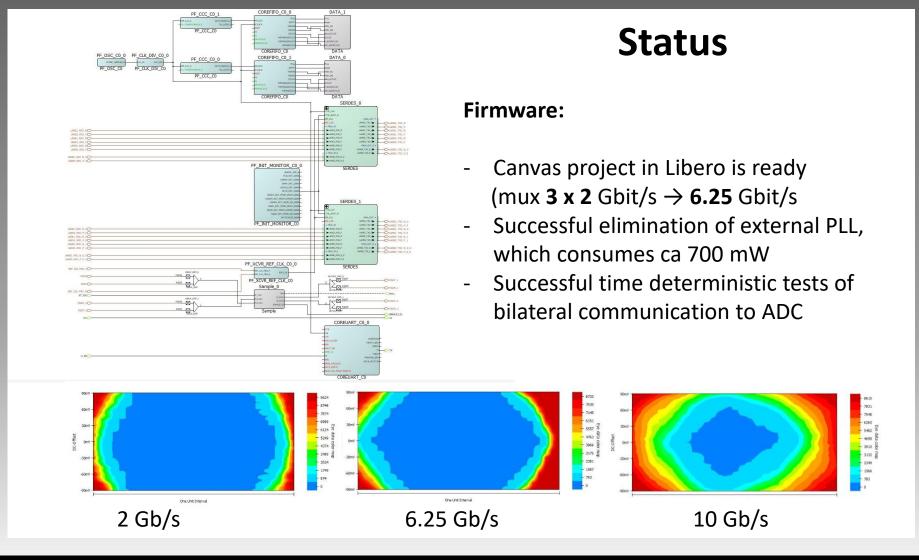

#### Polar Fire – based Crate Controller

#### Status of the DAQ electronics for the EMC

#### **CRATE CONTROLLER**

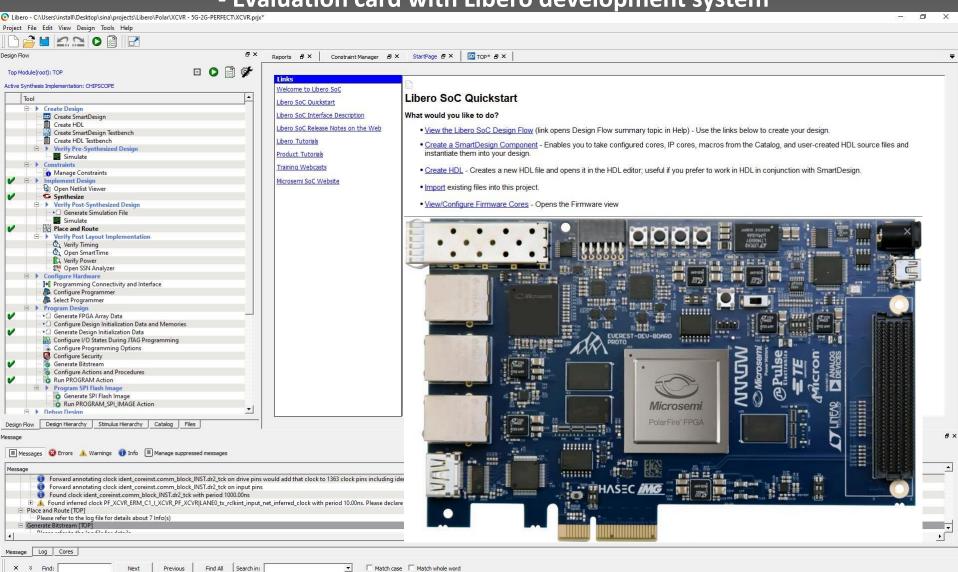

Fam: PolarFire Part: MPF300T-1FCG1152E VHDL

#### - Evaluation card with Libero development system

# Status of the DAQ electronics for the EMC CRATE CONTROLLER

#### A project containing 6 channels 2Gb/s and 2 channels 6.25 Gb/s (time deterministic)

#### **Crate Controller**

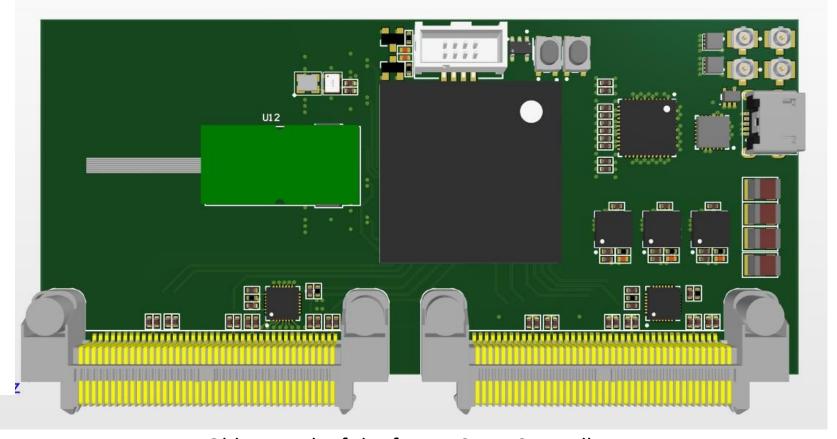

# Dual channel VTRx Test version, 2 x 4,8 Gb/s

The first prototype with VTRx

#### **Crate Controller**

#### Future plans: Dual channel VTRx+ 2 x 10 Gb/s

Old artwork of the future Crate Controller VTRx+ will be produced 2021

#### ADC for EMC-Endcap

#### **Updated plans**

- ADC production for Shashlik, tests Jan.. Aug 22

- Production needs quite urgent decision due to planned component price changes

- > Ev. ADC redesign for barrel Aug 21.. Aug 22

- Decision depends on the Pulse Detection Asic progress

- PANDA DC test Jan21..Dec 22 master, phd

- Basic debugging started, manpower will be needed in the future

- Second prototype, volume Aug 21.. Aug 22

- Based on the outcome of the first tests

- > LVDS DC tests Apr 21..Aug 22

- > Device was discussed and approved by the collaboration. It will go to prototype production

- FPGA for the bulk needs to be ordered until April 2021

- Crate controller Jan..Jun 21 master

- Debugging started, but the envisaged master student has left. I will continue anyhow.

- Power Supply tests Feb 21

- Unclear situation, since new call for experiments at AGOR left no time for an application

- Backplane Jun..Dec 21

- New backplane is ready and will be sent along with the LVDS-DC for production

## Thank You!