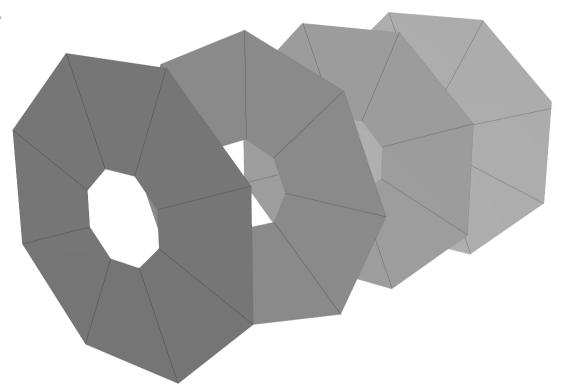

## Reminder: LMD Concept

· 10 - 50 cm between planes

#### sensors:

- · 150 / 300 μm thick

- · double-sided

#### strips

- · 50 μm pitch

- · stereo angle ~90°

rotate e.g. second and fourth plane to reduce ambiguities

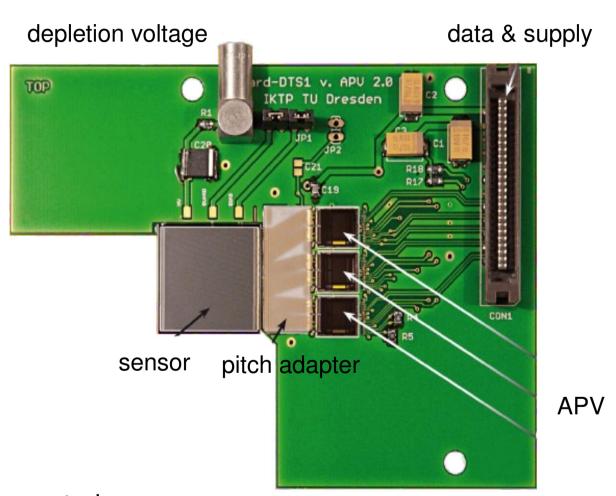

### Reminder: First Test Sensors

#### from ATLAS

- · 20.82 x 20.82 mm<sup>2</sup>

- · 300 µm thick

- · 50 μm pitch

- · 385 strips

- double-sided, BUT one-sided readout

- every 64th strip is not connected

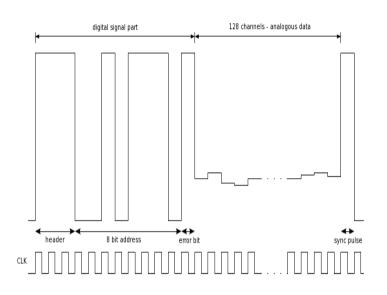

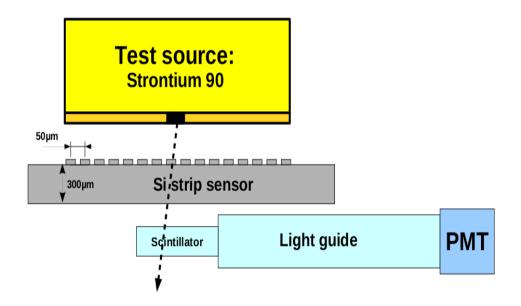

# APV25-S1 - Frontend Chip

- developed for CMS @ LHC

- · 128 channels

- · pitch 44 μm

- Preamp + Shaper + Analog-MUX

- no internal trigger

- external trigger required

- → scintillator & photomultiplier

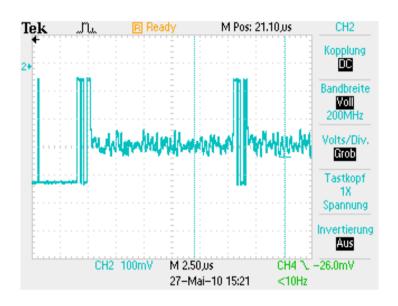

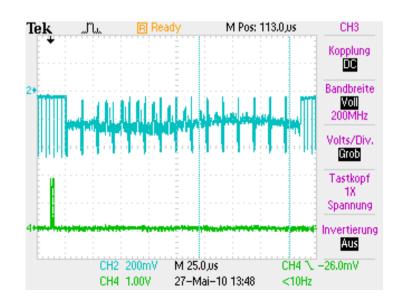

- → APV25 in 3 sample mode:

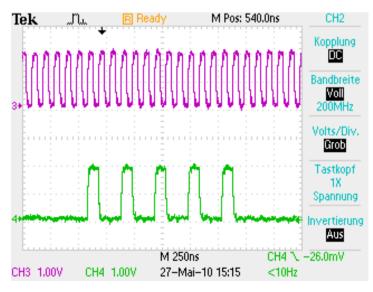

## Readout via Oscilloscope

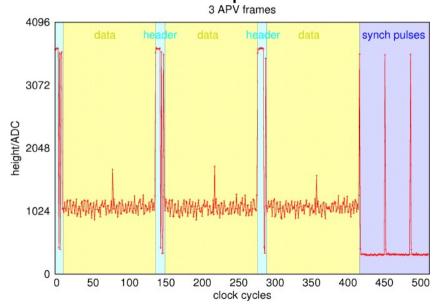

# APV - clock, trigger, frames

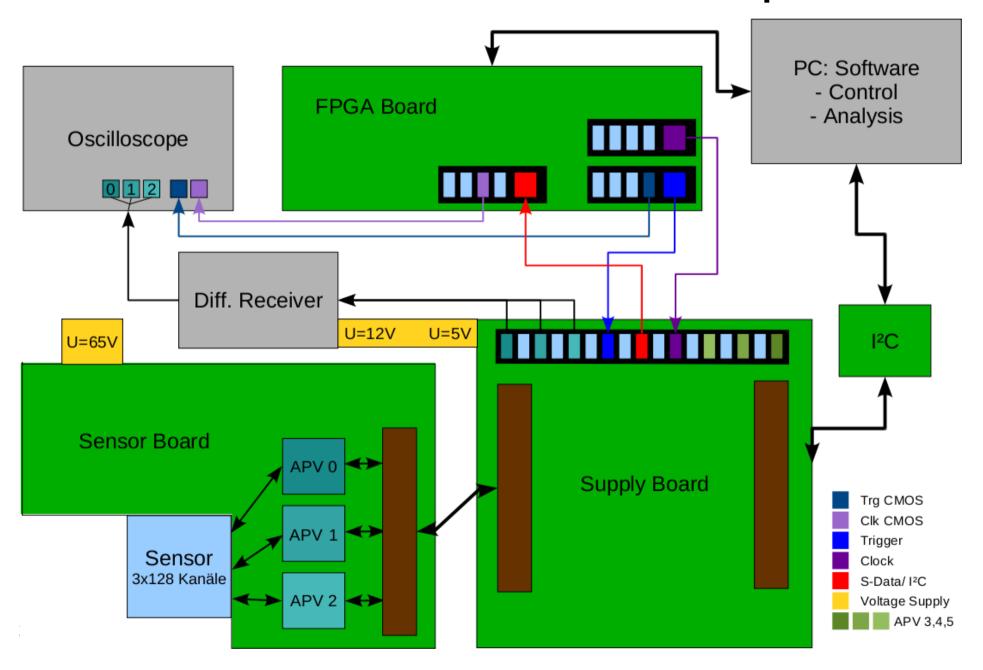

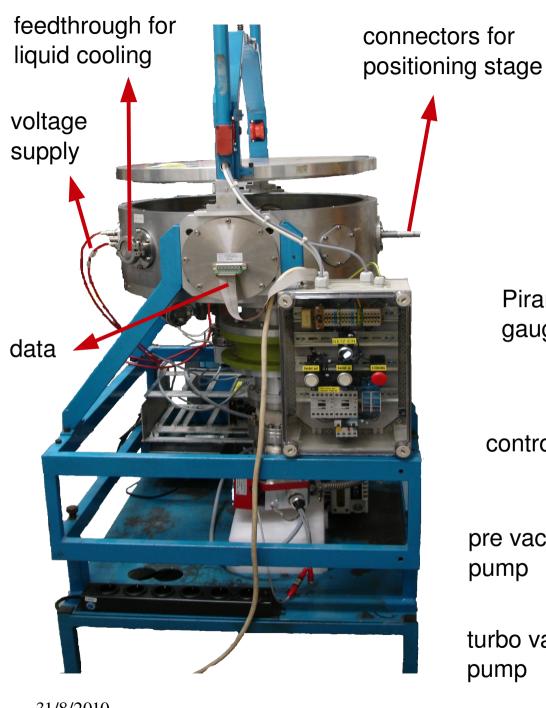

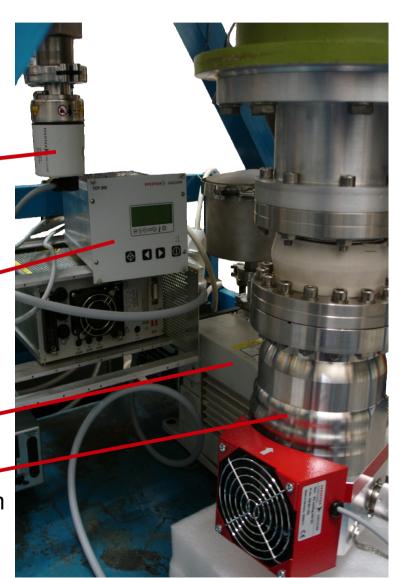

# Experimental Setup

31/8/2010

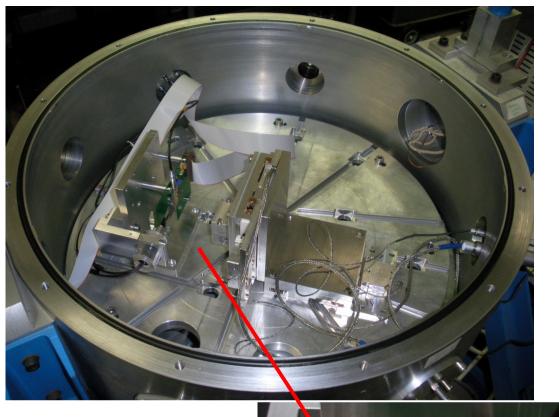

## Chamber and Vacuum

Pirani gauge

controller

pre vacuum pump

turbo vacuum pump

Sr9n

vacuum chamber

Sensor Board Sr Source & Photomultiplier

31/8/2010

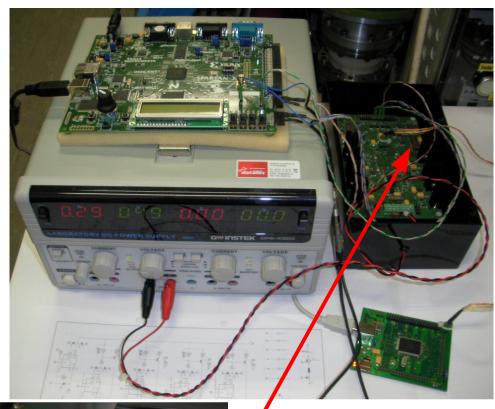

I<sup>2</sup>C Master Supply & FPGA Board

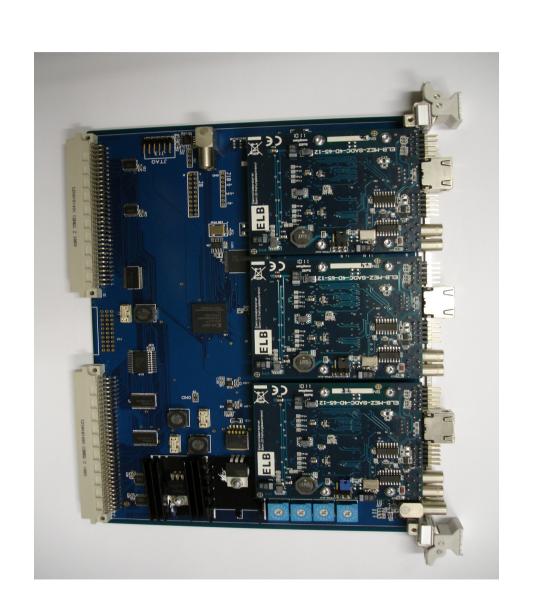

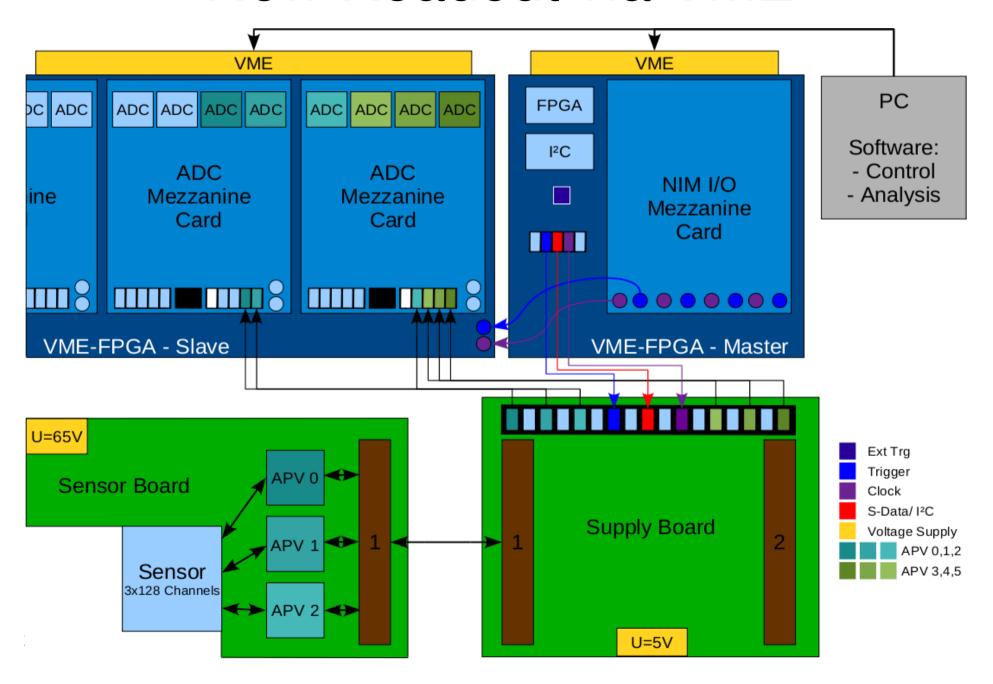

### VME-FPGA with Mezzanine-ADCs

- designed by Bonn MVD group

- combined solution for FPGA and ADC

- → VME-FPGA boards (VFB2) with ADC daughter cards

- → 3 x 4 frontends/ channels per board

- → future online zero suppression and hit and cluster finder on VME-FPGA boards

- documentation coming next week

- Bonn software has to be adjusted to Mainz VME-CPU

### New Readout via VME

### **Tests Planned**

#### testing:

- · spatial resolution

- temperature dependent SNR

- · different sensor types

- radiation hardness

#### test beams/ radiation sources:

- Sr 90  $\beta$  source

- · Electrons @ MAMI

- · Protons @ COSY

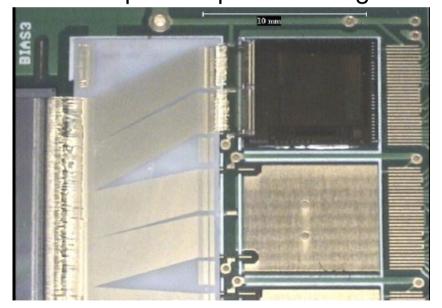

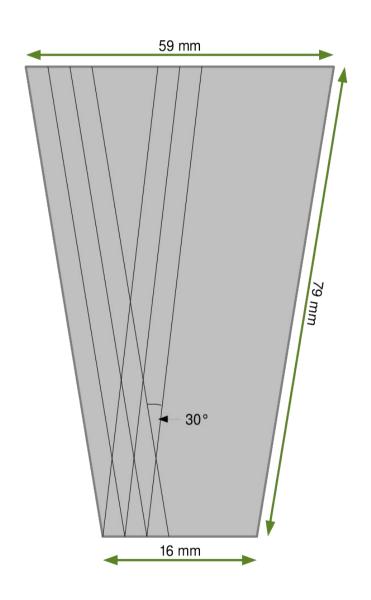

### New Sensors and ...

#### double-sided sensors from

- Micron Semiconductors "YY2"

- 300 μm sensors have arrived

- → wedge sensors used at the Dzero experiment @ Fermilab

- → cooperation with Dzero people

- connected to readout via flexible circuits: tracks and electronic parts on multiple layer bands

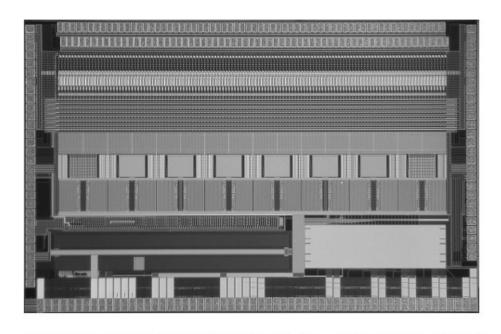

## ... alternative Frontend?

#### frontend FSSR 2 from Fermilab:

- Si Strip Readout Chip

- Self-triggered

- we got some chips (exact four!) for testing from Ray Yarema

- still to examine if they match our specifications and what Fermilab means with "self-triggered"

Fig. 1. Photograph of the FSSR2 chip with input pads at the top. The chip measures 7.5 mm x 5 mm and the input pads have an effective pitch of  $50 \, \mu m$ .

FSSR2, a Self-Triggered Low Noise Readout Chip for Si Strip Detectors – Re, Manghisoni, Yarema et. al.

## Summary

- Setup of a Test Station for double-sided silicon strip sensors in Mainz

- FPGA based readout for APV25 frontends

- Bonn software for VME readout will be adjusted to Mainz VME-CPU

- → thanks to Bonn Group Karsten and Hans for their help !!

- → first experimental setup including electronics is (almost) ready

discussions about new sensors and electronics are ongoing