# Status of development and radiation tests Forward Endcap APD HV-adjustment board

EMC-Session 11.3.2020 Ch. Schmidt

### Overview

#### Introduction/Board overview

Basic circuit

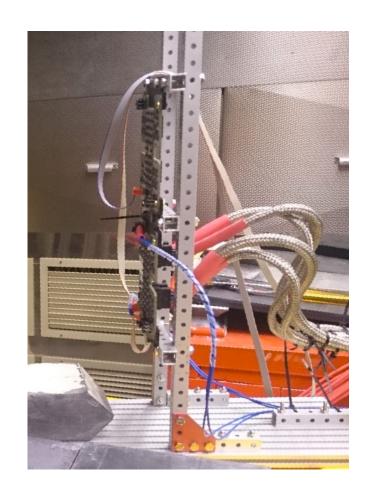

#### Irradition tests at Strahlenzentrum Giessen

- Setup (HV-Board, HV-Controller)

- First findings/effects in output voltage

#### Longterm stability

On-Board voltage measurement

### Adjustment circuit

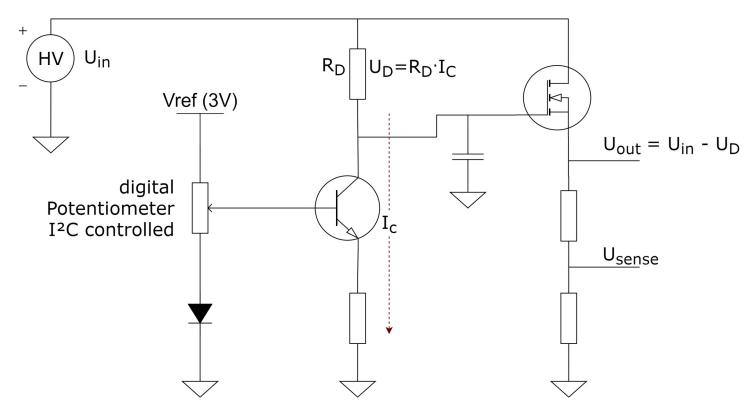

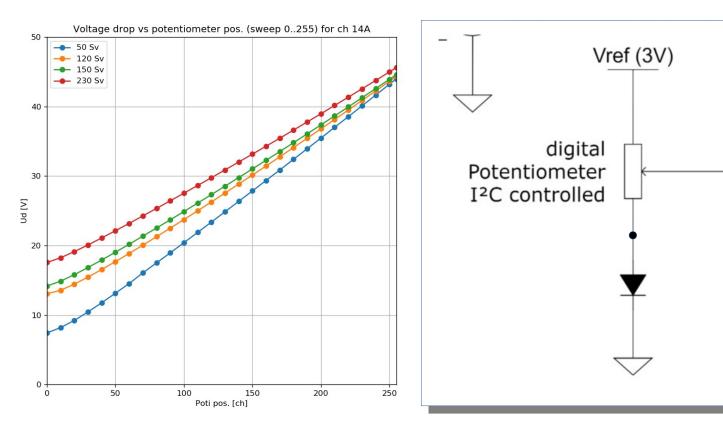

#### Basic circuit of adjustment part:

- U<sub>D</sub> adjustable via transistor, which is controlled by 8bit dig. potentiometer.

- U<sub>out</sub> sensed via high impedance voltage divider (U<sub>sense</sub>)

### Adjustment circuit

#### Basic circuit of adjustment part:

#### Output voltage:

- 8Bit potentiometer (MCP4461, 4ch)

- Adjustment range in test: ~45V (LSB: ~175mV)

- Final range smaller ~12.8V (LSB: ~50mV)

(a trade-off between ability to correct inter-channel drift and resolution)

- U<sub>D</sub>

#### APD voltage (output voltage):

- 16Bit ADC (ADS1115, 4ch and MUXer)

- LSB: ~17mV

#### APD current:

- not measured, no space to implement (needs to be a high side measurement)

- U<sub>D</sub> adjustable via transistor, which is controlled by 8bit dig. potentiometer.

- U<sub>out</sub> sensed via high impedance voltage divider (U<sub>sense</sub>)

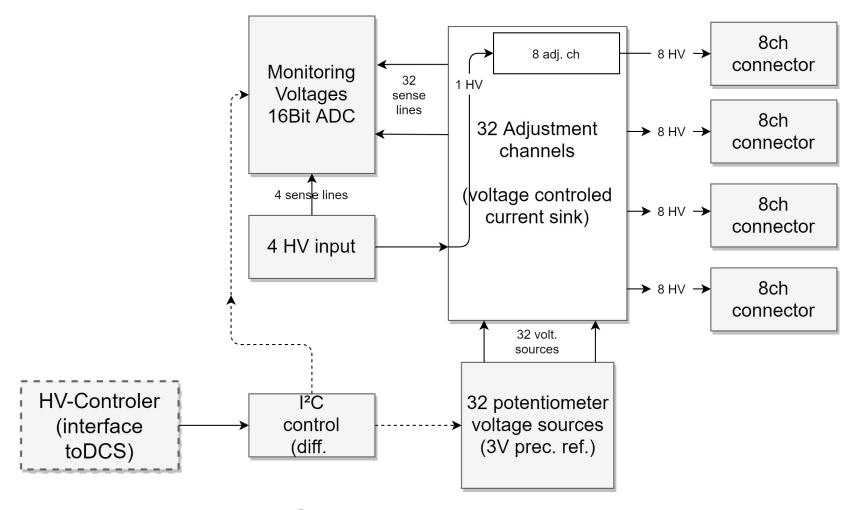

### Internal structure

Boards are cascaded on a bus of up to 15 boards.

→ To avoid address conflicts adr. translator chip is used on each board.

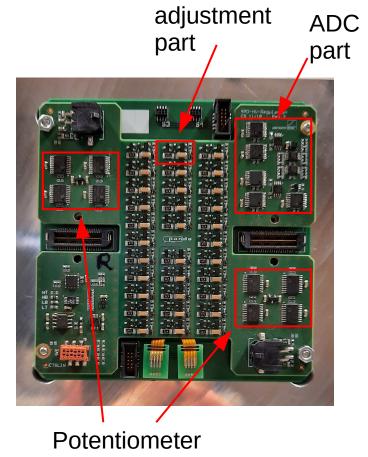

# HV adjustment board 16er

Rev 2 → 3: More Layers for better ground design (avoid I2C noise), need to change package (availability)

one

### Irradiation test

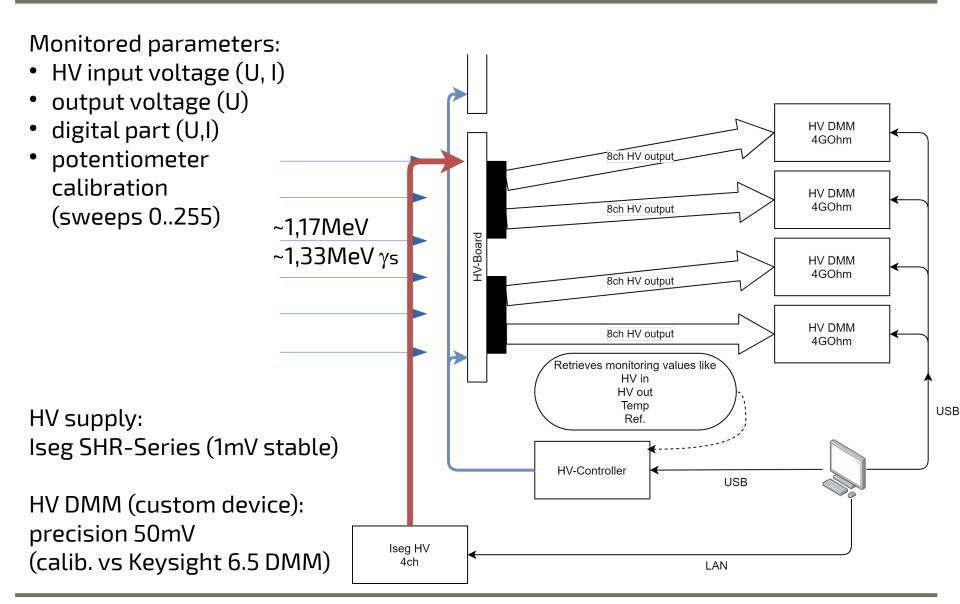

Prototypes of HV-board and controller irradiated together for testing the complete chain under normal conditions (HV and readout)

- Monitor output voltages

- Look for failures of digital components

- Monitor current consumption

Using high intensity 60Co gamma source at Strahlenzentrum Giessen

@room temp. ~20°C

### Testsetup parameters

### Dose rates - simulation

#### Dose rates in APDs (200um Si) behind the crystal of the forward endcap:

https://panda-wiki.gsi.de/foswiki/bin/view/EMC/ForwardEndcapRates

Monte Carlo simulations of the radiation dose of APDs for the forward endcap.

Done by Marc Pelizaeus Oktober 2012. Assumptions: APD of 200 um Si behind the crystals. Beam momentum of 15 GeV/c. Luminosity of 2\*10^32 cm^-2s^-1. 10 half years data taking. Please note, that this is the peak luminosity. The average luminosity is a factor of 2 lower. So all values of the table below have to be divided by 2.

| Theta [deg] | Rate [mGy/h] | Dose [Gy] | APD hits [1E10] |

|-------------|--------------|-----------|-----------------|

| 5.78        | 10.48        | 459.02    | 131.86          |

| 7.13        | 7.17         | 314.04    | 83.54           |

| 0.40        | 4.00         | 005.44    | F0.04           |

HV-boards are positioned in the back of the endcap from 13°-23° in theta

→ numbers give good estimation

dose for lumi 2·10<sup>32</sup>, 10 half years, average luminosity (50%)

lifetime dose: 4 - 29 Gy (23° - 13°)

dose rate:  $0.09 - 0.65 \,\text{mGy/h} (23^{\circ} - 13^{\circ})$

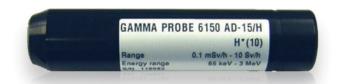

### Irradiation setup - dose rate

HV-Board and controller positioned, that rate ratio is comparable to position in forward endcap:

Dose rates were measured by devices from radiation protection

Irradiation time:

39,3 h

$$\rightarrow$$

305Sv

4,3 h no source

3h  $\rightarrow$  24Sv

Translation from  $H^*(10)$  dose rate to dose rate in silicon is still in progress  $\rightarrow$  therefore following slides are plotted against  $H^*(10)$  dose [Sv]

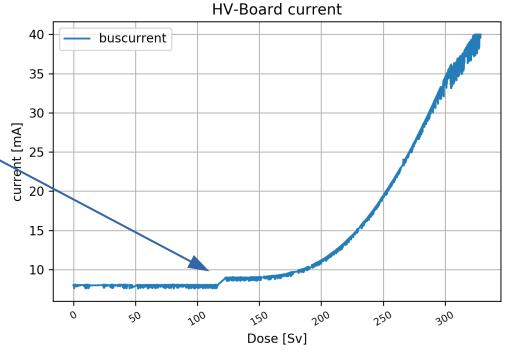

# Digital part of HV board

Digital part worked with no errors during operation of the devices (reading ADCs, setting potentiometer,...)

#### But some issues:

- Current increase after ~120Sv

- Analog switches main contributor

- non-volatile memory of potentiometer broken after 329Sv

- Change of address translation

- After switch on in lab address different

- 2 weeks later change gone (annealing effects)

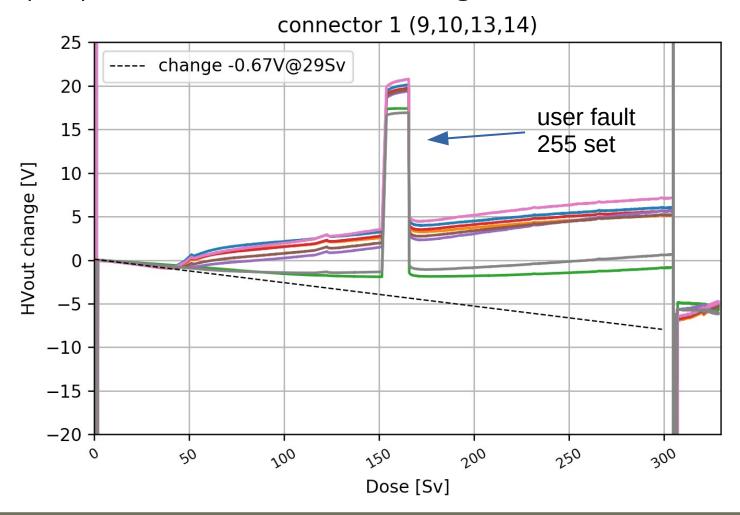

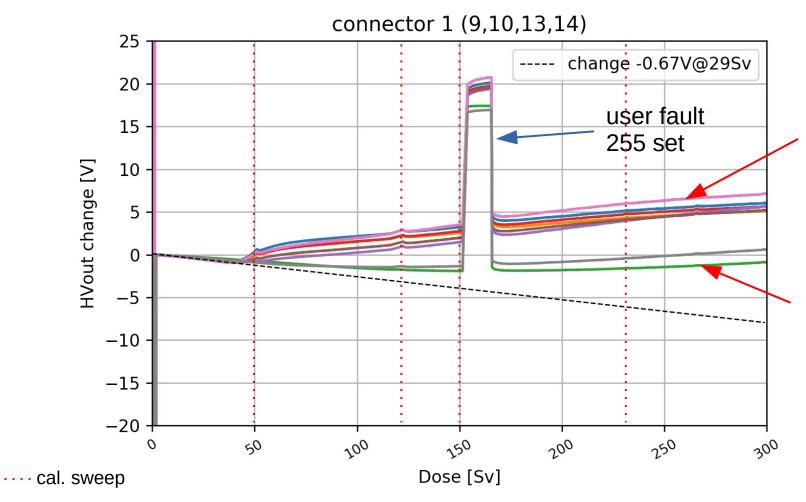

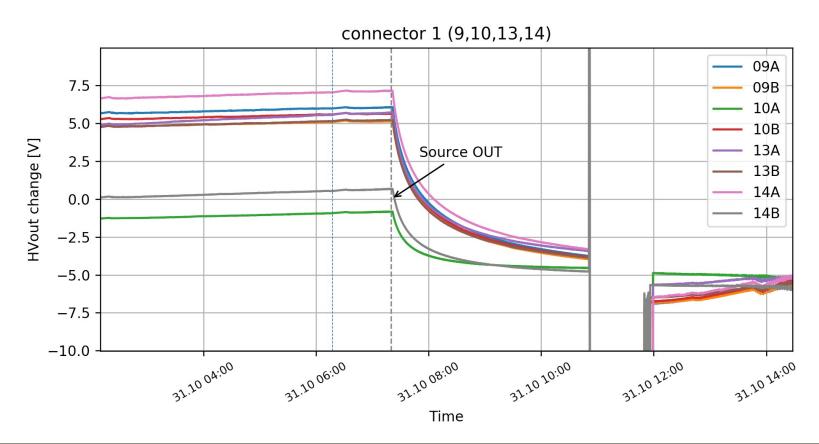

# Output voltage

Absolute output voltage change measured by external device (NOT onboard ADC) for a fixed poti. pos of 128. After 50Sv sudden change:

# Output voltage

Absolute output voltage change measured by external device (NOT onboard ADC) for a fixed poti. pos of 128. After 50Sv sudden change:

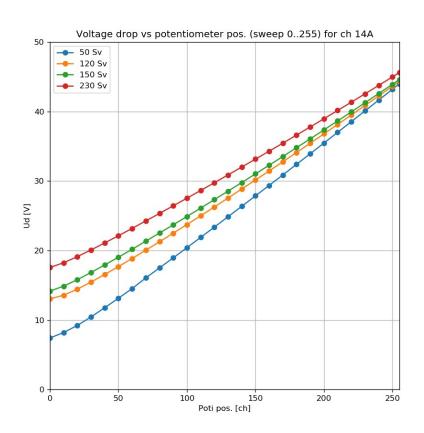

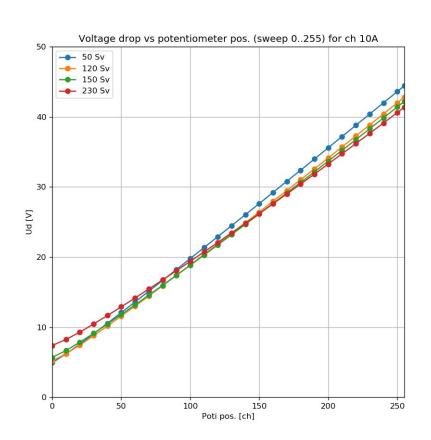

### Potentiometer calibration

#### 2 examples of change in output voltage (potentiometer calibration)

maybe change in forward voltage of diode diode makes less effect on higher poti position

not so much change visible may be compensating effects

### Potentiometer calibration

#### 2 examples of change in output voltage (potentiometer calibration)

maybe change in forward voltage of diode diode makes less effect on higher poti position

# Output voltage

After ~300Sv radiation was "switched off" and some recovery is visible.

- But not coming back to old value

- After power cycle channels do not come back to value before cycle

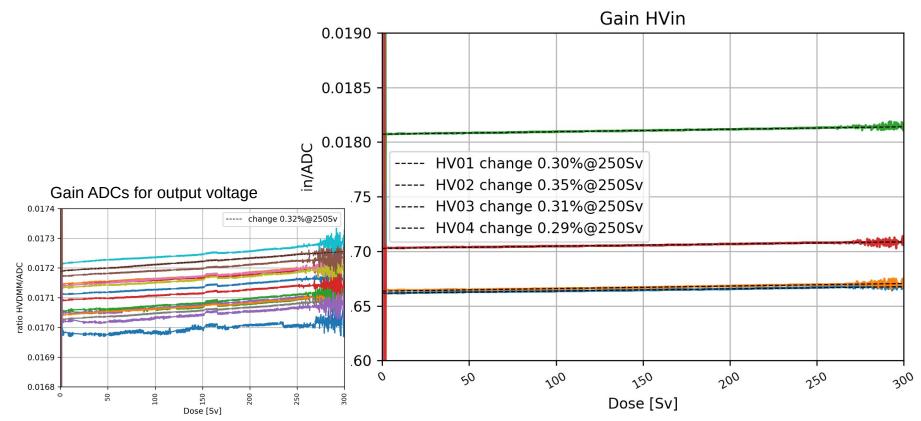

# ADC gain

Input voltages are measured by ADC → Change in ADC conversion can be checked by stable voltage from HV-supply

Example:  $0.0180V/\text{ch} * 22000 \text{ ch} = 396V \rightarrow 396V*0.003 = 1.19V@250Sv$

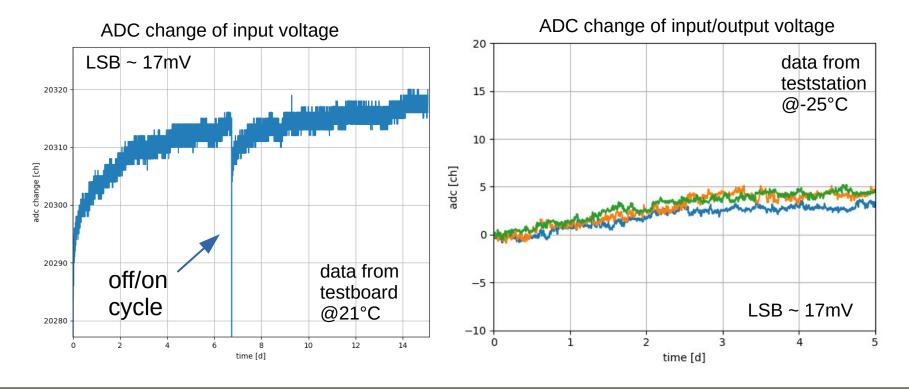

# ADC stability (onboard)

Measurement circuit needs to be stable over long time ranges (months)

- very slow drift visible at const. input voltage (370V)

- source of this effect not yet undestood

- pedestal dirft / gain change ??

### Outlook

- Continue work on translation  $H^*(10) \rightarrow dose$  in silicon

- PCB design may need some corrections (from tests)

- change of MUXer (current increase)

- adr. translator problem

- Additional tests:

- lower rate (dirft/damage "scales" with rate)

- exchange diode by resistor to test influence on output voltage

→ may be smaller effect

- effects of power cycling

- more potentiometer sweeps

- neutron/proton irradtion