65Ť

Chip Design Activities Summary and Outlook Backup Full Chip Simulation

## Outline

### Simulation and Data Analysis

- Motivation

- Full Chip Simulation

- 3 Summary and Outlook

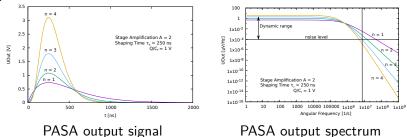

Motivation Full Chip Simulation

In May FEE workshop: Motivation of Analogue transients parameter:

- 99.9 % of signal in the spectrum below 3.17 MHz

- $\Rightarrow$  Sampling frequency: 8 MS/s

- $\Rightarrow$  8 samples to cover full pulse

- $\Rightarrow$  16 sample traces

Are theses traces really sufficient for feature extraction?

Different algorithms for time and amplitude extraction have been tested

As the latest HitDetection prototype ASIC has a bug in digital readout simulated HitDetection data was used

- Time

- Zero crossing of derivation

- Amplitude

- Maximum value

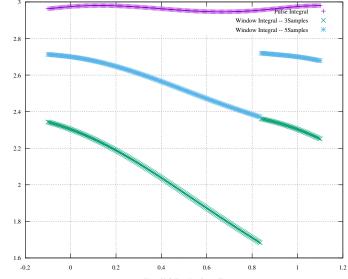

- Integral

- Window integral

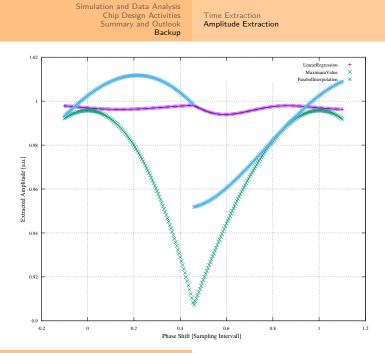

- Parabolic interpolation

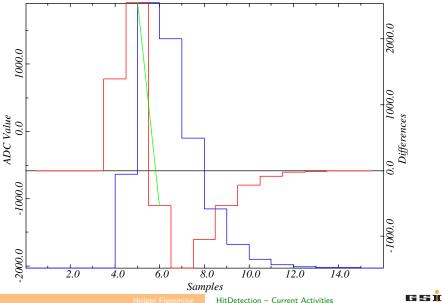

- Linear regression of transient and standardised pulse shape

Motivation Full Chip Simulation

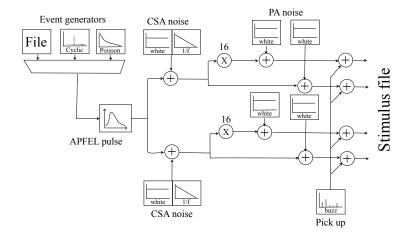

#### Stimulus generator

• Generating noisy APFEL pulses for Full Chip Simulation

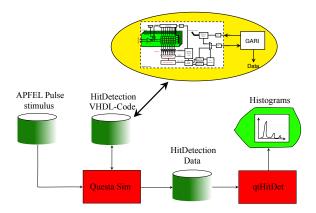

Chip Design Activities Summary and Outlook Backup Motivation Full Chip Simulation

- Feeding Stimulus data info QuestaSim simulation of HitDetection VHDL code

- HitDetection data output is written into file

- Data is analysed with described feature extraction algorithms

- Poisson distributed pulses, 50 kHz rate

- 10 discrete amplitudes 6 mV ... 1.6 V

- Logarithmic steps

- $\bullet~$  CSA white noise: 0.1 mV / 0.5 mV

- No CSA 1/f noise

- PA white noise: 2 mV / 5 mV

- $\bullet\,$  No Pick up / 20 mV 50 Hz + 5 mV 100 Hz

Chip Design Activities Summary and Outlook Backup Motivation Full Chip Simulation

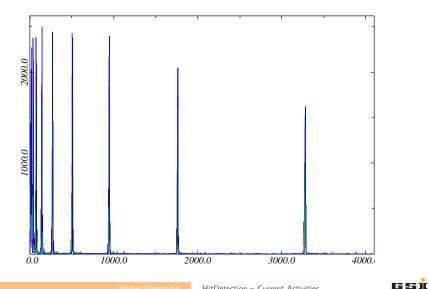

### Low Gain Amplitude Spectrum

Chip Design Activities Summary and Outlook Backup Motivation Full Chip Simulation

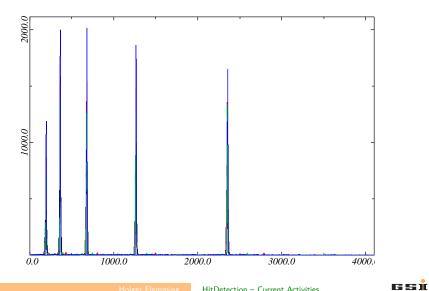

## High Gain Amplitude Spectrum

Chip Design Activities Summary and Outlook Backup Motivation Full Chip Simulation

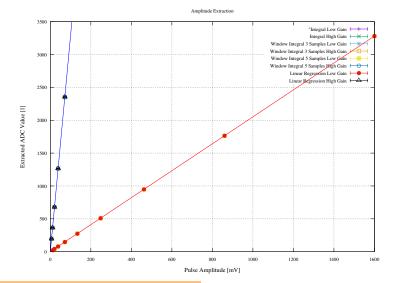

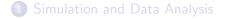

#### Amplitude Extraction

Holger Flemming

#### HitDetection - Current Activities

#### GSİ

Chip Design Activities Summary and Outlook Backup Motivation Full Chip Simulation

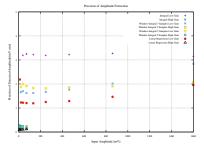

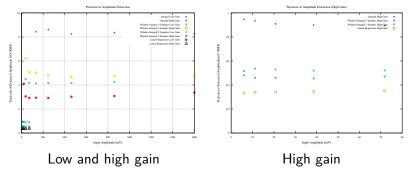

#### Precision of Amplitude Extraction

Low and high gain

Precision of Amplitude Extraction

High gain

- CSA white noise: 0.1 mV

- No CSA 1/f noise

- PA white noise: 2 mV

- No Pick up

Chip Design Activities Summary and Outlook Backup Motivation Full Chip Simulation

#### Precision of Amplitude Extraction

- CSA white noise: 0.5 mV

- No CSA 1/f noise

- PA white noise: 5 mV

- $\bullet$  Pick up: 20 mV 50 Hz + 5 mV 100 Hz

Chip Design Activities Summary and Outlook Backup Motivation Full Chip Simulation

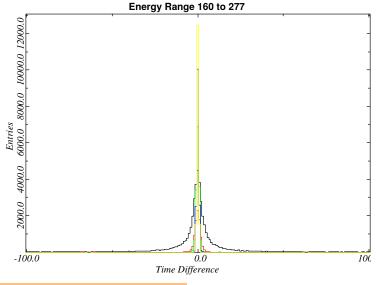

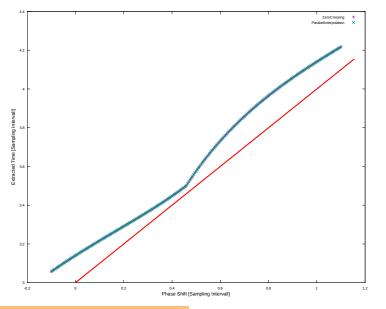

#### Time Extraction

65Ť

Chip Design Activities Summary and Outlook Backup Motivation Full Chip Simulation

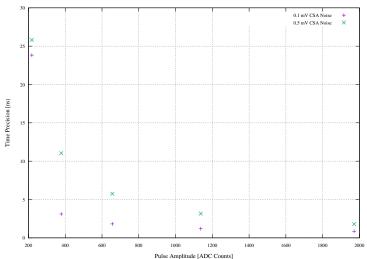

#### Precision of Time Extraction

Time Precision vs Signal Amplitude

olger Flemming

#### HitDetection - Current Activities

GSİ

Analogue Memory Input Buffer and Discriminator Floor Planning

# Outline

2 Chip Design Activities

- Analogue Memory

- Input Buffer and Discriminator

- Floor Planning

## **3** Summary and Outlook

G 5 1

Analogue Memory Input Buffer and Discriminator Floor Planning

Chip design activities towards a 16 channel prototype for barrel readout are ongoing

- Scaling analogue memory

- Input buffer and discriminator

- Floor planning

Analogue Memory Input Buffer and Discriminator Floor Planning

### Analogue Memory Scaling

- Current analogue memory has four rows per channel with 8 columns

- Number of columns is increased to 16

- Schematic and layout design is finished

- Currently owing:

- Simulation of parasitic extraction

- Matching with read out integrators

Analogue Memory Input Buffer and Discriminator Floor Planning

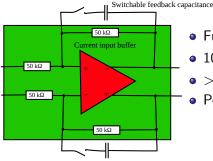

- Fully differential, gain 1

- 100 kΩ differential input resistor

- > 50 MHz bandwidth

- Possible modification:

- Low pass characteristic by switchable feedback capacitances

- Anti aliasing

- Suppression of high frequency pick-up

r s u

- Noise reduction

- First simulations very promising

Analogue Memory Input Buffer and Discriminator Floor Planning

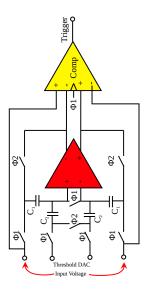

## • Φ<sub>1</sub>

- Storing input voltage in  $C_1$

- Storing threshold Voltage in  $C_2$

## • Φ<sub>2</sub>

- Switching  $C_1$  into feedback

- Transferring charge from  $C_2$  to  $C_1$

- Output voltage:

- $U_{in} C_2/C_1 U_{thres}$

- Used as comparator threshold

- Leading edge of  $\Phi_1$

- Taking comparator decision

$$\begin{split} & U_{in}(t) > U_{in}(t - \Delta t) - \frac{C_2}{C_1} U_{Thres} \\ & \Rightarrow \frac{\Delta U_{in}}{\Delta t} < \frac{C_2}{C_1} U_{Thres} \end{split}$$

r s u

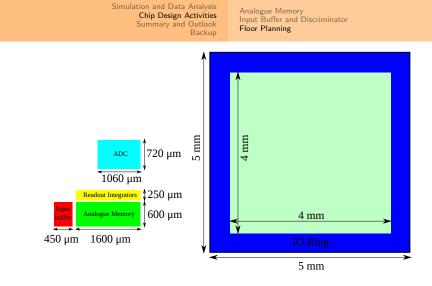

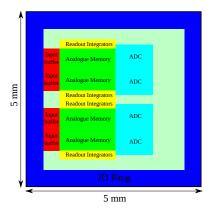

- For MPW prototype runs the design has to fit into 5 by 5 mm<sup>2</sup> blocks

- approx. 15 kEuro / block

65T

Analogue Memory Input Buffer and Discriminator Floor Planning

- 9.58 mm<sup>2</sup> for full custom blocks will fit into 1  $5 \times 5 \text{ mm}^2$  block

- 6.42 mm<sup>2</sup> for power routing and digital logic Sufficient area??

65T

## Outline

- 2 Chip Design Activities

- Summary and Outlook

Holger Flemming HitDetection – Current Activities

# Summary and Outlook

- Different feature extraction algorithms have been tested with simulated HitDetection data

- Time as well as amplitude extraction works very well

- Extraction quality depends on numerical effort

- High quality feature extraction from 16 sample traces is feasable!

- Analyses have to be checked with measured data. Corrected HitDetection prototype is expected this month.

- Design work towards a 16 channel prototype for barrel readout is ongoing

# Thank you for your attention

Holger Flemming HitDetection – Current Activities

Time Extraction Amplitude Extraction

# Backup

Holger Flemming HitDetection – Current Activities

Time Extraction Amplitude Extraction

Amplitude Extraction Summary and Outlook Backup Integral Extraction 8000.0 10000.0 12000.0 2000.0 1000.0 ADC Value 0.0 6000.0 Integral 4000.0 -1000.0 2000.0 -2000.0 0.0 2.0 4.0 6.0 8.0 10.0 12.0 14.0 Samples GSİ

Time Extraction

Simulation and Data Analysis Chip Design Activities

HitDetection - Current Activities

- Based on extracted time a standardised APFEL pulse is generated (green)

- For each sample: Standard APFEL pulse value and transient ADC value

- Linear regression (right side)  $\Rightarrow$  baseline, amplitude

- $\Rightarrow$  reconstructed APFEL pulse (red)

Time Extraction Amplitude Extraction

Holger Flemming

HitDetection - Current Activities

GSĬ

Extracted Amplitude [a.u.]

Time Extraction Amplitude Extraction

Phase Shift [Sampling Intervall]

GSİ

Holger Flemming

#### HitDetection - Current Activities

#### GSI