### **MVD SPD**

# Status report of the readout architecture design for the PANDA silicon pixel detectors

### **Outline**

- \* ToPiX version 3 architecture

- \* Clock frequency issues

- \* Data transmission

- \* Power supplies

# ToPiX specs

- \* Pixel size :  $100 \mu m \times 100 \mu m$

- \* Chip active area: 11.4 mm × 11.6 mm (116 rows, 110 cols)

- \* dE/dx : Time over Threshold, up to 100 fC

- \* Analog noise floor : < 32 aC ( 200 e<sup>-</sup> )

- → System clock frequency : 155÷160 MHz

- Max event and data rates: 12.3 MHz/cm<sup>2</sup> 815 Mb/s/chip (?)

- \* Power consumption : < 500 mW/cm<sup>2</sup>

- \* Total Ionizing Dose : < 100 kGy

- \* Equivalent neutron fluence : < 5·10<sup>14</sup> 1MeV n<sub>EO</sub>/cm<sup>2</sup>

# ToPiX v2

- Full pixel cell ( analogue + digital )

- Two folded columns with 128 cells

- Two columns with 32 cells

- 5x2 mm<sup>2</sup> die area

- CMOS 0.13 μm LM technology

- Working frequency: 50 MHz

- Dice-based SEU resistant FFs

- Tests:

- → test bench

- → with a sensor and a radiation source

- $\rightarrow$  TID and SEU

# ToPiX v3

New prototype in 0.13 µm under development – main changes :

- \* BEOL option: DM

- \* Standard cells library : IBM

- \* Clock frequency: 155÷160 MHz

- \* SEU protection: triple redundancy

- \* More compact analog part

# System aspects

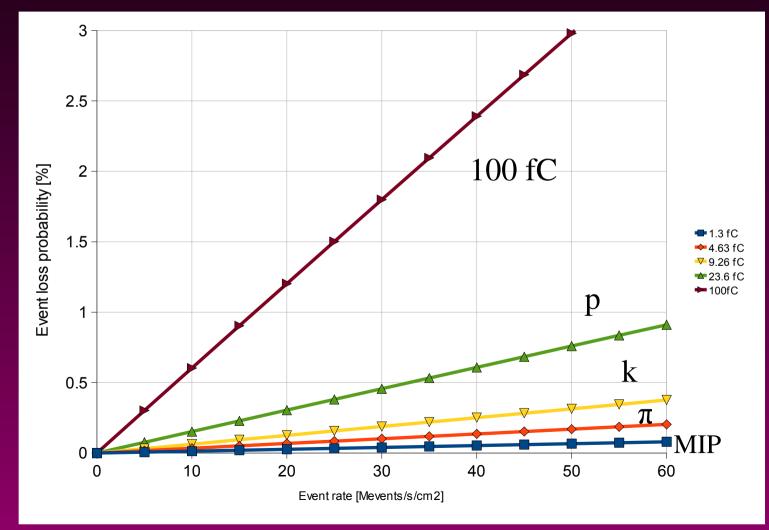

- Time resolution: 1.8 ns r.m.s. @ 160 MHz

- Pixel readout time: 8 clock cycles (50 ns)

- ToT gain: 62.5 ns/fC

- Pixel dead time (a) 1.3 fC:  $\sim$ 90 ns

- Pixel dead time @ 100 fC : ~6 µs

- Chip active area: 1.32 cm<sup>2</sup>

- Bits per event: 50

# **Event loss probability** *ToT contribution*

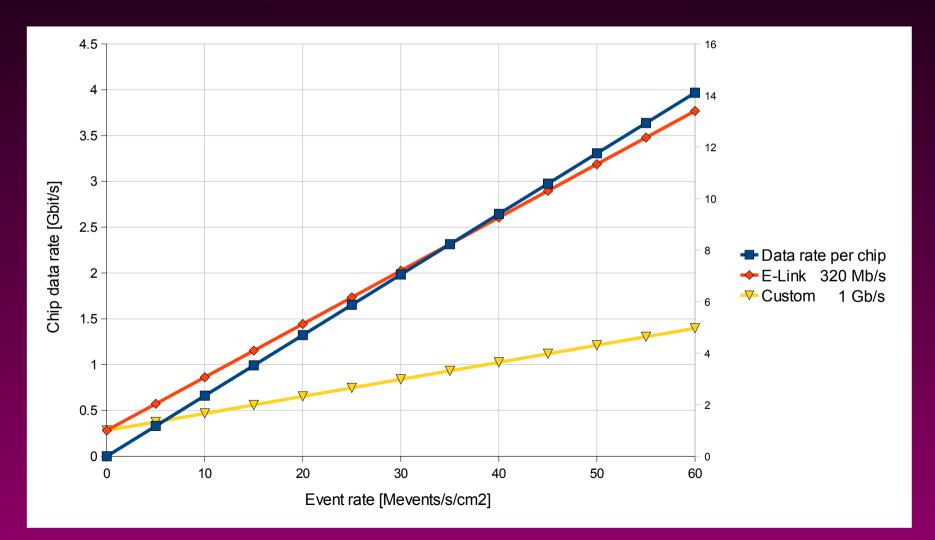

# Data rate vs event rate

# **MVD** pixel requirements

#### Basic considerations:

- in a triggerless environment SPDs generate a lot of data (currently 50 bits/hit : address+time reference+ToT)

- to fit space and material requirements, we need electrical to optical conversion as close as possible to the detector

- electronics has to be radiation hard

- no COTS components can be used

- looking for solution in the HEP community, especially at development for LHC-sLHC

### **Clock issue**

- 1. ToPiX is (almost) completely synchronous

- \* most performances are defined by the clock (time resolution, dead time, transmission bandwidth, ToT gain)

- \* we do need to freeze the clock frequency (at least  $\pm 10\%$ )

- 2. LHC electronics is based on a 40 MHz clock

- \* in principle many ASICs can work at different frequencies but it is not guarantee (ref. QPLL)

- \* for pixel it would be safer to for a 2<sup>N</sup>×40 MHz clock

- \* any other PANDA detectors plan to use LHC electronics?

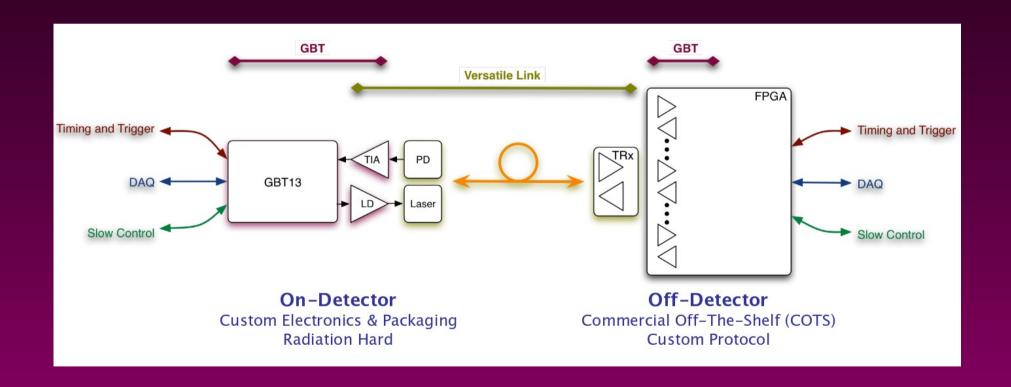

# **GBT** project

### **GBT** chipset

#### Radiation tolerant chipset:

- \* GBTIA : Transimpedance optical receiver

- \* GBLD : Laser driver

- \* GBTx : Data and Timing Transceiver

- \* GBT-SCA: Slow control ASIC

#### Supports:

- \* Bidirectional data transmission

- \* Bandwidth:

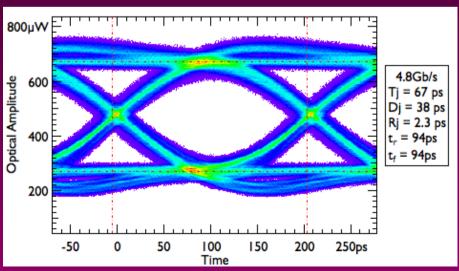

- $\rightarrow$  Line rate : 4.8 Gb/s

- → Effective : 3.36 Gb/s

#### Target Applications:

- \* Data readout

- \* TTC

- \* Slow control and monitoring links

#### Radiation Tolerance:

- \* Total dose

- Single Event Upset

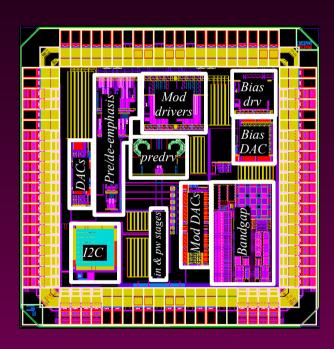

- GBLD: 5 Gb/s laser driver

- Modulation current : 2÷24 mA

- Bias current: 2÷43 mA

- Pre-emphasis/de-emphasis current: 0÷12 mA

- I2C digital control

# Data transmission

Sezione di Torino

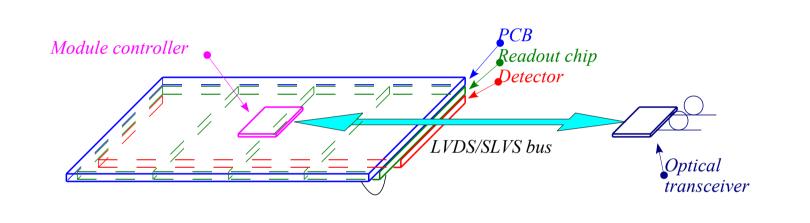

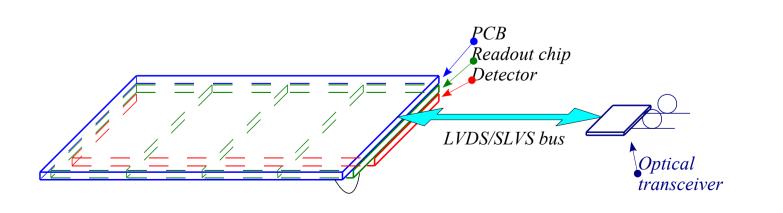

Option 1

Option 2

# **Electrical link**

#### E-link

- \* Under development for the GBT interface

- \* Up to 320 Mbit/s

- \* Direct connection to the GBT

- \* More cables, less design work

#### Custom design

- \* Target: 1 Gbit/s

- \* Common development : PANDA MVD and NA62 GTK

- \* More design work, less cables

# **Power supply**

- \* Deep submicron technologies requires lower voltages (0.35  $\mu m \rightarrow 3.3 \text{ V}, 0.25 \ \mu m \rightarrow 2.5 \text{ V}, 0.13 \ \mu m \rightarrow 1.2 \text{ V}$ )

- \* Power saving (~same current, lower voltage) but...

- power drop on lines and voltage regulator become critical!

- \*  $500 \text{ mW/}1.2 \text{ V} = 420 \text{ mA} \times 3 \Omega = 1.26 \text{ V} \rightarrow 51\%$  efficiency loss for cabling only

- \* Two solutions are under study in the sLHC community:

- serial powering

- DC-DC converters

### Serial powering

- \* ATLAS (not official) choice

- \* N modules are connected in series with a N×V<sub>DD</sub> voltage

- \* Shunt regulator to ensure voltage drop (keep current constant)

- \* AC connection to the detector and to the DAQ

- \* Three configurations:

- W: on chip shunt regulator and shunt transistor

- M: on chip shunt transistor, external shunt regulator

- SPi ext : external shunt regulator and shunt transistor

### **DC-DC** converter

- \* CMS official 1st choice

- \* Direct voltage conversion via PWM

- \* Commonly used in consumer electronics

- \* High efficiency

- \* Issues for HEP experiments:

- \* noise

- inductors in magnetic field

## **MVD** power scheme

- \* Just started looking at the issue

- \* No manpower for a custom solution

- \* Very first feeling : DC-DC looks better

- \* PANDA and sLHC timeschedule are similar

- → we can wait and see who will be the winner...

### Conclusions

- Design of the ToPiX v3 started

- \* still under the sword of Damocles of the clock frequency...

- \* Ongoing studies on the full architecture:

- \* electrical data transmission

- \* optical conversion and DAQ interface

- \* power supply