Institut

d a рапда

# **Updates on the MVD-Strip-Detector**

Entries 223212

80

60

#### **Detector Development**

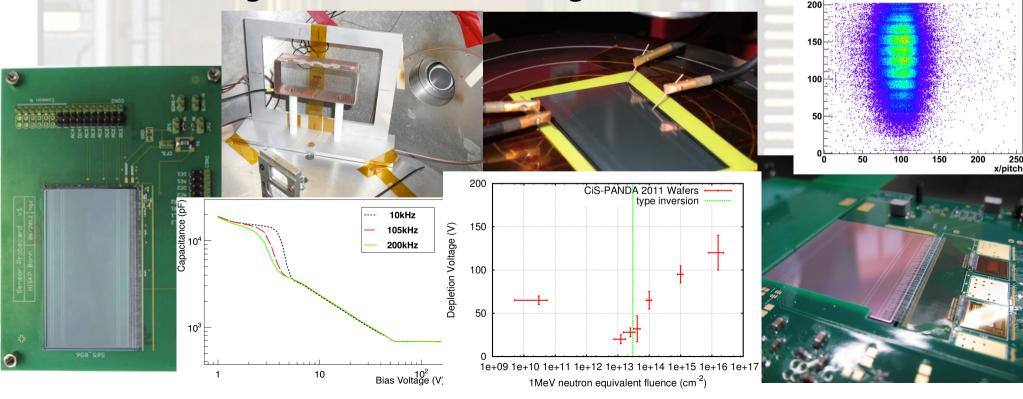

barrel sensors been intensively tested

Institut

- new engineering run submitted beginning 2013

- → investigate different biasing method

IFSSEN

Institut

#### **Detector Development**

- disk sensors engineering run arrived @Jülich

- CiS Erfurt, same technology as barrel sensors

| strip implants:    | 512 p <sup>+</sup> -strips in n-substrat<br>and 512 n <sup>+</sup> -strips for the<br>backside. | 36.87        |                  |

|--------------------|-------------------------------------------------------------------------------------------------|--------------|------------------|

| Strip orientation: | parallel to the long sensor<br>edges, skew angle = 15°                                          | Stereo angle |                  |

| pitch:             | 67.5 μm                                                                                         | 1001         |                  |

| Biasing:           | punch-through                                                                                   | 19.94        |                  |

| n-side charge sep: | p-spray                                                                                         | 21.69        |                  |

| height:            | 57.67 mm                                                                                        | 21.69        |                  |

| thickness:         | 250 – 300 µm                                                                                    |              | MVD group Jülich |

Institut

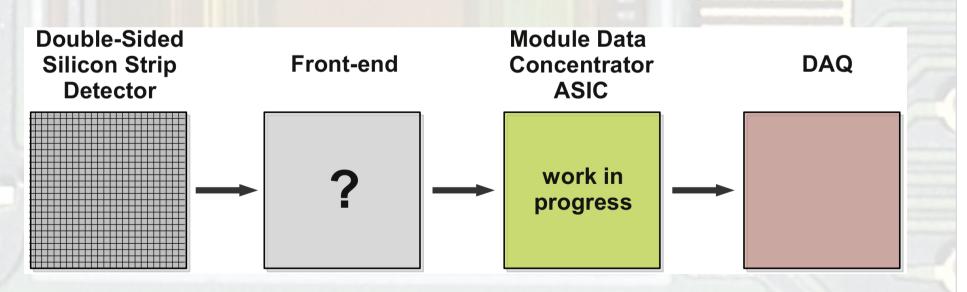

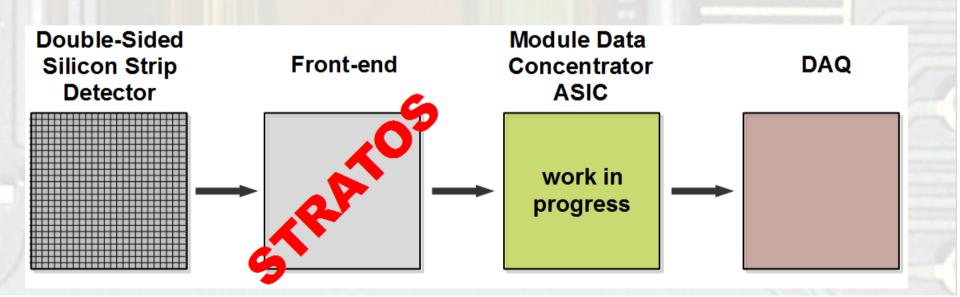

#### **Front-end Status**

- decision for the strip detector front-end made

- based on TOFPET ASIC (EndoTOFPET-US coll.)

- modifications towards silicon strip detectors already started at INFN Torino

Institut

#### **Front-end Status**

- decision for the strip detector front-end made

- based on TOFPET ASIC (EndoTOFPET-US coll.)

- modifications towards silicon strip detectors already started at INFN Torino

VIVERSITÄT

SSEN

**MVD group Turin**

#### **Front-end Features**

self-triggering, fully digital data output

Institut

- analog part customized to sensor capacitance

- short ToT to avoid pile-up

- fast sampling (binning ~100ps)

- using TDCs based on time interpolation

- high digitization resolution

- clustering to improve spacial resolution

- energy loss information as additional PID input

**FSSEN**

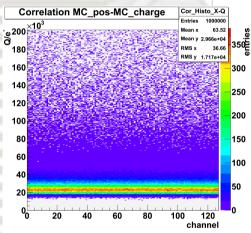

## **Strip Front-end Simulation**

fast and flexible using C++ and Root to compare with VHDL simulations

Institut

- Features (so far):

- adjustable number of channels (64 vs. 128)

- adjustable sensor thickness (charge)

- uniform distribution in position, landau distribution in charge

- double strip hit with charge sharing (CoG)

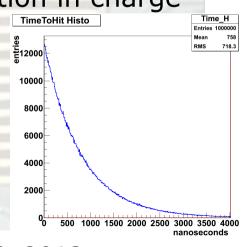

- exponential distribution in time

- wave-form from device simulation

- ... work in progress • **MVD** group Gießen

Institut

## **MVD Strip-Detector count**

|            | Barrel Part                  | Disk Part      | Sum  |

|------------|------------------------------|----------------|------|

| Sensors    | 184 rectangular<br>64 square | 48 trapezoidal | 296  |

| Front-ends | 2536 (64 ch)                 | 768 (64 ch)    | 3304 |

| DC-DCs     | 1240                         | 240            | 1480 |

| MDCs       | 248                          | 48             | 296  |

Institut

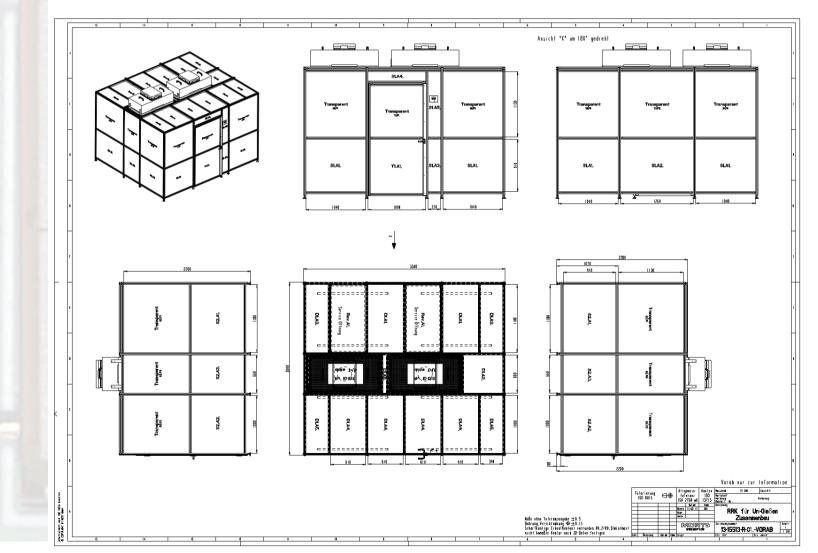

#### **Gießen Infrastructure**

- installed beginning of April

- size: 3,00 x 3,50 m<sup>2</sup>, internal height: 2,20 m

- approx. 10m<sup>2</sup> clean room space

- designed for ISO 6

- measured to comply better then ISO 6

Institut

#### **Gießen Infrastructure**

bonding machine: F&K Delvotec 5630 already in Gießen will be assembled soon

wafer prober: Cascade Microtech PA200BlueRay ordered

Institut

Institut

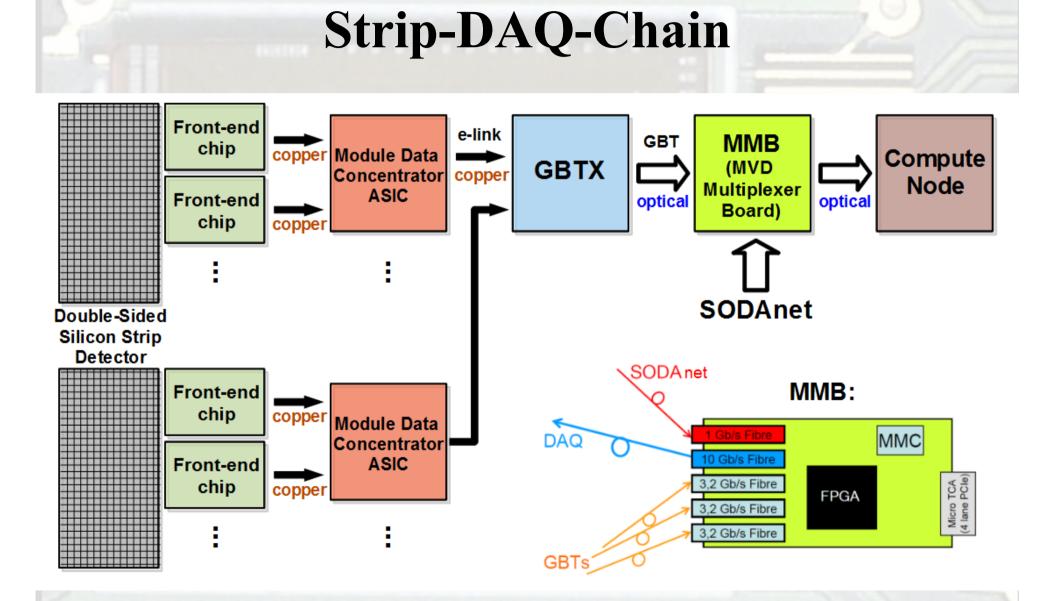

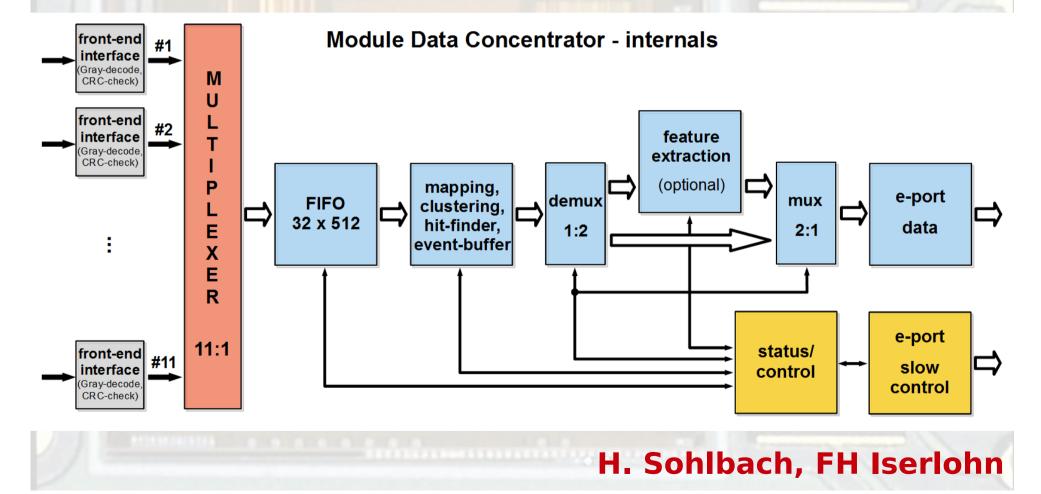

#### **Module Data Concentrator**

- all front-ends of one strip sensor connected to one module data concentrator ASIC (MDC)

- front-end data:

- strip address

- time information

- ToT

- e-links (GBT) will be used for data transfer and slow control

#### H. Sohlbach, FH Iserlohn

Institut

#### **Module Data Concentrator**

Institut

#### **Module Data Concentrator**

- Status as of April 2013

- design versions: with/without feature extraction

- design & simulation of FPGA prototype (VHDL-based) finished for:

- 11:1 multiplexer, FIFO, clustering/hit finding

- in design/redesigning: triple redundancy, clustering/hit finding, e-link, status/control

- work on the specification of the front-end/module controller interface in progress

#### H. Sohlbach, FH Iserlohn

FSSFN

### Summary

strip front-end in development

Institut

- MDC in development

- => both developed for the specific requirements of the PANDA MVD

- feature set customized to our requirements

- no dependence on external developments

## **Thank you for** your attention

#### **STRATOS** = **ST**rip **R**eadout **A**SIC **TO**rino **S**olution (Lancia Stratos)

Institut

Institut

NIVERSITAT

-SSEN

**Pile-up**

$\boldsymbol{P}_{pile-up} = 1 - e^{(-\dot{N}_{chn} \cdot \boldsymbol{t}_{ToT})}$ short ToT to avoid pile-up:

Institut

assuming 36ns ToT (5fC ~ 1 MIP in a single strip): P(pile-up) = 0.036%@ 10kHz channel hit rate (SF=1) P(pile-up) = 0.072%@ 20kHz channel hit rate (SF=2) @ 40kHz channel hit rate (SF=4) P(pile-up) = 0.144%

assuming 60ns ToT (10fC ~ 2 MIP in a single strip): P(pile-up) = 0.06%@ 10kHz channel hit rate (SF=1) P(pile-up) = 0.12%@ 20kHz channel hit rate (SF=2) P(pile-up) = 0.24%@ 40kHz channel hit rate (SF=4)

(ToT based on device simulation from Valentino)

II. Physikalisches Institut

#### **Gießen Infrastructure**