Hardware Acceleration LAB

PANDA DAQ Summary 2022

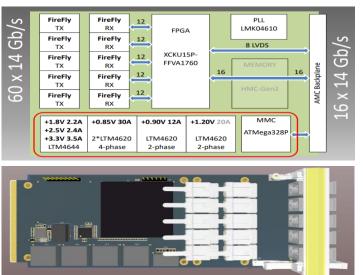

## DAQ-0

### Panda DC -Status

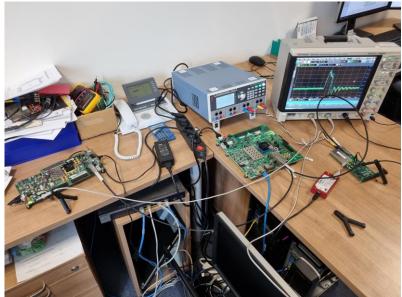

- 1. 2 boards were produced. One board is missing 0.9V The problem is faulty PCB. For furter tests of this board power this needs to be provided from an extarnal source. To be tested in future.

- 2. The second board has passed the power tests and is under tests.

- 3. The MMC works used mostly for power control

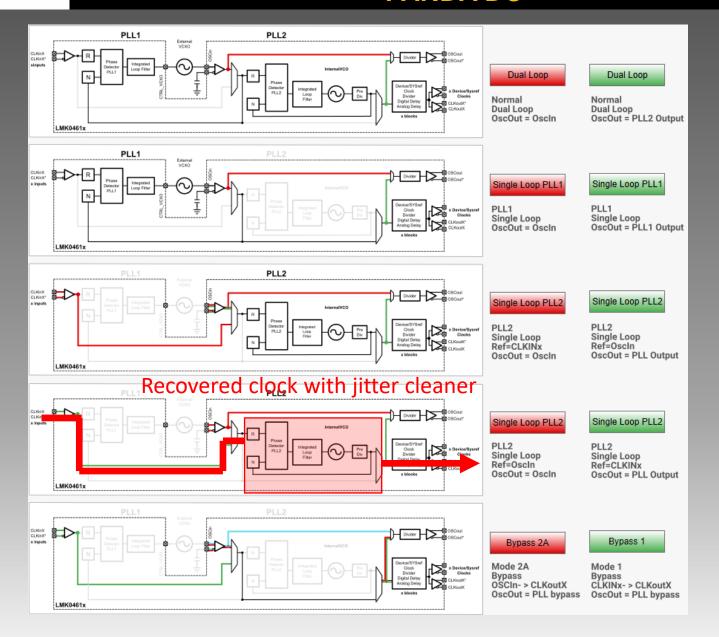

- 4. The PLL works used for providing system clocks

- 5. 8/11 GTH and 4/8 GTY transceivers work in internal loopback tests. Non-working channels be investigated. The problem is related to internal PLL (not locking).

- 6. Power consumption of GTH and GTY transceivers agrees with simulations.

- 7. Split fibers for fiber loopback tests will be delivered in 4 weeks

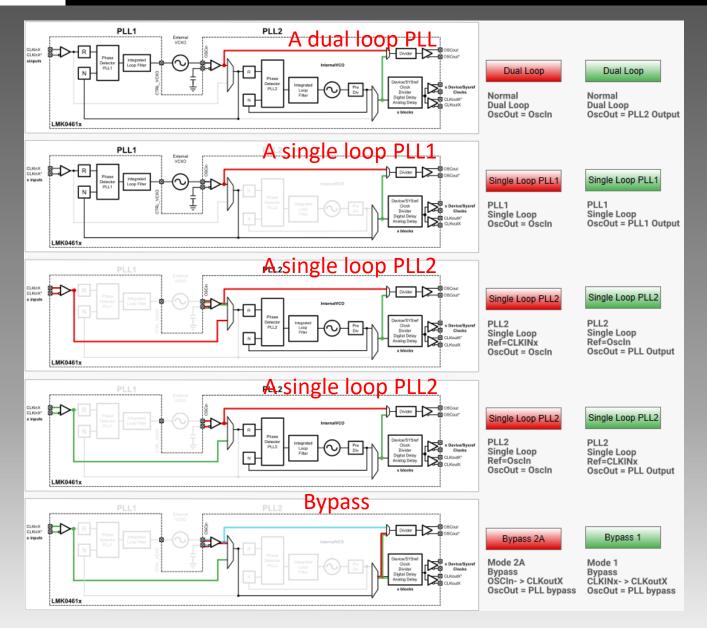

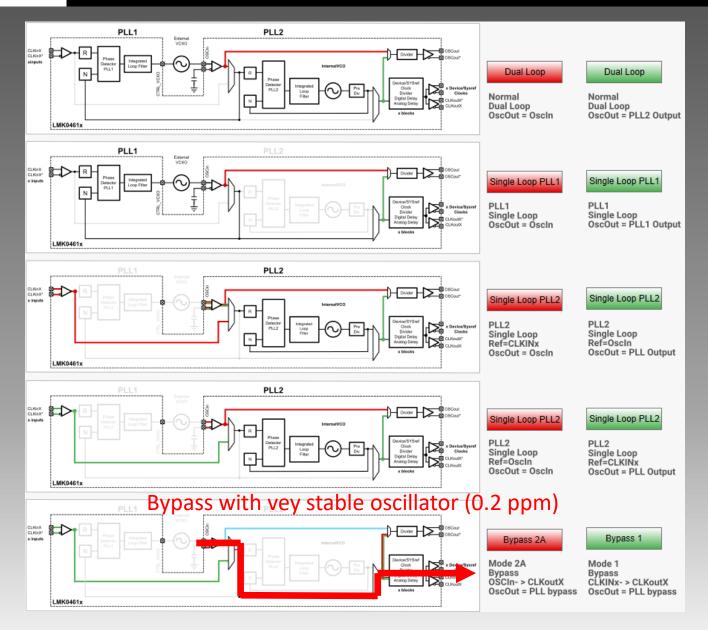

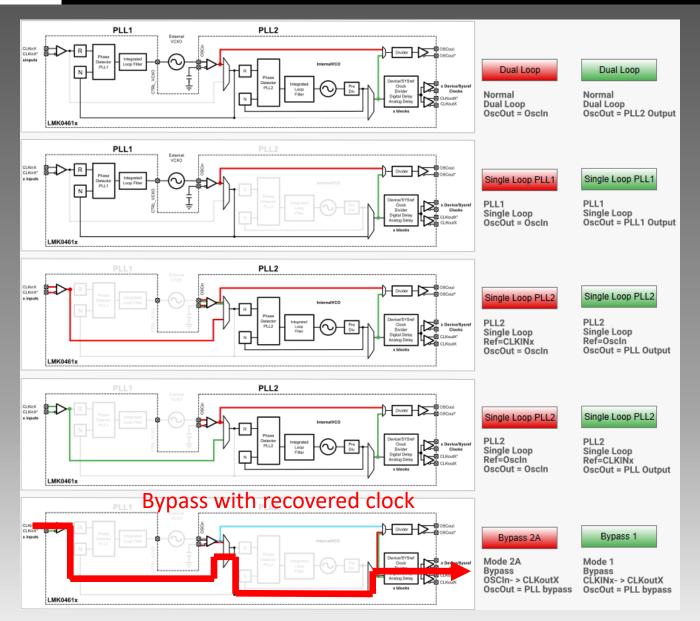

## PLL controller

- Clock supplier to Gigabit Transceivers

- SPI controlled device

- HDL SPI controller and configuration file (P. Marciniewski & M. Caselle)

- Configuration file generated by TI tools and verified on an evaluation board

- Proper reset sequence

- PLL registers configuration

- Device enable by a register at the end of the sequence

| hw_ila_1 א      |                                                      |                       |       |              |         |         |       |       |       |       |       |       |  |       | ?_D@X |       |         |       |                    |        |       |       |

|-----------------|------------------------------------------------------|-----------------------|-------|--------------|---------|---------|-------|-------|-------|-------|-------|-------|--|-------|-------|-------|---------|-------|--------------------|--------|-------|-------|

|                 | Waveform - hw_ila_1                                  |                       |       |              |         |         |       |       |       |       |       |       |  |       |       |       | ? _ @ X |       |                    |        |       |       |

| suo             | Q   <b>+</b>   <b>=</b>   <b>&amp;</b>   <b>&gt;</b> | »                     |       |              |         |         |       |       |       |       |       |       |  |       |       |       |         | ٥     |                    |        |       |       |

| shboard Options | ILA Status: Idle                                     |                       |       | 100          |         |         |       |       |       |       |       |       |  |       |       |       |         |       |                    |        |       | ^     |

| hboai           | Name                                                 | Value                 | 0     |              | 500     |         | 1,000 |       | 1,500 | 2,000 | 2,500 | 3,000 |  | 3,500 | 4,000 | 4,500 | 5,000   | 5,500 | l <sup>6,000</sup> | 6,500  | 7,000 | 7,500 |

| Das             | 🔓 spi_reset                                          | 1                     |       |              |         |         |       |       |       |       |       |       |  |       |       |       |         |       |                    |        |       |       |

|                 | 🔓 spi_miso                                           | 0                     |       |              |         |         |       |       |       |       |       |       |  |       |       |       |         |       |                    |        |       |       |

|                 | 🔓 spi_cs                                             | 0                     |       |              |         |         |       |       |       |       |       |       |  |       |       |       |         |       |                    |        |       |       |

|                 | 🔓 vio_pll_reset_1                                    | 0                     |       |              |         |         |       |       |       |       |       |       |  |       |       |       |         |       |                    |        |       |       |

|                 | 🔓 spi_sclk                                           | 0                     |       |              |         |         |       | 1 П П |       |       |       |       |  |       |       |       |         |       |                    | nhnnnn |       |       |

|                 | > 😽 rom_addr[11:0]                                   | orm_addr[11:0] 0da    |       |              |         |         |       |       | 0db   |       |       |       |  |       |       |       |         |       |                    |        |       |       |

|                 | > 😼 rom_data[23:0]                                   | rom_data[23:0] 001101 |       |              |         |         |       |       |       |       |       |       |  |       |       |       |         |       |                    |        |       |       |

|                 |                                                      |                       |       |              |         |         |       |       |       | T     |       |       |  |       |       |       |         |       |                    |        |       |       |

|                 |                                                      |                       |       |              |         |         |       |       |       |       |       |       |  |       |       |       |         |       |                    |        |       |       |

|                 |                                                      |                       |       |              |         |         |       |       |       |       |       |       |  |       |       |       |         |       |                    |        |       |       |

|                 |                                                      |                       | Up    | dated at: 20 | 22-0ct- | 05 13:1 | 8:53  |       |       |       |       |       |  |       |       |       |         |       |                    |        |       | ~     |

|                 |                                                      | < >                   | > < ( |              |         |         |       |       |       |       |       |       |  |       |       |       |         |       |                    |        |       | >     |

# Gigabit Transceivers

- Evaluation of MGT channels performance

- Automatic IBERT tester component

- First channels positively tested (P. Marciniewski)

- 5 Gbps with 100 MHz reference clock

- Loopback at PMA level

- Optical components required for external loopback

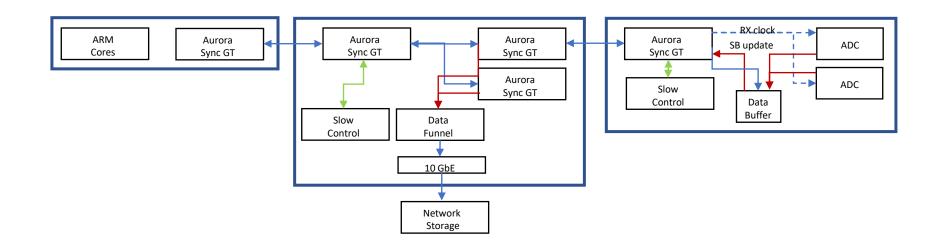

- Aurora Sync

- High-level protocol for data transport, AXI transfer, synchronization pulses

- Implemented on GTP (Artix), GTX (Kintex, ZynqU+), GTH (KintexU+)

- To be adapter to GTY

### **Transceiver loopback tests**

| 🍌 project_2 - [C:/Users/Pawel/Desktop/LMK                        | <br>K04610/project_2/project_2.xpr]                             | - Vivado 2020.1 |                |                            |                                                                                                                 |                     |            |                |                     |                         |                     |                |                                       | -              | - 🗆 X          | × 🗆 |

|------------------------------------------------------------------|-----------------------------------------------------------------|-----------------|----------------|----------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------|------------|----------------|---------------------|-------------------------|---------------------|----------------|---------------------------------------|----------------|----------------|-----|

| <u>File Edit Flow Tools Reports</u>                              | s <u>W</u> indow La <u>v</u> out <u>V</u> ie                    | ew <u>H</u> elp | Quick Access   |                            |                                                                                                                 |                     |            |                |                     |                         |                     |                |                                       | write_bitstrea | am Complete 🔦  | 1-  |

|                                                                  | th 🔅 Σ 🕺 🖉                                                      | 🖌 🔀 Da:         | shboard 👻      |                            |                                                                                                                 |                     |            |                |                     |                         |                     |                |                                       | 📰 Serial I/O   | ) Analyzer 🔍 🗸 | -   |

| Flow Navigator 😤 🔶 ? 🔔                                           | A HARDWARE MANAGER - localhostbillinx_tcf/Xilinx/00001877bc9b01 |                 |                |                            |                                                                                                                 |                     |            |                |                     |                         |                     |                |                                       |                |                | ×   |

| Open Block Design                                                | Hardware                                                        | ?               | _ 0 6 X        | Scan Plot                  | s - Scan 1                                                                                                      | × Scan Plots - Scan | 2 × Scan P | Plots - Scan 3 | × Scan Plots - Scan | 4 × Scan Plots - Scan   | 5 × Scan Plots - Sc | an 6 🗙 Scan Pl | ots - Scan 7 >                        | Scan P 4       | ▶ = ? □ □      |     |

| Generate Block Design                                            |                                                                 | ►   ≫   ■       | ٥              |                            |                                                                                                                 |                     |            |                | *                   |                         |                     |                |                                       |                |                | 17  |

| ✓ SIMULATION                                                     | Name                                                            |                 | Status         |                            |                                                                                                                 |                     |            |                |                     | Unit Interval           |                     |                |                                       |                |                |     |

| Run Simulation                                                   | ⊵⊲ MGT_X                                                        |                 | 5.000 Gbps ^   |                            | -0.5                                                                                                            | -0.4                | -0.3       | -0.2           | -0.1                | 0 0.1                   | 0.2                 | 0.3            | 0.4                                   | 0.5            | BER            |     |

|                                                                  | P⊲ MGT_X                                                        |                 | 5.000 Gbps     | <b>s</b> 10                | the second se | -0:4                | -0.3       | -0.2           | -0:1                |                         | 0.2                 | 0.5            | 0.4                                   | 0.5            |                |     |

| <ul> <li>RTL ANALYSIS</li> <li>Open Elaborated Design</li> </ul> | № MGT_X0Y19           ✓ 彎 Quad_229 (5)           ⊡ COMMON_X0Y5  |                 | 5.000 Gbps     | 9 <b>0</b> 0 5             | 0                                                                                                               |                     |            |                |                     |                         |                     |                |                                       |                |                |     |

|                                                                  | < COMM                                                          | 014_X015        | >              | -10                        |                                                                                                                 |                     |            |                |                     |                         |                     |                |                                       |                |                |     |

| SYNTHESIS                                                        |                                                                 |                 |                |                            |                                                                                                                 |                     |            |                |                     |                         |                     |                |                                       |                |                |     |

| ▶ Run Synthesis                                                  | Scan Properties                                                 | ?               | _ 🗆 🖒 ×        | Summar                     | (y                                                                                                              |                     | Metrics    |                | Settings            |                         |                     |                |                                       |                |                |     |

| > Open Synthesized Design                                        | 📕 Scan 1                                                        | +               |                | Nam                        | ie: S <sup>r</sup>                                                                                              | CAN_1               | Open area: | 17543          | Link settings:      | N/A                     |                     |                |                                       |                |                |     |

|                                                                  | Name: SCAN_1                                                    |                 | î              | Desr                       | cription: So                                                                                                    | can 1               | Open UI %: | 88.37          | Horizontal increm   | ient: 1                 |                     |                |                                       |                |                |     |

|                                                                  | Description: Scan 1                                             |                 | 8              | Start                      | .ed: 20                                                                                                         | 022-Oct-05 17:05:21 |            |                | Horizontal range:   | -0.500 UI to 0.500 UI   |                     |                |                                       |                |                |     |

| Run Implementation                                               | Status: Done                                                    |                 |                | Ende                       | ed: 2(                                                                                                          | 022-Oct-05 17:06:46 |            |                | Vertical increment  | it: 1                   |                     |                |                                       |                |                |     |

| ✓ Open Implemented Design                                        | RX: MGT_X0                                                      | 1V12/RX         | ~              | Linde                      |                                                                                                                 | 22 00 00 11:00.40   |            |                |                     |                         |                     |                |                                       |                |                |     |

| Constraints Wizard                                               | General Properties                                              | 116055.1        |                |                            |                                                                                                                 |                     |            |                | Vertical range:     | 100%                    |                     |                |                                       |                |                |     |

| Edit Timing Constraints                                          |                                                                 |                 |                |                            |                                                                                                                 |                     |            |                |                     |                         |                     |                |                                       |                |                | -1  |

| 🔯 Report Timing Summary                                          | Tcl Console Messages                                            | Serial I/O Link | s Serial I/O S | Scans ×                    |                                                                                                                 |                     |            |                |                     |                         |                     |                |                                       |                | ? _ 🗆 🖸        | 1   |

| Report Clock Networks                                            | Q   ¥   €   ▶                                                   |                 |                |                            |                                                                                                                 |                     |            |                |                     |                         |                     |                |                                       |                |                |     |

| Report Clock Interaction                                         | Name Link                                                       | Link Settings   | Reset RX       | Scan Type                  | Status                                                                                                          | Progress            | Open Area  | Open UI %      | Horz Incr           | Horz Range              | Vert Incr           | Vert Range     | Dwell                                 |                | Dwell BER      |     |

| 🖄 Report Methodology                                             | Scans (12)                                                      |                 |                |                            |                                                                                                                 |                     |            |                |                     |                         |                     |                |                                       |                |                |     |

| Report DRC                                                       | Scan 1                                                          |                 |                | 2d_full_eye                |                                                                                                                 | 100%                |            | 88.37          | 1 ~                 | 0.500 0110 0.500 01     |                     | 100%           | ✓ BER                                 |                | 1e-5           | 41  |

| Report Utilization                                               | Scan 2                                                          |                 |                | 2d_full_eye                | Done                                                                                                            | 100%                | 16384      | 82.35          | 8 ~                 | 0.000 010 0.000 01      |                     | 100%           | ✓ BER                                 |                | 1e-5           | -11 |

|                                                                  | Scan 3                                                          |                 | -              | 2d_full_eye                | Done<br>Done                                                                                                    | 100%                |            | 82.35<br>88.24 | 8 ~                 |                         |                     | 100%<br>100%   | V BER                                 |                | 1e-5<br>1e-5   | -11 |

| 📡 Report Power                                                   | Scan 4                                                          |                 |                | 2d_full_eye<br>2d_full_eye | Done                                                                                                            | 100%                |            | 88.24          | 8 ~                 |                         | -                   | 100%           | <ul><li>✓ BER</li><li>✓ BER</li></ul> |                | 1e-5<br>1e-5   | -   |

| 渚 Schematic                                                      | Scan 6                                                          |                 | _              | 2d_full_eye                |                                                                                                                 | 100%                |            | 82.35          | 8 ~                 |                         |                     | 100%           | <ul><li>✓ BER</li></ul>               |                | 1e-5           |     |

|                                                                  | Scan 7                                                          |                 |                | 2d_full_eye                | Done                                                                                                            | 100%                |            | 82.35          | 8 ~                 | 0.000 0110 0.000 01     |                     | 100%           | ✓ BER                                 |                | 1e-5           |     |

| PROGRAM AND DEBUG                                                | Scan 8                                                          |                 | _              | 2d_full_eye                | Done                                                                                                            | 100%                |            | 88.24          | 8 ~                 |                         |                     | 100%           | ✓ BER                                 |                | 1e-5           |     |

| 👫 Generate Bitstream                                             | Scan 9                                                          |                 |                | 2d_full_eye                | Done                                                                                                            | 100%                |            | 88.24          | 8 ~                 |                         |                     | 100%           | ✓ BER                                 |                | 1e-5           |     |

| ∨ Open Hardware Manager                                          | Scan 10 Found 9                                                 |                 | _              | 2d_full_eye                |                                                                                                                 | 100%                |            | 82.35          | 8 ~                 |                         |                     | 100%           | ✓ BER                                 |                | 1e-5           |     |

| Open Target                                                      | Scan 11                                                         |                 |                | 2d_full_eye                | Done                                                                                                            | 100%                | 16960      | 82.35          | 8 ~                 | -0.500 UI to 0.500 UI 🗸 | 8 ~                 | 100%           | ✓ BER                                 | ~              | 1e-5           |     |

| Program Device                                                   | Scan 12 Found 1                                                 | 1               | _              | 2d_full_eye                |                                                                                                                 | 100%                | 17216      | 82.35          | 8 ~                 | -0.500 UI to 0.500 UI 🗸 | 8 ~                 | 100%           | ✓ BER                                 |                | 1e-5           |     |

| Add Configuration Memory D                                       | <                                                               |                 |                |                            |                                                                                                                 |                     |            |                |                     |                         |                     |                |                                       |                | 3              | >   |

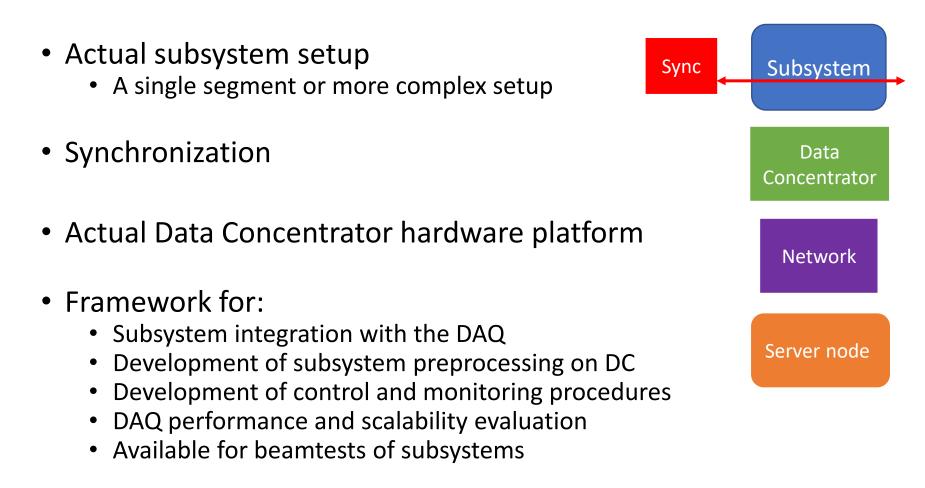

# DAQ-0 setup

#### **Controller Board**

- Common clock source

- Synchronous transc.

- Linux + master AXI

- L. Linzen works on dev. board

#### **Data Concentrator**

- Common clock recovery

- Common clock forwarding

- Endp. data aggregation

- Ethernet output

- AXI forwarding and local

### Endpoint

- Common clock recovery

- Data buffering

- Slow control

GTX endpoint tested on dev. board

### Summary

- Basic DC functionality operational

- Proceed to evaluate communication infrastructure

- Testing setup ready in Cracow

- 1 DC unit to share

- EMC SADC as Endpoint

- Tests of Aurora on GTX

- Integration with ADC readout

- 2 units produced and equipped

- 1 u. operational, 1 u. power supply under investigation

- FPGA programmable

- Module Management Controller operational

- Initial firmware (P. Marciniewski & M. Caselle)

- PLL HDL controller clock source for MGTs

- Evaluation of MGT channels

- FPGAs purchased for more units

- Firefly transceivers sets for 2 units

- Purchase required for additional 2 units

- Additional cabling for loopbacks and bundle splits ordered

0 8 N)d

#### UPPSALA UNIVERSITET

#### Status of the DAQ electronics for the EMC PANDA DC

**UPPSALA**

#### Status of the DAQ electronics for the EMC **PANDA DC**

**UPPSALA**

**UPPSALA**

#### Status of the DAQ electronics for the EMC **PANDA DC**